CDC® REMOVABLE STORAGE DRIVE

PA3A1

PA3A2

THEORY OF OPERATION

GENERAL MAINTENANCE INFORMATION

TROUBLE ANALYSIS

ELECTRICAL CHECKS

REPAIR AND REPLACEMENT

Volume 2

HARDWARE MAINTENANCE MANUAL

### **REVISION RECORD**

| REVISION        | DESCRIPTION                                                                                   |

|-----------------|-----------------------------------------------------------------------------------------------|

| 01<br>(2-16-82) | Preliminary release                                                                           |

| 02<br>(5-14-82) | Preliminary manual update                                                                     |

| 03              | Preliminary release of manual to cover Theory                                                 |

| (2-18-83)<br>04 | of Operation only. Preliminary manual update to include sections                              |

| (3-16-83)<br>A  | on maintenance. Original release documenting series code 04                                   |

| (6-14-83)       | and below units. This edition obsoletes all previous editions.                                |

| B<br>(7-26-83)  | Manual revised to incorporate series code 05 technical and editorial changes.                 |

| C (9-26-83)     | Manual revised to incorporate series code 06<br>  technical and editorial changes.            |

| D               | Manual revised to incorporate series codes 07                                                 |

| (1-25-84)<br>E  | and 08 technical and editorial changes.  Manual revised to incorporate series code 09         |

| (08-09-84)      | technical and editorial changes. This edition of the control obsoletes all previous editions. |

| F<br>(05-08-85) | Manual revised to incorporate series codes 10<br>  thru 14 technical and editorial changes.   |

| G<br>(10-15-85) | Manual revised to incorporate class 1 ECOs for series code 16: DJ03811; series code 18:       |

| <b>,</b>        | DJ03769; class 2 ECOs DJ03814, DJ03787, DJ850305 and technical and editorial changes.         |

|                 | and coomitour and cartorrar changes.                                                          |

|                 |                                                                                               |

|                 |                                                                                               |

|                 |                                                                                               |

|                 | ·<br>                                                                                         |

|                 |                                                                                               |

REVISION LETTERS I, O, Q AND X ARE NOT USED.

© 1982, 1983, 1984, 1985 By Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation

Twin Cities Disk Division

Customer Documentation Dept.

5950 Clearwater Drive

Minnetonka, MN 55343

or use Comment Sheet in the back

of this manual.

### LIST OF EFFECTIVE PAGES

#### Sheet 1 of 6

New features, as well as changes, deletions, and additions to information in this manual are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE     | REV | PAGE | REV |

|----------|-----|------|-----|

| Cover    |     | 1-1  | G   |

| Warnings |     | 1-2  | G   |

| Title P  | -   | 1-3  | F   |

| ii       | G   | 1-4  | A   |

| iii      | G   | 1-5  | A   |

| iv       | G   | 1-6  | A   |

| v        | G ` | 1-7  | A   |

| vi       | G   | 1-8  | A   |

| vii      | G   | 1-9  | Α   |

| viii     | G   | 1-10 | A   |

| ix       | A   | 1-11 | E   |

| x        | F   | 1-12 | F   |

| хi       | F   | 1-13 | A   |

| хii      | E   | 1-14 | A   |

| xiii     | G   | 1-15 | В   |

| xiv      | G   | 1-16 | A   |

| xv       | G   | 1-17 | A   |

| xvi      | G   | 1-18 | A   |

| xvii     | G   | 1-19 | E   |

| xviii    | G   | 1-20 | С   |

| xix      | G   | 1-21 | A   |

| XX       | E   | 1-22 | F   |

| xxi      | G   | 1-23 | A   |

| xxii     | G   | 1-24 | A   |

| xxiii    | G   | 1-25 | · A |

| xxiv     | G   | 1-26 | A   |

| XXV      | F   | 1-27 | · A |

| Blank    |     | 1-28 | D   |

| xxvii    | F   | 1-29 | A   |

| xxviii   | G   | 1-30 | A   |

| xxix     | G   | 1-31 | A   |

| XXX      | F   | 1-32 | D   |

| S-1 Div  | _   | 1-33 | A   |

| Blank    | -   | 1-34 | A   |

83324490 G

Sheet 2 of 6

| PAGE         | <u>REV</u>                      | PAGE         | REV        |

|--------------|---------------------------------|--------------|------------|

| -            |                                 | <del></del>  |            |

| 1-35         | A                               | 1-76         | E          |

| 1-36         | E                               | 1-77         | E          |

| 1-37         | A                               | 1-78         | E          |

| 1-38         | A                               | 1-79         | A          |

| 1-39         | A                               | 1-80         | A          |

| 1-40         | A                               | 1-81         | A          |

| 1-41         | Α                               | 1-82         | D          |

| 1-42         | A                               | 1-83         | E          |

| 1-43         | A                               | 1-84         | E          |

| 1-44         | · A                             | 1-85         | E          |

| 1-45         | A                               | 1-86         | E          |

| 1-46         | A                               | 1-87         | A          |

| 1-47<br>1-48 | A                               | 1-88         | E          |

| 1-48         | A                               | 1-89         | E          |

| 1-50         | A                               | 1-90         | A          |

| 1-50         | A<br>A                          | 1-91         | A          |

| 1-52         | A                               | 1-92         | E          |

| 1-53         | E                               | 1-93         | E          |

| 1-54         | A                               | 1-94<br>1-95 | E A        |

| 1-55         | Ä                               | 1-96         | E<br>A     |

| 1-56         | Ä                               | 1-97         | E          |

| 1-57         | Ä                               | 1-98         | E          |

| 1-58         | A                               | 1-99         | E          |

| 1-59         | A                               | 1-100        | E          |

| 1-60         | <b>A</b> :                      | 1-101        | Ē          |

| 1-61         | <b>B</b> .                      | 1-102        | Ē          |

| 1-62         | A                               | 1-103        | Ē          |

| 1-63         | A                               | 1-104        | E          |

| 1-64         | В                               | 1-105        | E          |

| 1-65         | A                               | 1-106        | E          |

| 1-66         | Α                               | 1-107        | <b>E</b> ' |

| 1-67         | A                               | 1-108        | E          |

| 1-68         | A                               | 1-109        | <b>E</b> ? |

| 1-69         | E                               | 1-110        | E          |

| 1-70         | E                               | 1-111        | G          |

| 1-71         | $\mathbf{G}^{N_{\mathrm{obs}}}$ | 1-112        | G          |

| 1-72         | A                               | 1-113        | G          |

| 1-73         | $\mathbf{E}$                    | 1-114        | A          |

| 1-74         | E                               | 1-115        | A          |

| 1-75         | E                               | 1-116        | A          |

|              |                                 |              | **         |

Sheet 3 of 6

| PAGE    | REV | PAGE             | REV |

|---------|-----|------------------|-----|

| 1-117   | G   | 2-12             | G   |

| 1-118   | A   | 2-13             | G   |

| 1-119   | G   | 2-14             | G   |

| 1-120   | G   | 2-15             | G   |

| 1-121   | E   | 2-16             | F   |

| 1-122   | A   | 2-17             | F   |

| 1-123   | G   | 2-18             | G   |

| 1-124   | G   | 2-19             | G   |

| 1-125   | G   | 2-20             | G   |

| 1-126   | G   | 2-21             | G   |

| 1-127   | G   | 2-22             | G   |

| 1-128   | G   | 2-23             | G   |

| 1-129   | G   | 2-24             | G G |

| 1-130   | G   | 2-25             | G   |

| 1-131   | G   | 2-26             | G   |

| 1-132   | G   | 2-27             | G   |

| 1-133   | G   | Blank            |     |

| 1-134   | G   | S-3 Div          |     |

| 1-135   | G   | Blank            |     |

| 1-136   | G   | 3-1              | E   |

| 1-137   | G   | 3-2              | E   |

| 1-138   | G   | 3-3              | E   |

| 1-139   | G   | 3-4              | E   |

| 1-140   | G   | 3-5              | G   |

| 1-141   | G   | 3-6              | G   |

| 1-142   | G   | 3-7              | G   |

| 1-143   | G   | 3-8              | G   |

| 1-144   | G   | 3-8.1            | G   |

| S-2 Div | _   | Blank            | _   |

| Blank   | -   | 3-9              | G   |

| 2-1     | G   | 3-10             | G   |

| 2-2     | G   | 3-11             | G   |

| 2-3     | F   | 3-12             | G   |

| 2-4     | G   | 3-13             | G   |

| 2-5     | G   | 3-14             | E   |

| 2-6     | F   | 3-15             | G   |

| 2-7     | F   | 3-16             | G   |

| 2-8     | F   | 3-17             | G   |

| 2-9     | F   | 3-18             | G   |

| 2-10    | G   | 3-19             | G   |

| 2-11    | G   | 3-20             | G   |

|         |     | - <del>-</del> - |     |

Sheet 4 of 6

| PAGE | REV | PAGE    | REV        |

|------|-----|---------|------------|

| 3-21 | G   | 3-62    | E          |

| 3-22 | G   | 3-63    | A          |

| 3-23 | G   | 3-64    | D          |

| 3-24 | G   | 3-65    | A          |

| 3-25 | G   | 3-66    | E          |

| 3-26 | G   | 3-67    | A          |

| 3-27 | A   | 3-68    | A          |

| 3-28 | A   | 3-69    | A          |

| 3-29 | A   | 3-70    | A          |

| 3-30 | A   | 3-71    | A          |

| 3-31 | E   | 3-72    | E          |

| 3-32 | E   | 3-73    | A          |

| 3-33 | E   | 3-74    | E          |

| 3-34 | D · | 3-75    | E          |

| 3-35 | E   | 3-76    | A          |

| 3-36 | E   | 3-77    | E          |

| 3-37 | D   | 3-78    | A          |

| 3-38 | A   | 3-79    | E          |

| 3-39 | E   | 3-80    | A          |

| 3-40 | A   | 3-81    | A          |

| 3-41 | A   | 3-82    | G          |

| 3-42 | E   | 3-83    | <b>A</b> . |

| 3-43 | A   | 3-84    | E          |

| 3-44 | A   | 3-85    | E          |

| 3-45 | E   | 3-86    | E          |

| 3-46 | A   | 3-87    | E          |

| 3-47 | A   | 3-88    | E          |

| 3-48 | A   | 3-89    | A          |

| 3-49 | A   | 3-90    | E          |

| 3-50 | A   | 3-91    | A          |

| 3-51 | D   | 3-92    | E          |

| 3-52 | D   | 3-93    | Α          |

| 3-53 | E   | Blank   | -          |

| 3-54 | E   | S-4 Div | _          |

| 3-55 | A   | Blank   | <br>D      |

| 3-56 | A   | 4-1     | В          |

| 3-57 | E   | Blank   | _          |

| 3-58 | E   | 4-3     | G          |

| 3-59 | E   | 4-4     | G          |

| 3-60 | A   | 4-5     | G          |

| 3-61 | A   | 4-6     | G          |

Sheet 5 of 6

| PAGE    | REV          | PAGE  | REV        |

|---------|--------------|-------|------------|

| 4-7     | G .          | Blank | -          |

| 4-8     | G            | 5-7   | G          |

| 4-9     | G            | 5-8   | G          |

| 4-10    | G            | 5-9   | G          |

| 4-11    | G            | 5-10  | G          |

| 4-12    | G            | 5-11  | G.         |

| 4-13    | : <b>G</b>   | 5-12  | G          |

| Blank   | *            | 5-13  | G          |

| 4-15    | G            | 5-14  | G          |

| 4-16    | G            | 5-15  | G          |

| 4-17    | G            | 5-16  | G          |

| 4-18    | G            | 5-17  | G          |

| 4-19    | G            | 5-18  | G          |

| 4-20    | G            | 5-19  | G          |

| 4-21    | G            | 5-20  | G          |

| 4-22    | G            | 5-21  | G          |

| 4-23    | G            | Blank | _          |

| 4-24    | G            | 5-23  | G          |

| 4-25    | G ,          | 5-24  | G          |

| Blank   | ·            | 5-25  | G          |

| 4-27    | G            | Blank |            |

| 4-28    | G            | 5-27  | G          |

| 4-29    | G            | 5-28  | G          |

| 4-30    | G            | 5-29  | G          |

| 4-31    | G            | Blank | · —        |

| 4-32    | G            | 5-31  | · <b>G</b> |

| 4-33    | G            | 5-32  | G          |

| 4-34    | G            | 5-33  | G          |

| 4-35    | G            | 5-34  | G          |

| Blank   | -            | 5-35  | G          |

| 4-37    | G            | 5-36  | G          |

| 4-38    | G            | 5-37  | G          |

| 4-39    | G            | 5-38  | G          |

| 4-40    | G            | 5-39  | G          |

| S-5 Div | - ·          | 5-40  | G          |

| Blank   | <del>-</del> | 5-41  | G          |

| 5-1     | E            | 5-42  | G          |

| 5-2     | G .          | 5-43  | G          |

| 5-3     | G            | 5-44  | G          |

| 5-4     | G            | 5-45  | G          |

| 5-5     | G            | Blank | -          |

Sheet 6 of 6

| PAGE  | REV   | PAGE    | REV        |

|-------|-------|---------|------------|

| 5-47  | G     | Blank   | _          |

| 5-48  | G     | 5-77    | G          |

| 5-49  | G     | 5-78    | G          |

| 5-50  | G     | 5-79    | G          |

| 5-51  | G     | 5-80    | G          |

| 5-52  | G     | 5-81    | G          |

| 5-53  | G     | 5-82    | G          |

| 5-54  | G '   | 5-83    | G          |

| 5-55  | G     | 5-84    | G          |

| 5-56  | G     | 5-85    | G `        |

| 5-57  | G     | 5-86    | . <b>G</b> |

| 5-58  | G     | 5-87    | G          |

| 5-59  | G     | 5-88    | G          |

| 5-60  | G     | 5-89    | G          |

| 5-61  | G     | 5-90    | G          |

| 5-62  | G     | 5-91    | G          |

| 5-63  | G     | 5-92    | G          |

| 5-64  | G     | 5-93    | G          |

| 5-65  | G     | 5-94    | G          |

| Blank | • = " | 5-95    | G          |

| 5-67  | G     | 5-96    | G          |

| 5-68  | G     | 5-97    | G          |

| 5-69  | G     | 5-98    | G          |

| 5-70  | G     | 5-99    | G          |

| 5-71  | G     | Blank   | -          |

| Blank | -     | Cmt Sht | -          |

| 5-73  | G     | Rtn Env | _ `        |

| 5-74  | G     | Blank   | -          |

| 5-75  | G     | Cover   |            |

|       |       |         |            |

### **PREFACE**

This manual contains maintenance information for the CONTROL DATA® PA3A1 and PA3A2 Removable Storage Drives (RSDs). It is prepared for customer engineers and other technical personnel directly involved with maintaining the RSD.

The information in this manual is presented as follows:

- Section 1 Theory of Operation. Describes power functions, electromechanical functions, interface, unit selection, servo surface decoding, sector detection, seek functions, head selection, read/write functions, and fault detection.

- Section 2 General Maintenance Information. Contains information on warnings and precautions, maintenance tools and materials, testing the drive, and accessing the drive for maintenance.

- Section 3 Trouble Analysis. Contains procedures and information to assist in troubleshooting the drive.

- Section 4 Electrical Checks. Provides electrical test procedures.

- Section 5 Repair and Replacement. Contains procedures and information on the replacement and adjustment of drive assemblies.

The following manuals apply to the RSD and are available from Control Data Corporation, Literature Distribution Services, 308 North Dale Street, St. Paul, MN 55103:

#### Publication No.

#### <u>Title</u>

83324480

PA3Al and PA3A2 Hardware Maintenance Manual, Volume 1 (contains general description, operation, installation and checkout information, and parts data)

(Continued on Next Page)

ix

| Publication No. | <u>Title</u>                                                                                                    |

|-----------------|-----------------------------------------------------------------------------------------------------------------|

| 83324490        | PA3Al and PA3A2 Hardware Maintenance Manual, Volume 2 (contains theory of operation and maintenance)            |

| 83324630        | PA3Al and PA3A2 Hardware Maintenance Man-<br>ual, Volume 3 (contains diagrams)                                  |

| 83325320        | A Guide for the Disk Drive Operator                                                                             |

| 83325360        | Reference Card (provides status code and diagnostics information)                                               |

| 83325440        | RSD/FSD Power Supply Diagrams Manual (contains power supply diagrams which are intended for reference use only) |

| 83322440        | CDC Microcircuits, Volume 1 (provides functional descriptions for integrated circuits)                          |

| 83324440        | CDC Microcircuits, Volume 2 (provides functional descriptions for integrated circuits)                          |

### **CONTENTS**

| Important Safety Information and Precautions | vxv   |

|----------------------------------------------|-------|

| Abbreviations                                | xxvii |

| 1 MURODY OF OPERATION                        |       |

| 1. THEORY OF OPERATION                       |       |

| Introduction                                 | 1-1   |

| Power Functions                              | 1-3   |

| General                                      | 1-3   |

| Power Distribution                           | 1-3   |

| Local/Remote Power Sequencing                | 1-4   |

| Power On Sequence                            | 1-4   |

| Power Off Sequence                           | 1-8   |

| Electromechanical Functions                  | 1-9   |

| General                                      | 1-9   |

| Disk Rotation                                | 1-9   |

| General                                      | 1-9   |

| Mechanical Description                       | 1-9   |

| Pack and Spindle Linkage                     | 1-9   |

| Drive Motor                                  | 1-10  |

| Electrical Description                       | 1-10  |

| General                                      | 1-10  |

| Motor Speed Control                          | 1-10  |

| Dynamic Motor Braking                        | 1-12  |

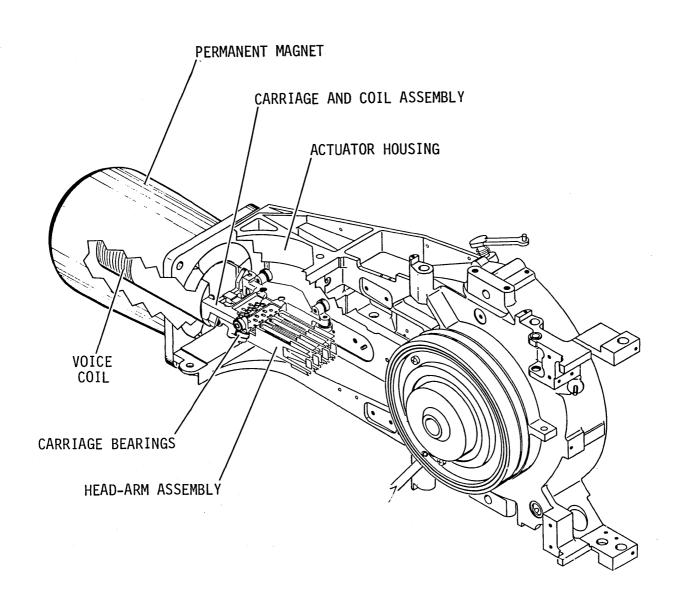

| Head Positioning                             | 1-15  |

| General                                      | 1-15  |

| Actuator and Magnet Physical Description     | 1-15  |

|                                              | 1-17  |

| Actuator and Magnet Functional Description   |       |

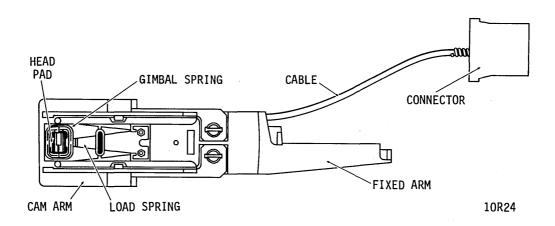

| Heads                                        | 1-17  |

83324490 F xi

| General                          | 1-17 |

|----------------------------------|------|

| Head-Arm Assembly                | 1-18 |

| Head Loading                     | 1-18 |

| Air Flow System                  | 1-19 |

| Interface                        | 1-19 |

| General                          | 1-19 |

| I/O Cables                       | 1-20 |

| I/O Signal Processing            | 1-30 |

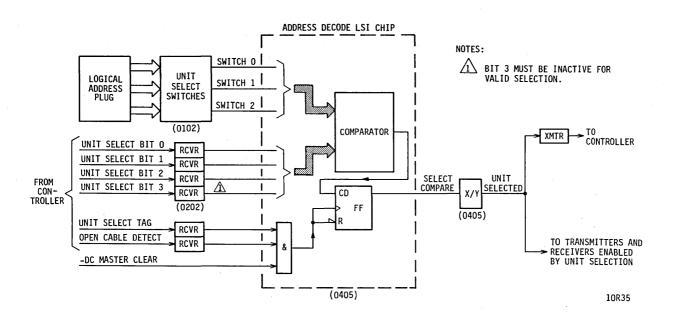

| Unit Selection                   | 1-33 |

| General                          | 1-33 |

| Single Channel Unit Selection    | 1-33 |

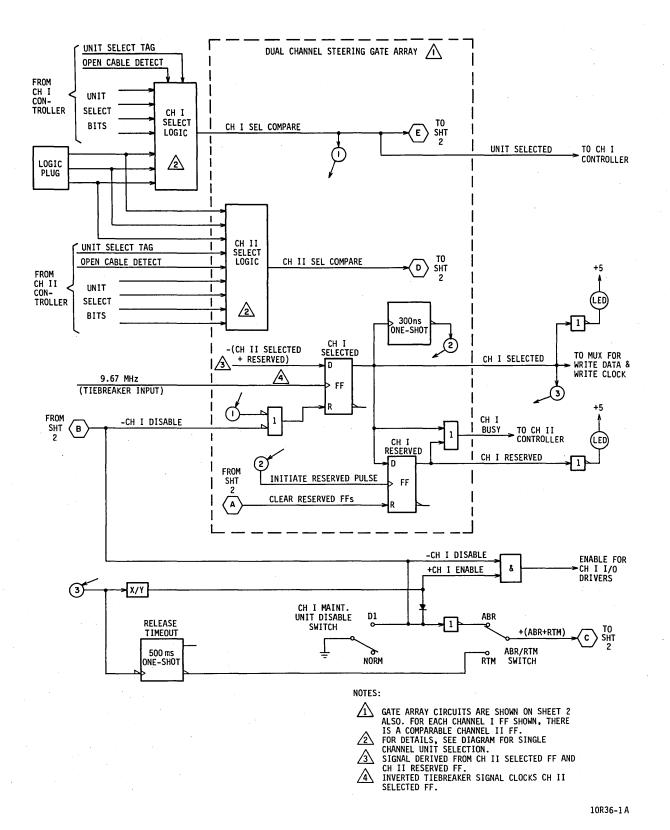

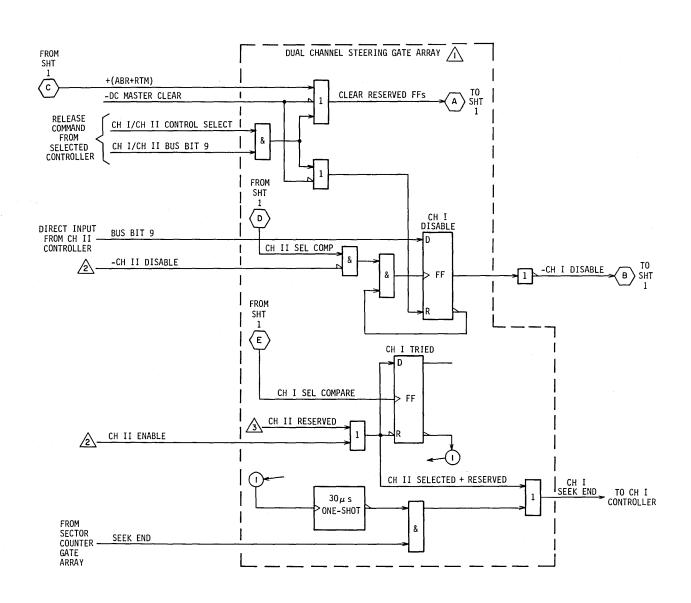

| Dual Channel Unit Selection      | 1-34 |

| General                          | 1-34 |

| Select and Reserve Function      | 1-35 |

| Release Function                 | 1-42 |

| Priority Select Function         | 1-43 |

| Maintenance Disable Function     | 1-44 |

| Drive Servo System               | 1-44 |

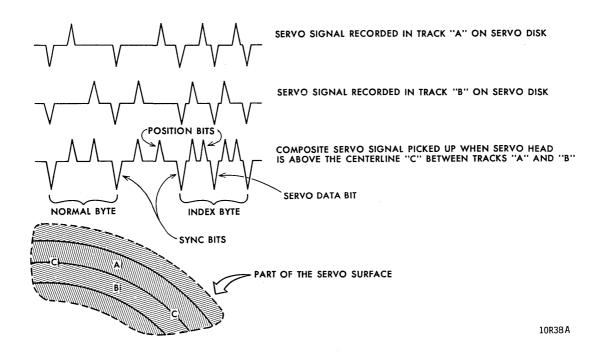

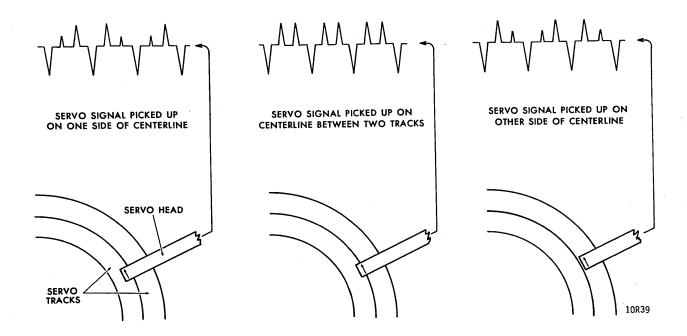

| Servo Surface Decoding           | 1-45 |

| General                          | 1-45 |

| Tribit Recording Scheme          | 1-46 |

| Servo Surface Format             | 1-47 |

| Tribit Decoder Circuit Operation | 1-50 |

| General                          | 1-50 |

| System Overview                  | 1-50 |

| Position Demodulation            | 1-51 |

| Tribit Decoder PLO               | 1-53 |

| Index and Guard Band Decoding    | 1-56 |

| Sector Detection                 | 1-59 |

| Seek Functions                   | 1-61 |

| General                          | 1-61 |

| System Overview                  | 1-61 |

| Servo Circuit Functions       | 1-64  |

|-------------------------------|-------|

| General                       | 1-64  |

| Coarse Loop Operation         | 1-64  |

| General                       | 1-64  |

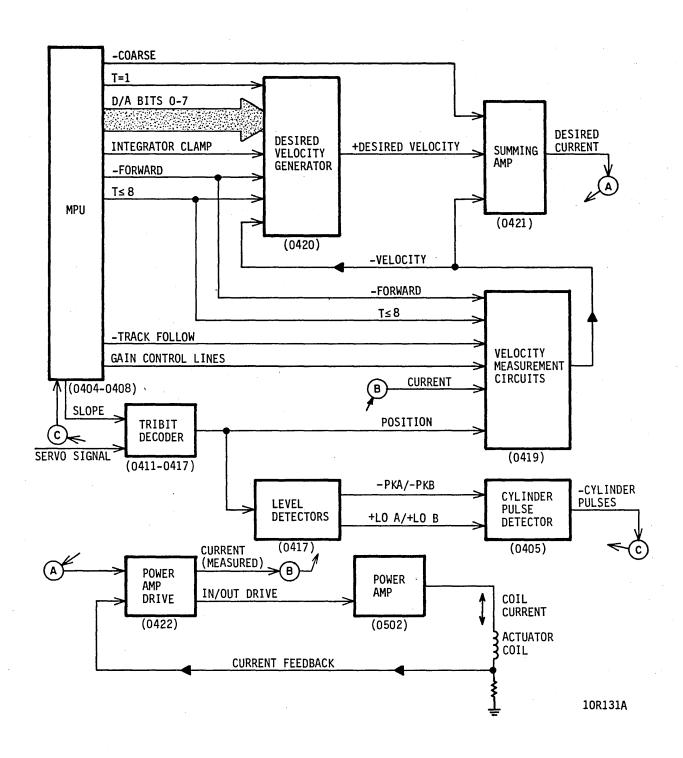

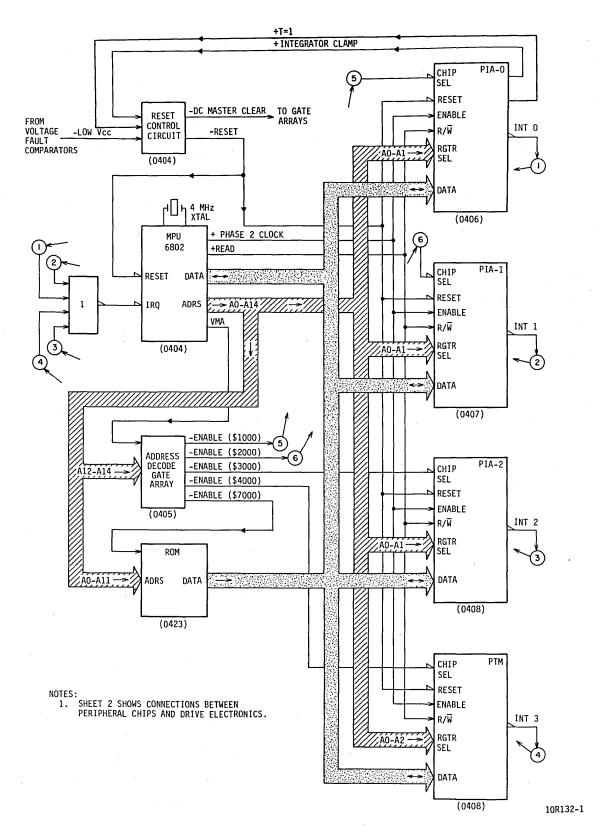

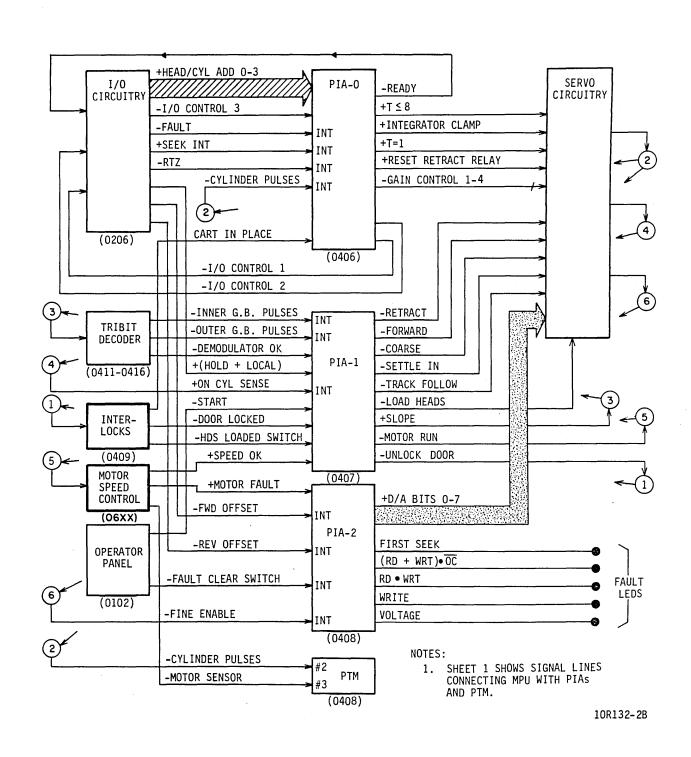

| Microprocessor Control System | 1-65  |

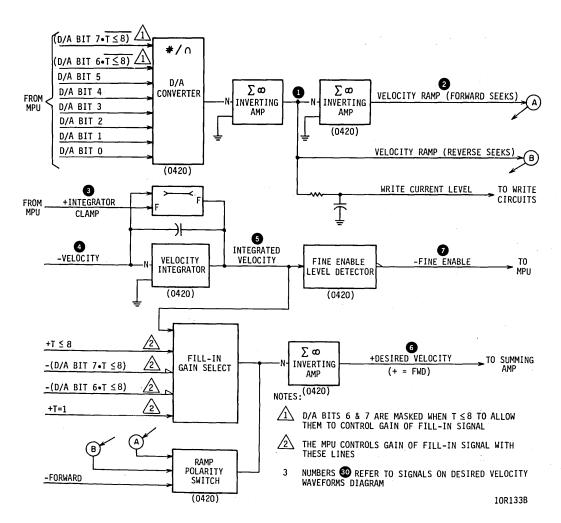

| Desired Velocity Generation   | 1-67  |

| Cylinder Pulse Detection      | 1-71  |

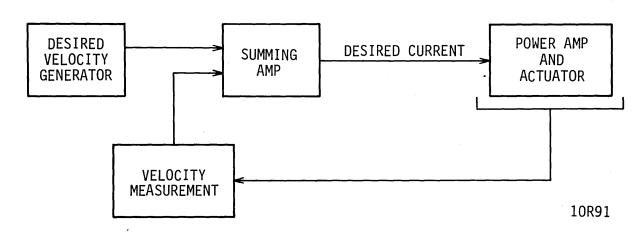

| Velocity Measurement          | 1-74  |

| Summing Amp                   | 1-77  |

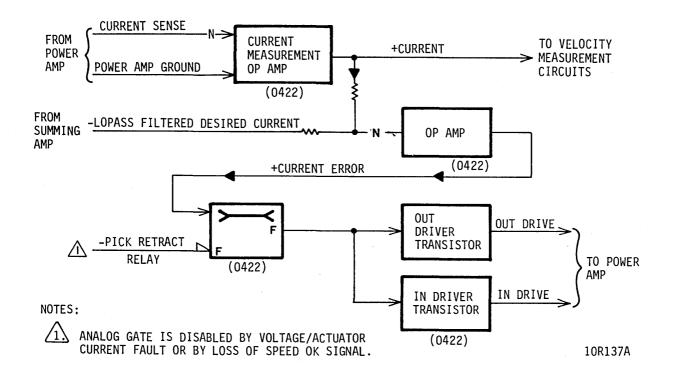

| Power Amp Drive               | 1-77  |

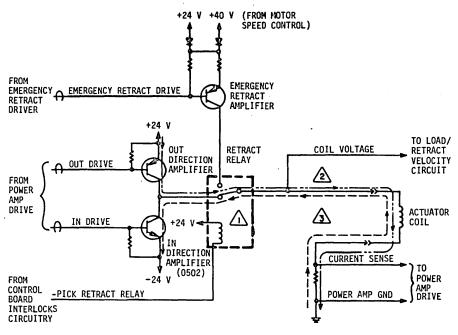

| Power Amp                     | 1-79  |

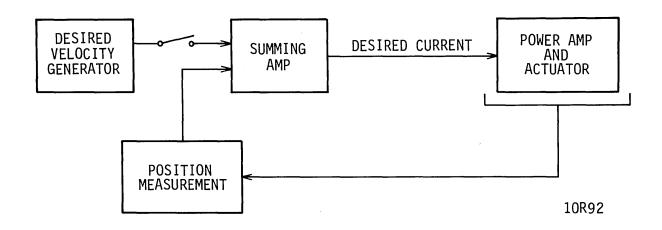

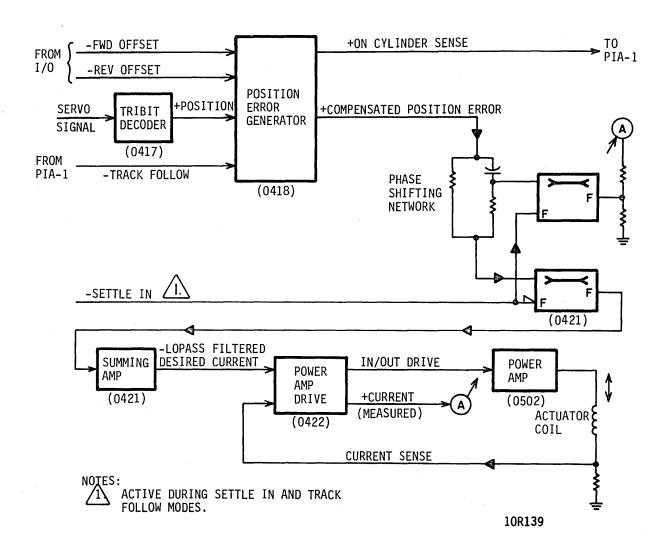

| Fine Loop Operation           | 1-80  |

| General                       | 1-80  |

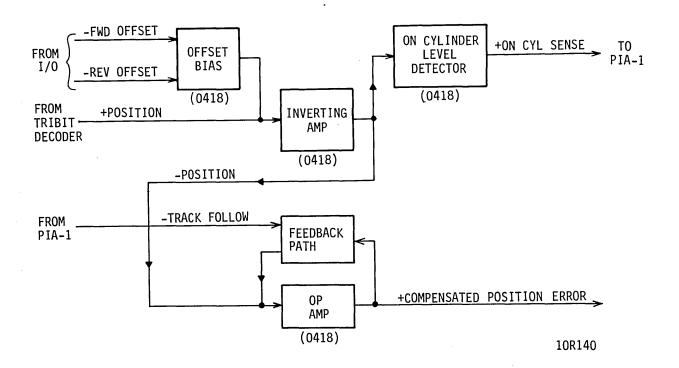

| Position Error Generation     | 1-80  |

| Fine Loop Actuator Movement   | 1-83  |

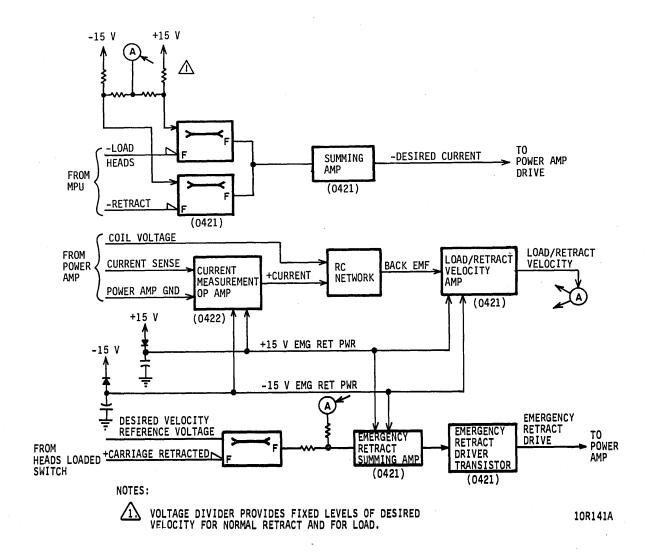

| Load/Retract Servo Loops      | 1-84  |

| Types of Seeks                | 1-86  |

| General                       | 1-86  |

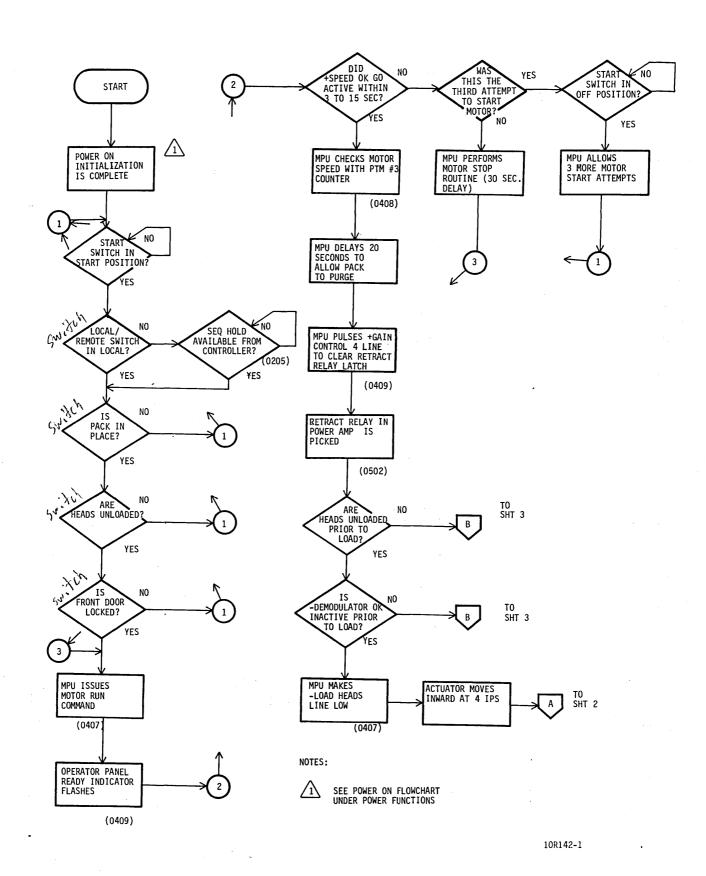

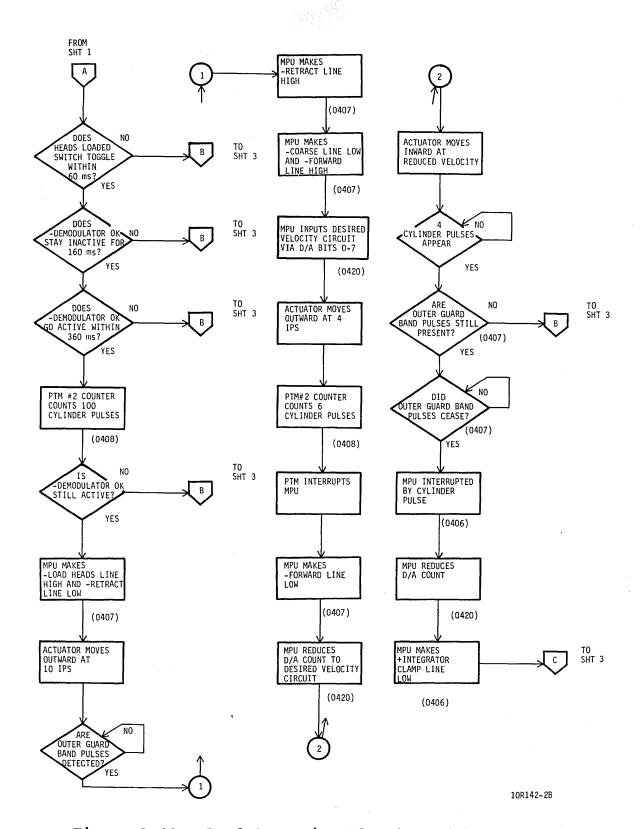

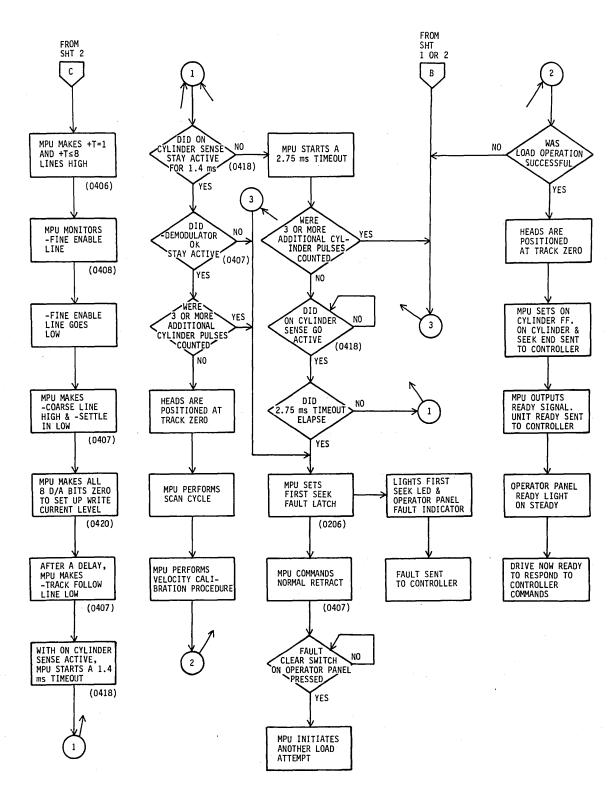

| Load Operation                | 1-86  |

| Normal Seek                   | 1-93  |

| Return to Zero Seek           | 1-10  |

| Retract Operations            | 1-109 |

| General                       | 1-109 |

| Normal Retract Operations     | 1-109 |

| Emergency Retract Operations  | 1-106 |

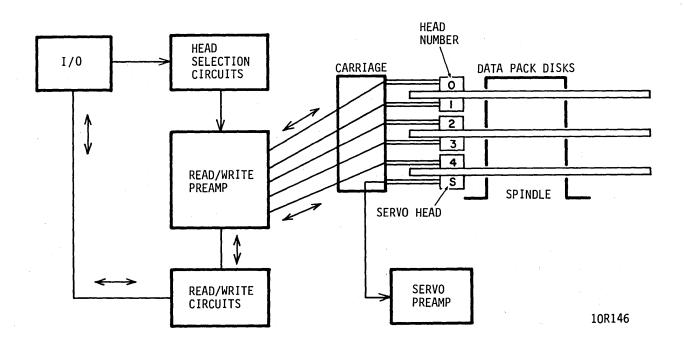

| Head Operation and Selection  | 1-107 |

| General                       | 1-107 |

| Head Functional Description   | 1-107 |

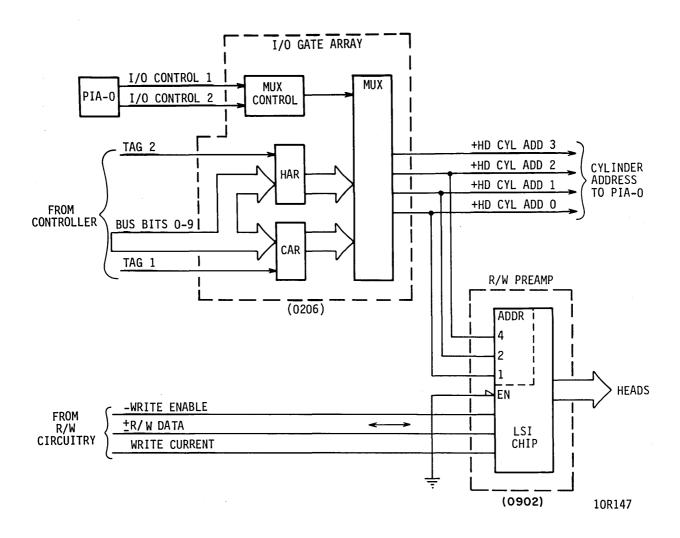

| Head Selection                | 1-109 |

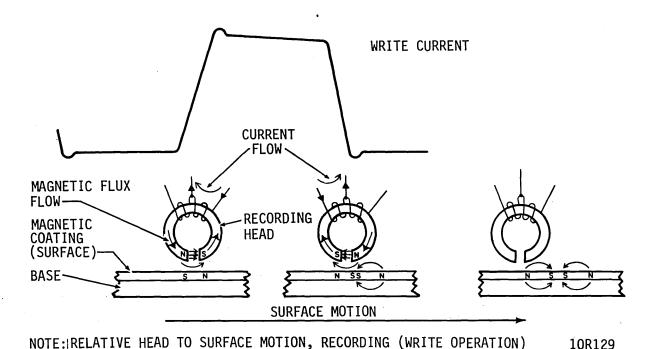

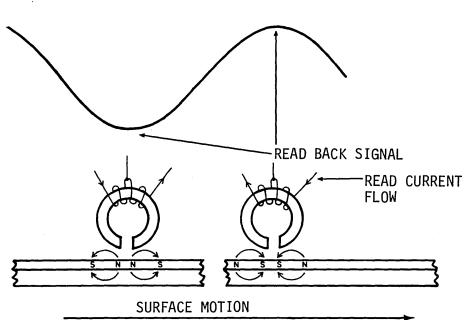

| Read/Write Functions          | 1-111 |

| General                       | 1-111 |

| Rasic Read/Write Principles   | 1 110 |

83324490 G

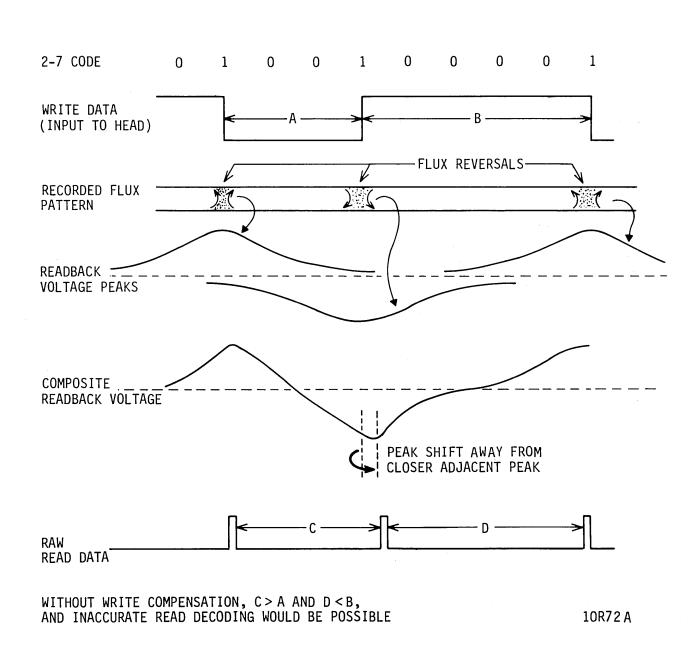

| Principles of 2-7 Recording          | 1-113  |

|--------------------------------------|--------|

| Peak Shift                           | 1-114  |

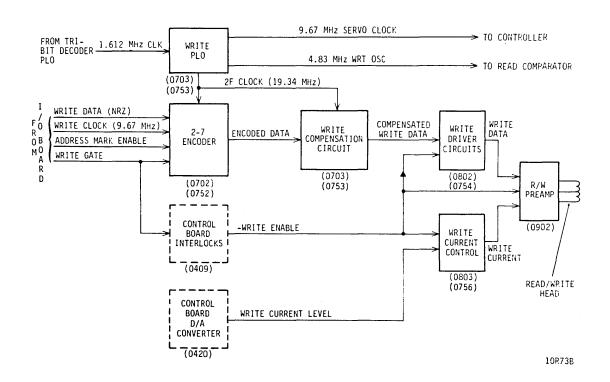

| Write Circuits                       | 1-116  |

| General                              | 1-116  |

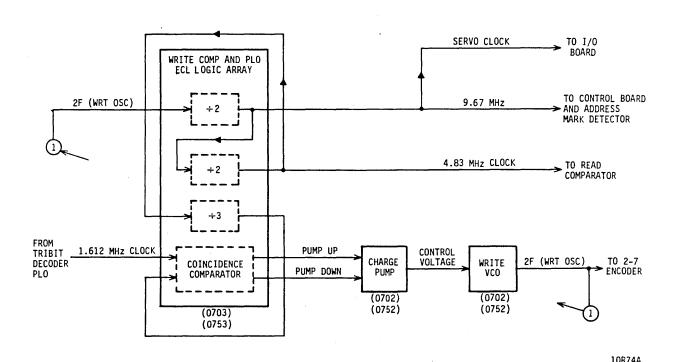

| Write PLO                            | 1-116  |

| 2-7 Encoder                          | 1-119  |

| Write Compensation Circuit           | 1-121  |

| Write Driver Circuit                 | 1-123  |

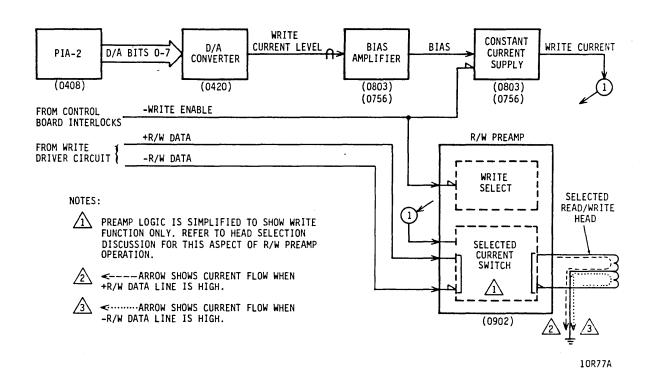

| Write Current Control                | 1-124  |

| R/W Preamp                           | 1-124  |

| Read Circuits                        | 1-125  |

| General                              | 1-125  |

| R/W Preamp                           | 1-126  |

| Data Latch Circuit                   | 1-127  |

| Data Latch Circuit (One Board R/W)   | 1-128  |

| Data Latch Circuit (Two Board R/W)   | 1-129  |

| Read Comparator and PLO              | 1-132  |

| 2-7 Decoder                          | 1-134  |

| Address Mark Detection               | 1-136  |

| Fault and Error Conditions           | 1-137  |

| General                              | 1-137  |

| Errors Indicated by Fault Signal     | 1-137  |

| General                              | 1-137  |

| Voltage or Actuator Current Fault    | 1-139  |

| Read or Write and Off Cylinder       | 1-140  |

| Write Fault                          | 1-140  |

| Read and Write Fault                 | 1-141  |

| First Seek Fault                     | 1-141  |

| Errors not Indicated by Fault Signal | 1-142  |

| General                              | 1-142  |

| Motor Speed Error                    | 1-142  |

| Sook Error                           | 1_1/13 |

| 2. GENERAL MAINTENANCE INFORMATION              |      |

|-------------------------------------------------|------|

| Introduction                                    | 2-1  |

| Warnings and Precautions                        | 2-1  |

| Electrostatic Discharge Protection              | 2-3  |

| Maintenance Tools and Materials                 | 2-6  |

| General                                         | 2-6  |

| Testing the Drive                               | 2-6  |

| General                                         | 2-6  |

| Field Test Unit                                 | 2-6  |

| Connecting FTU To Drive I/O Plate               | 2-7  |

| Connecting FTU To Drive I/O Board               | 2-7  |

| System Software                                 | 2-8  |

| Data Packs                                      | 2-8  |

| Data Pack Installation-Removal                  | 2-8  |

| Identifying Test Points                         | 2-8  |

| Accessing Assemblies for Maintenance            | 2-9  |

| Accessing Deck Assembly Parts                   | 2-19 |

| 2101 - Main Logic - Maintenance/Normal Position | 2-19 |

| Maintenance Position                            | 2-19 |

| Normal Operating Position                       | 2-21 |

| 2102 - Main Logic - Removal/Replacement         | 2-21 |

| Removal                                         | 2-23 |

| Replacement                                     | 2-25 |

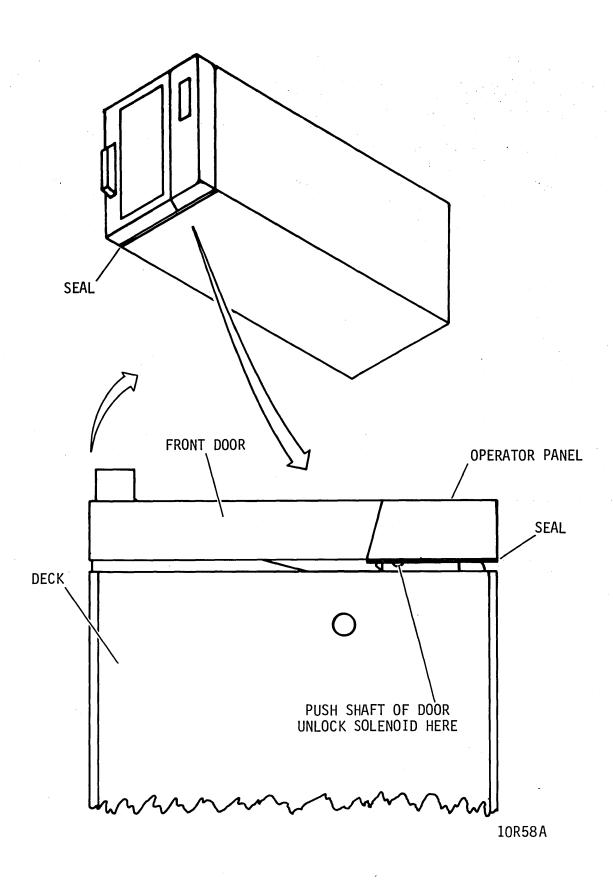

| 2103 - Overriding Front Door Interlock          | 2-26 |

| 3. TROUBLE ANALYSIS                             |      |

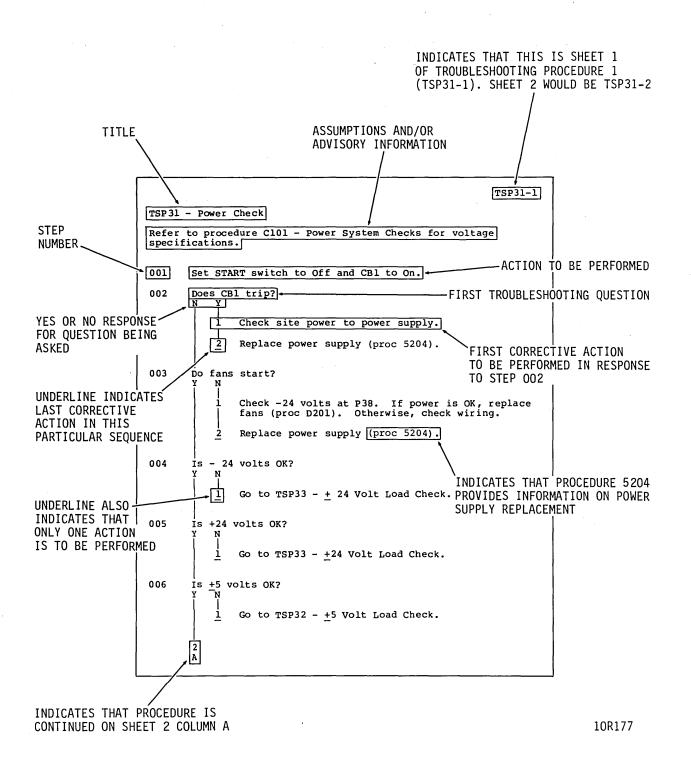

| Introduction                                    | 3-1  |

| Froubleshooting Procedures                      | 3-2  |

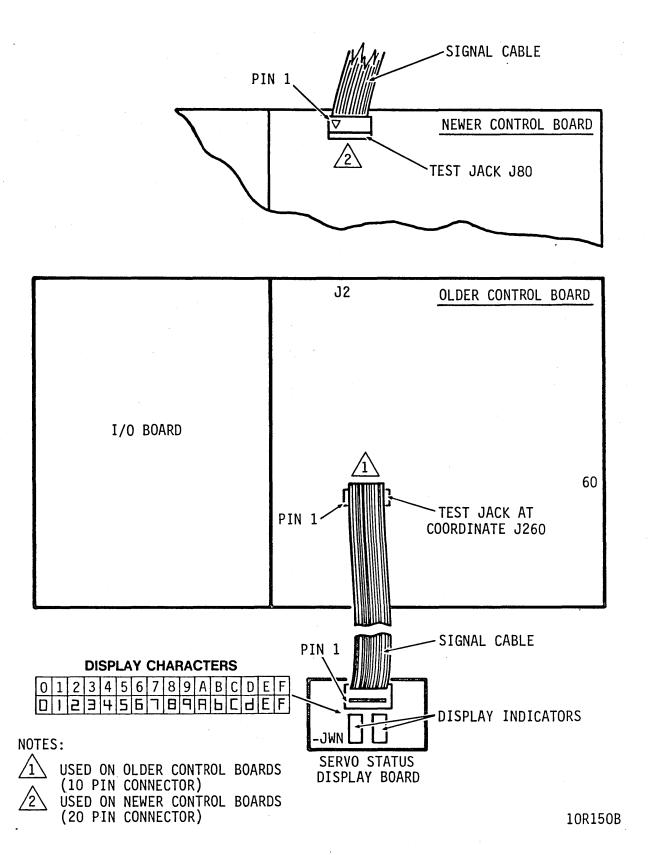

| Servo Status Codes                              | 3-25 |

| General                                         | 3-25 |

| Installing the Servo Status Display Card (_JWN) | 3-25 |

| Servo Status Code Definitions                   | 3-25 |

83324490 G xv

| 4. ELECTRICAL CHECKS                      |      |

|-------------------------------------------|------|

| Introduction                              | 4-1  |

| 4101 - Power Checks                       | 4-4  |

| Servo Checks                              | 4-6  |

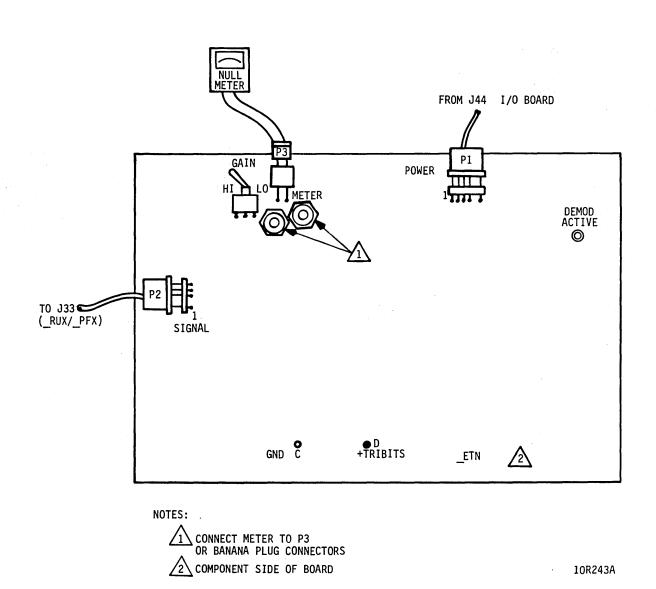

| 4201 - Tribit Check                       | 4-6  |

| 4202 - Position Signal Check              | 4-8  |

| 4203 - Servo Offset Check                 | 4-10 |

| 4204 - On Cylinder Check                  | 4-10 |

| 4205 - Cylinder Pulse Check               | 4-11 |

| 4206 - Power Amp Driver Check             | 4-11 |

| 4207 - Servo Test Mode                    | 4-12 |

| Write Checks                              | 4-16 |

| 4301 - Write Fault Grounding              | 4-17 |

| 4302 - Write PLO Check                    | 4-18 |

| 4303 - Write Data Check                   | 4-20 |

| 4304 - Write Address Mark Check           | 4-24 |

| 4305 - Write Current Check                | 4-25 |

| Read Checks                               | 4-27 |

| 4401 - Read PLO Check                     | 4-28 |

| 4402 - Read Data Check                    | 4-30 |

| 4403 - Read Address Mark Check            | 4-34 |

| Miscellaneous Logic Checks                | 4-38 |

| 4501 - Index Check                        | 4-38 |

| 4502 - Sector Check                       | 4-40 |

|                                           | •    |

| 5. REPAIR AND REPLACEMENT                 |      |

| Introduction                              | 5-1  |

| 5101 - Entire Drive Removal & Replacement | 5-4  |

| Removal                                   | 5-4  |

| Replacement                               | 5-5  |

| 5102 - Top Cover Removal & Replacement    | 5-7  |

| Removal                                   | 5-7  |

| Replacement                               | 5-7  |

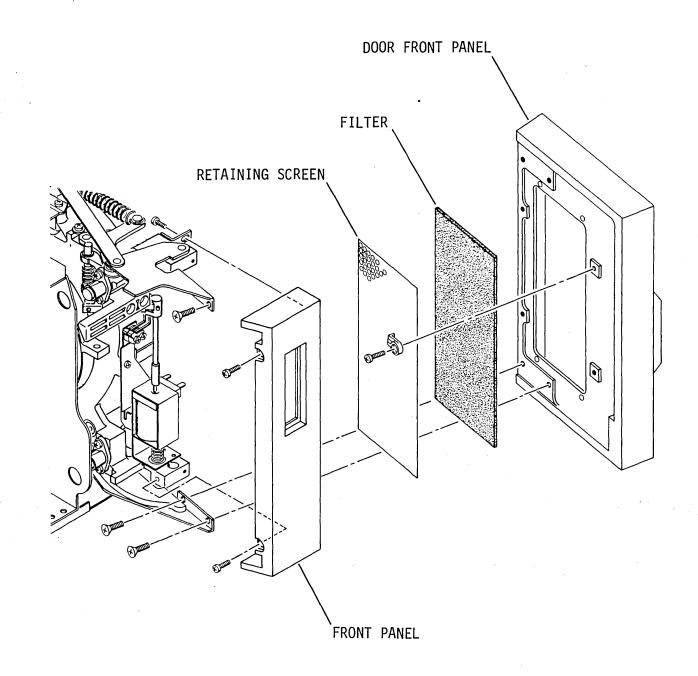

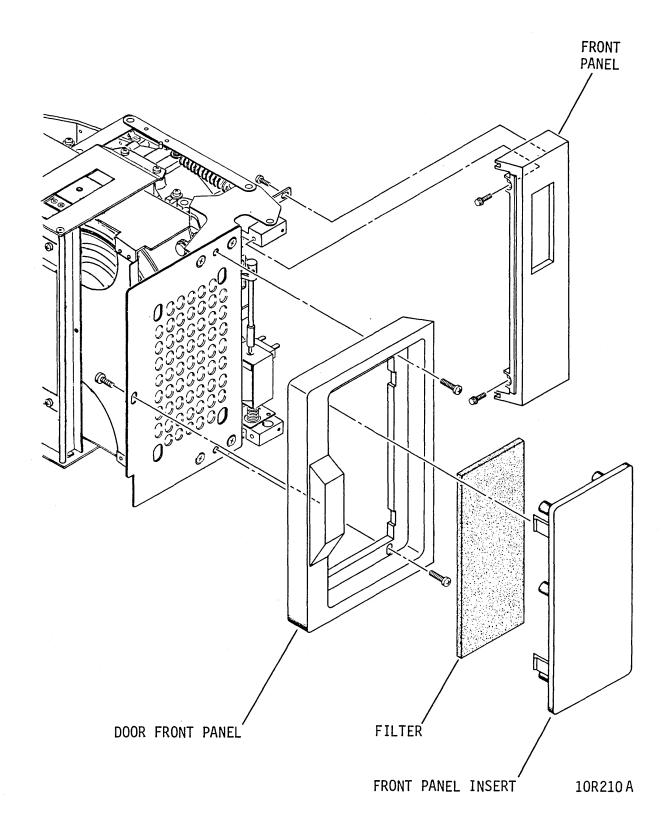

| 5103 - Front Panel Removal & Replacement                   | <b>√5−8</b> |

|------------------------------------------------------------|-------------|

| Removal (S/C 01 )                                          | 5-8         |

| Replacement (S/C 01 )                                      | 5-8         |

| Removal (S/C 02 & Abv)                                     | 5-10        |

| Replacement (S/C 02 & Abv)                                 | 5-10        |

| 5104 - Slide Removal & Replacement                         | 5-12        |

| Removal                                                    | 5-12        |

| Replacement                                                | 5-12        |

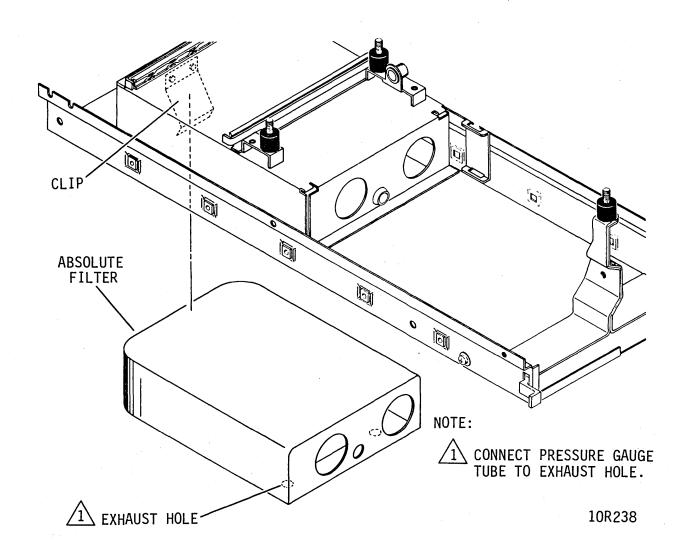

| 5105 - Absolute Filter Removal, Replacement & Testing      | 5-14        |

| Testing                                                    | 5-14        |

| Removal                                                    | 5-14        |

| Replacement                                                | 5-15        |

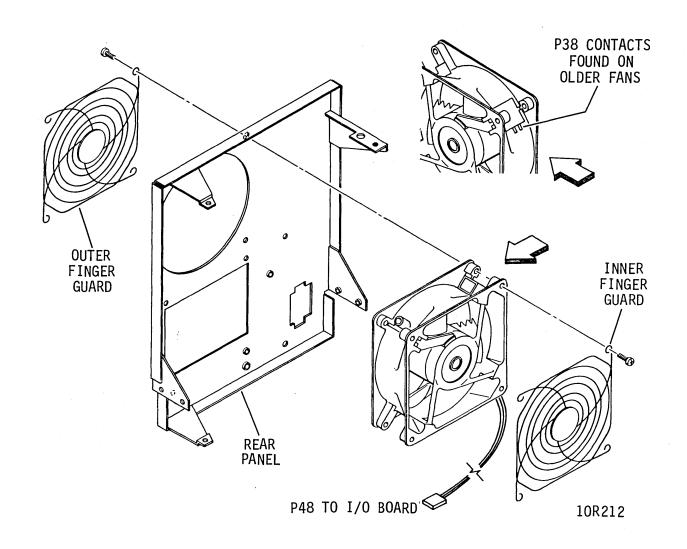

| 5201 - Fan Removal & Replacement                           | 5-16        |

| Removal                                                    | 5-16        |

| Replacement                                                | 5-16        |

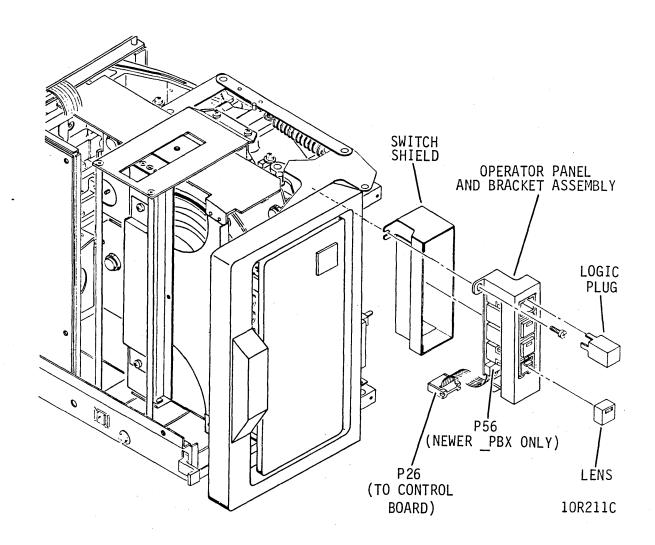

| 5202 - Operator Panel (_PBX) Removal & Replacement         | 5-18        |

| Removal                                                    | 5-18        |

| Replacement                                                | 5-18        |

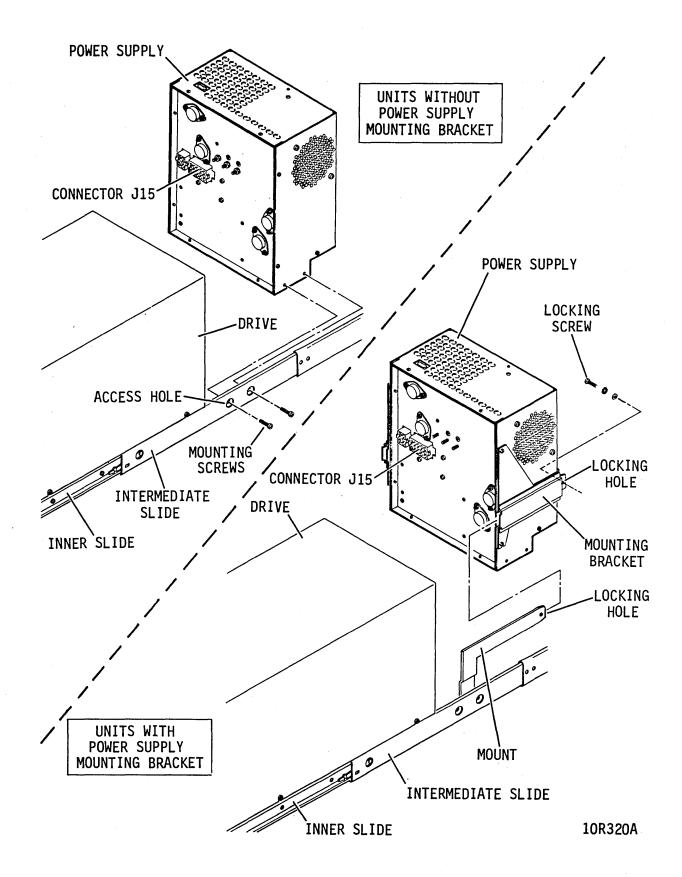

| 5203 - Power Supply Removal & Replacement                  | 5-20        |

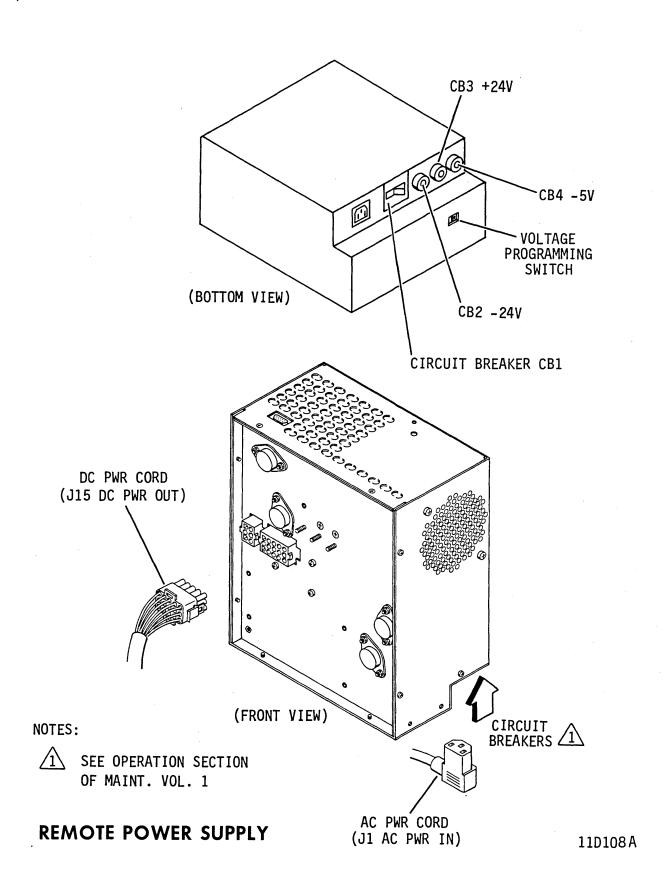

| Removal (Remote Power Supply)                              | 5-20        |

| Replacement (Remote Power Supply Without Mounting Bracket) | 5-23        |

| Replacement (Remote Power Supply With Mounting Bracket)    | 5-23        |

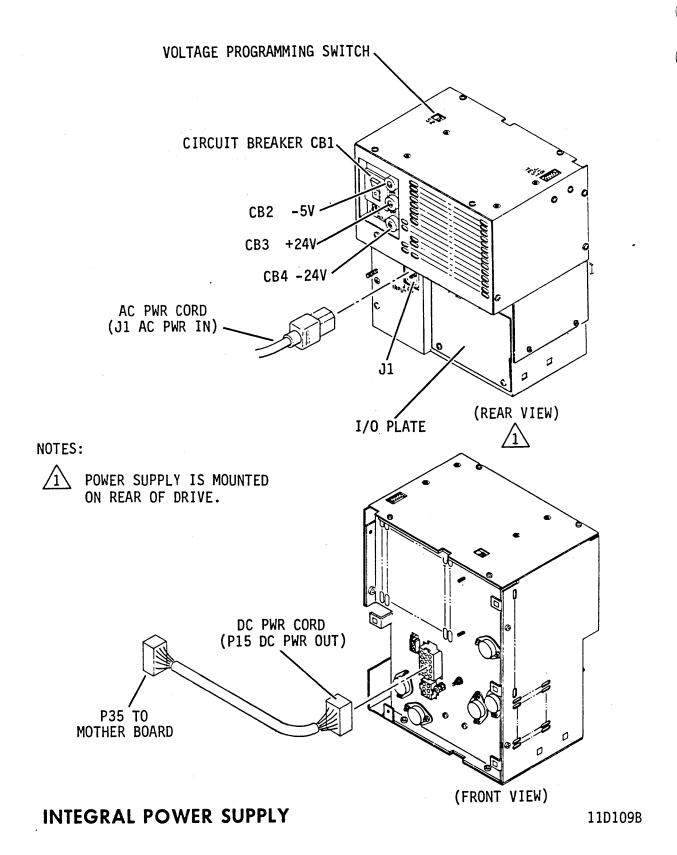

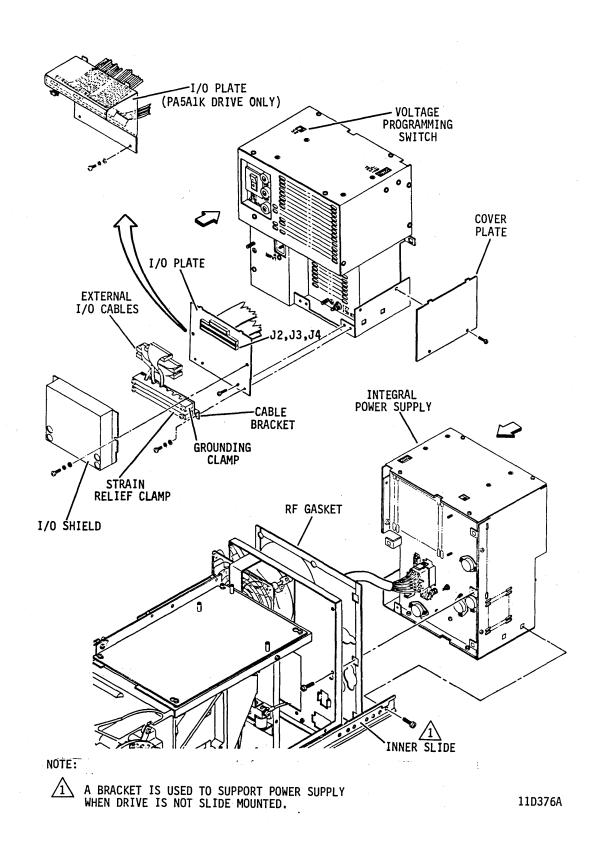

| Removal (Integral Power Supply)                            | 5-24        |

| Replacement (Integral Power Supply)                        | 5-27        |

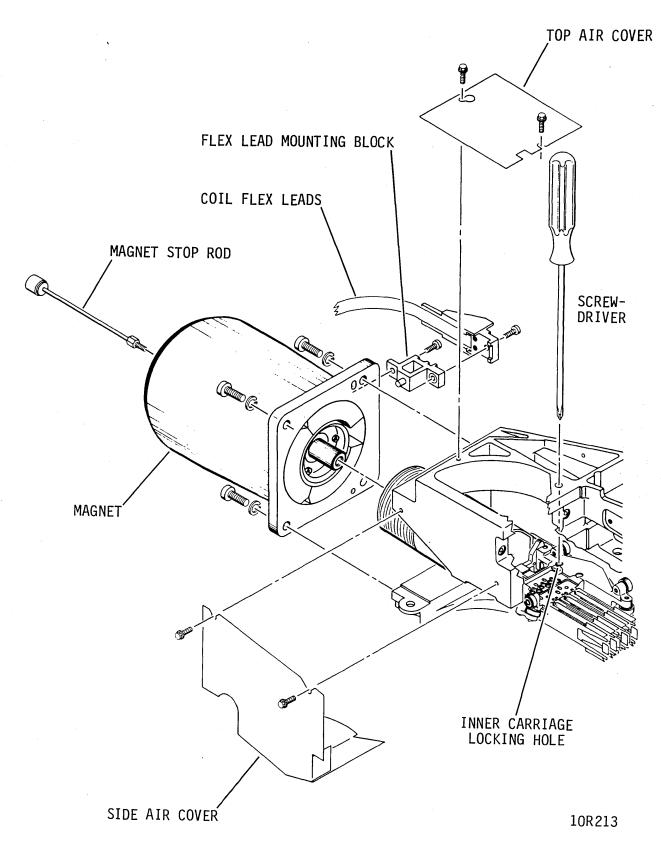

| 5204 - Magnet Removal & Replacement                        | 5-28        |

| Removal                                                    | 5-28        |

| Replacement                                                | 5-31        |

| 205 - Coil Assembly Removal, Replacement & Alignment       | 5-32        |

| Removal                                                    | 5-32        |

| Replacement & Alignment                                    | 5-32        |

| 206 - Carriage Removal & Replacement                       | 5-34        |

| Removal                                                    | 5-34        |

| Replacement                                                | 5-34        |

83324490 G

| 5207 - Upper & Lower Rails Removal & Replacement                                | 5-36 |

|---------------------------------------------------------------------------------|------|

| Removal                                                                         | 5-36 |

| Replacement                                                                     | 5-39 |

| 5208 - Rails & Bearings Inspection & Cleaning                                   | 5-42 |

| 5209 - Motor & Cable Assembly Removal & Replacement                             | 5-44 |

| Removal                                                                         | 5-44 |

| Replacement                                                                     | 5-47 |

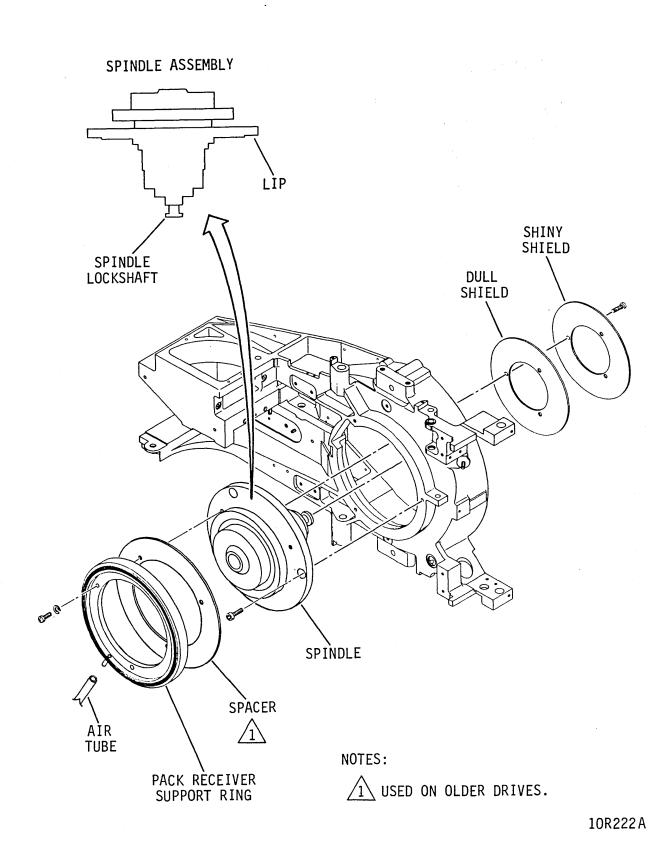

| 5210 - Spindle Removal & Replacement                                            | 5-48 |

| Removal                                                                         | 5-48 |

| Replacement                                                                     | 5-48 |

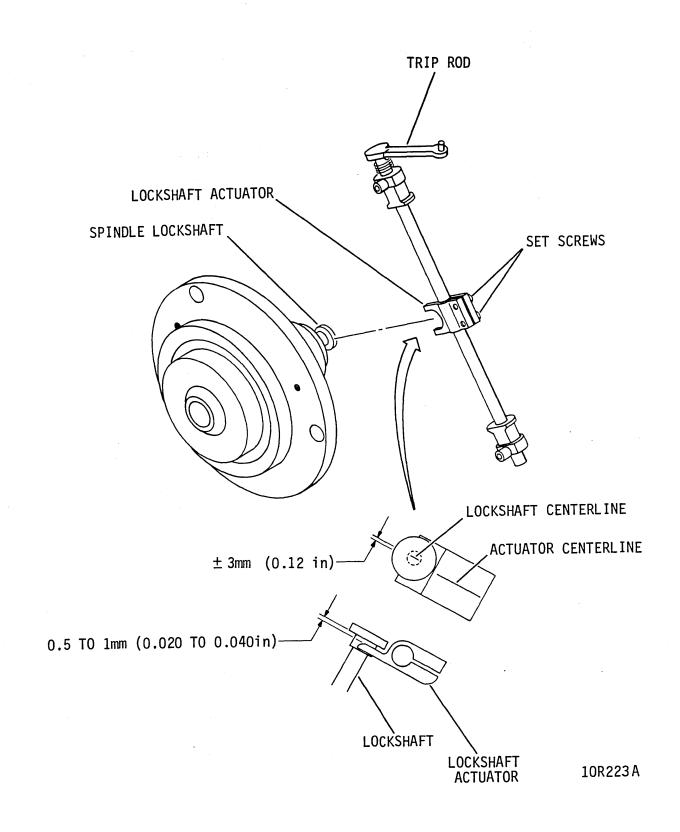

| 5211 - Spindle Lockshaft Adjustment                                             | 5-50 |

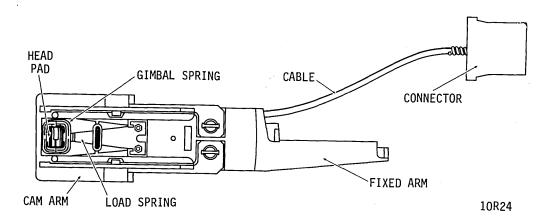

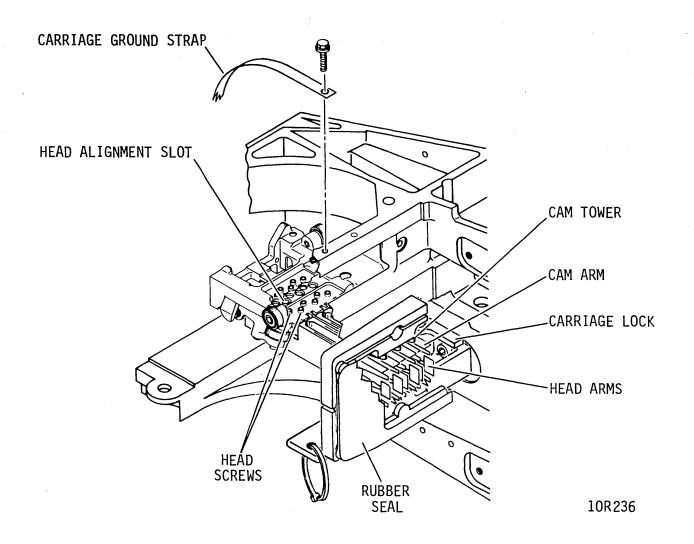

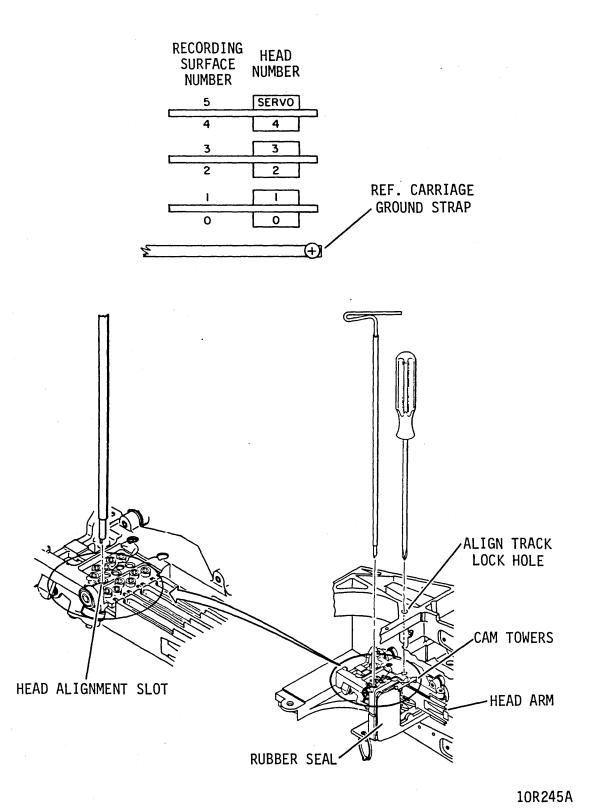

| 5212 - Head Arm Removal, Replacement & Alignment                                | 5-52 |

| Removal (Carriage and Coil Assembly Installed)                                  | 5-52 |

| Replacement (Carriage and Coil Assembly Installed)                              | 5-55 |

| Removal (Carriage and Coil Assembly Removed)                                    | 5-55 |

| Replacement (Carriage and Coil Assembly Removed)                                | 5-56 |

| Head Alignment                                                                  | 5-58 |

| General                                                                         | 5-58 |

| Procedure                                                                       | 5-59 |

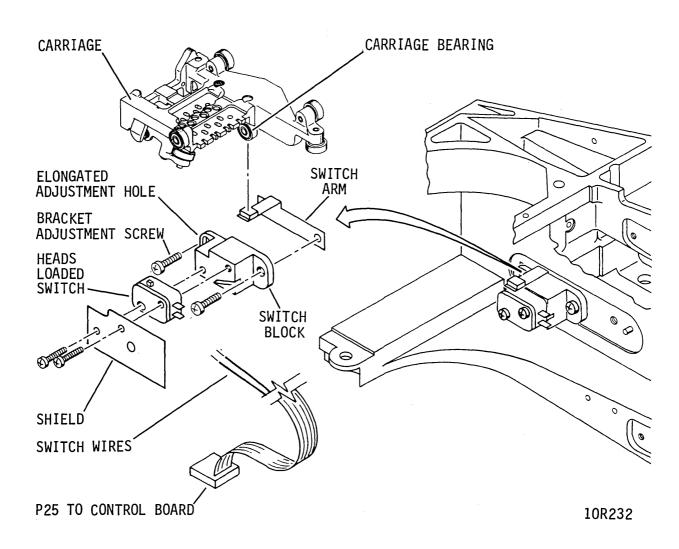

| 5213 - Heads Loaded Switch Removal, Replacement &                               |      |

| Adjustment                                                                      | 5-68 |

| Removal                                                                         | 5-68 |

| Replacement and Adjustment                                                      | 5-68 |

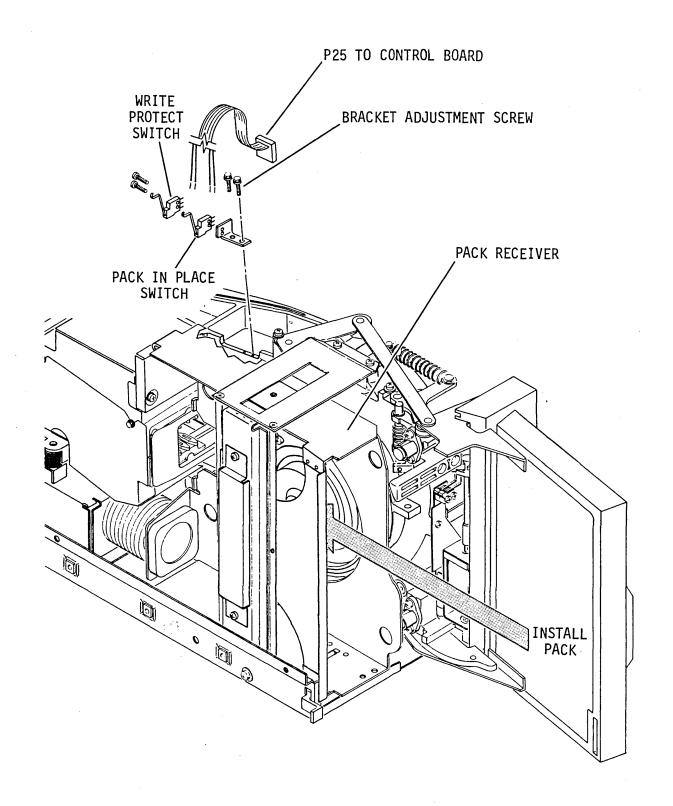

| 5214 - Pack In Place & Write Protect Switches Removal, Replacement & Adjustment | 5-70 |

| Removal                                                                         | 5-70 |

| Replacement and Adjustment                                                      | 5-70 |

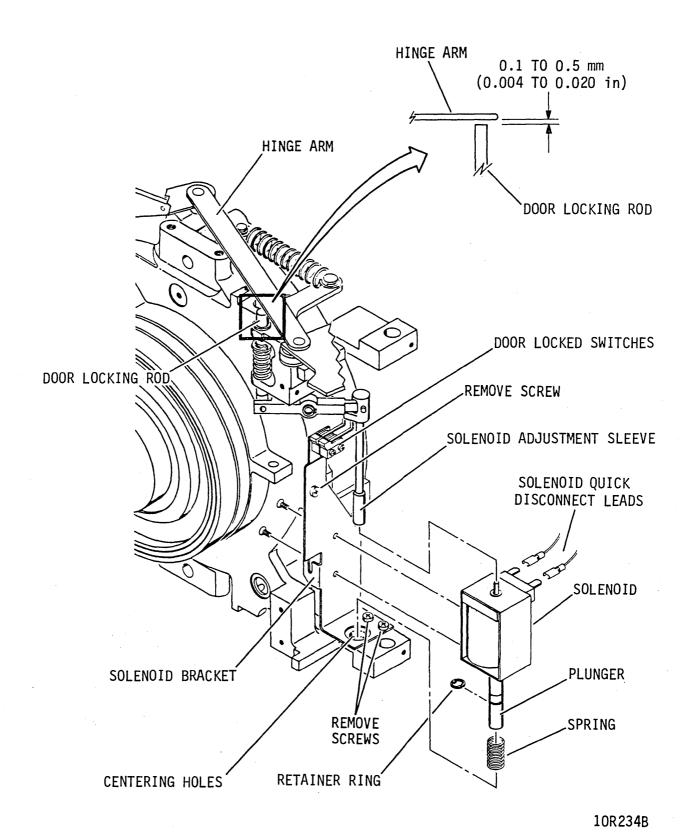

| 5215 - Door Unlock Solenoid Removal, Replacement &                              | 3-70 |

| Adjustment                                                                      | 5-74 |

| Removal                                                                         | 5-74 |

| Replacement & Adjustment                                                        | 5-74 |

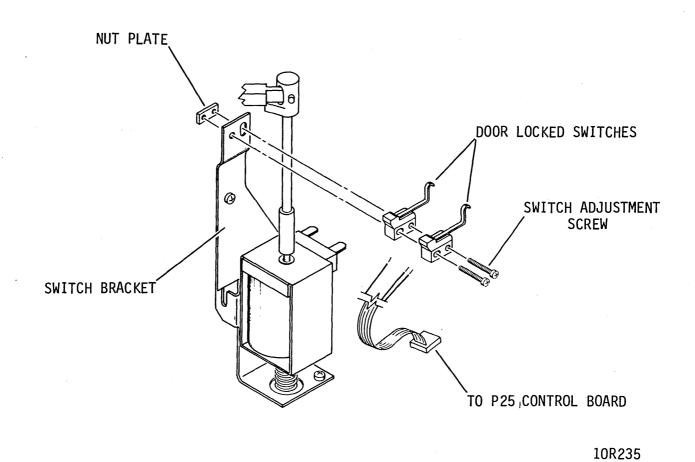

| 5216 - Door Locked Switches Removal, Replacement & Adjustment                   | 5-78 |

| Removal                                                                         | 5-78 |

|                                                                                 |      |

| Replacement and Adjustment                                                      | 5-78 |

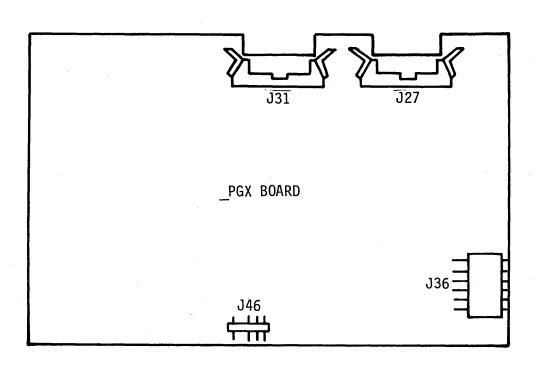

| 5301 - Read/Write PLO Board (_PGX) Removal & Replacement                        | 5-80 |

xviii

| Removal                       |                            | 5-80 |

|-------------------------------|----------------------------|------|

| Replacement                   |                            | 5-80 |

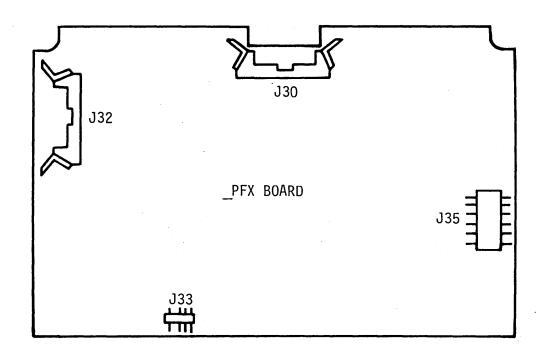

| 5302 - Data Latch Board (_PF  | X) Removal & Replacement   | 5-82 |

| Removal                       |                            | 5-82 |

| Replacement                   |                            | 5-82 |

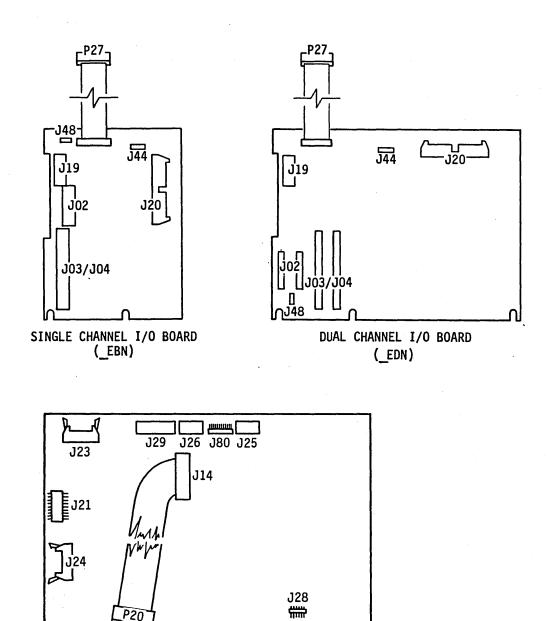

| 5303 - I/O Boards (_EBN/_EDN  | ) Removal & Replacement    | 5-84 |

| Removal (I/O Boards With F    | ixed I/O Cables)           | 5-84 |

| Replacement (I/O Boards Wi    | th Fixed I/O Cables)       | 5-85 |

| Removal (I/O Boards With D    | etachable I/O Cables)      | 5-87 |

| Replacement (I/O Boards Wi    | th Detachable I/O Cables)  | 5-87 |

| 5304 - Control Board (_PEX)   | Removal & Replacement      | 5-88 |

| Removal                       |                            | 5-88 |

| Replacement                   | •                          | 5-88 |

| 5305 - R/W Preamp Board (_PC  | X) Removal & Replacement   | 5-90 |

| Removal                       |                            | 5-90 |

| Replacement                   |                            | 5-90 |

| 5306 - Servo Preamp Board (_  | UUN) Removal & Replacement | 5-92 |

| Removal                       |                            | 5-92 |

| Replacement                   |                            | 5-92 |

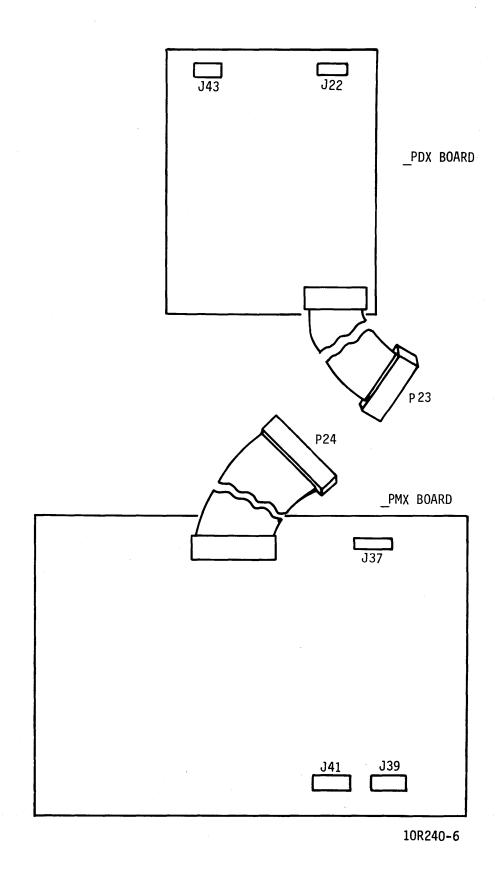

| 5307 - Power Amp Board (_PDX  | ) Removal & Replacement    | 5-94 |

| Removal                       |                            | 5-94 |

| Replacement                   |                            | 5-94 |

| 5308 - Motor Speed Control Bo | oard (_PMX) Removal &      |      |

| Replacement                   |                            | 5-96 |

| Removal                       |                            | 5-96 |

| Replacement                   |                            | 5-96 |

| 5309 - Read/Write Board (_RU  | K) Removal & Replacement   | 5-98 |

| Removal                       |                            | 5-98 |

| Poplagoment                   |                            |      |

83324490 G xix

### **FIGURES**

| 1-1  | Drive Functional Block Diagram          | 1-1  |

|------|-----------------------------------------|------|

| 1-2  | Power On Circuitry                      | 1-5  |

| 1-3  | Power On Sequence Flowchart             | 1-6  |

| 1-4  | Motor Speed Control System Diagram      | 1-11 |

| 1-5  | Speed Control Waveforms and Timing      | 1-13 |

| 1-6  | Motor Speed Control Simplified Logic    | 1-14 |

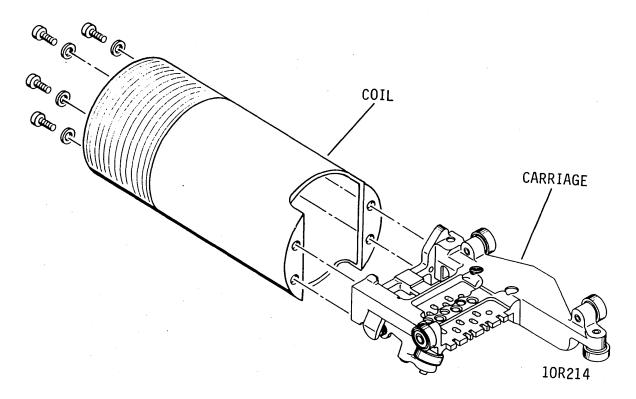

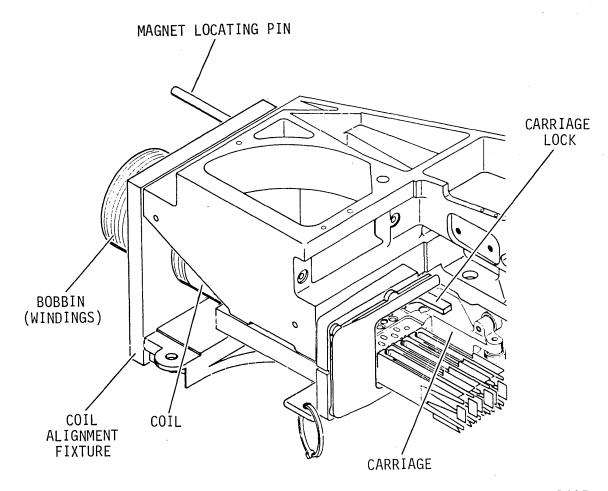

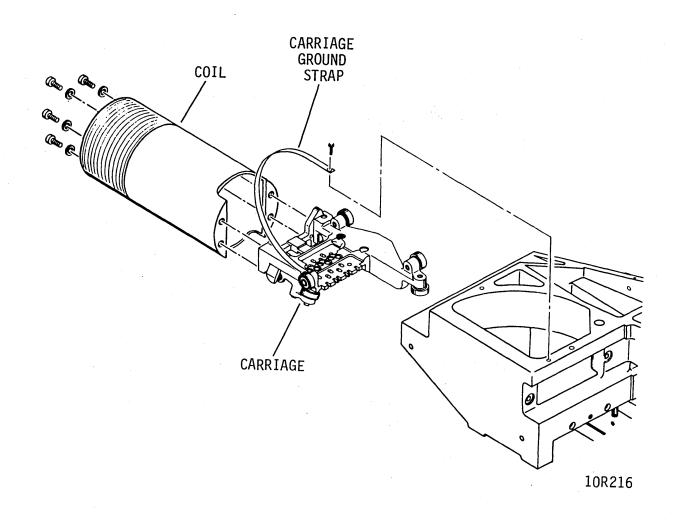

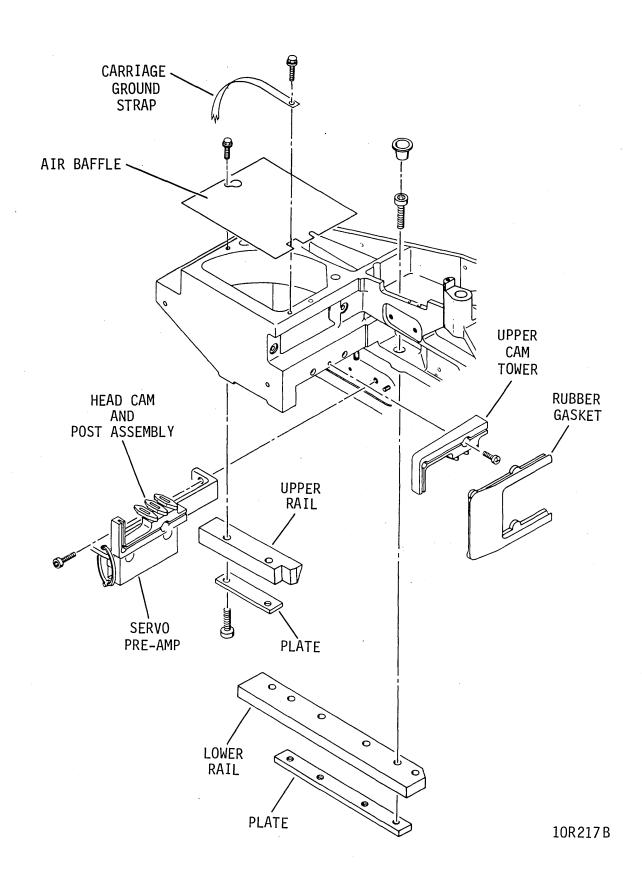

| 1-7  | Actuator and Magnet Assembly            | 1-16 |

| 1-8  | Data Heads                              | 1-17 |

| 1-9  | Drive Air Flow System                   | 1-20 |

| 1-10 | Closed Loop Air Flow                    | 1-21 |

| 1-11 | Interface Lines                         | 1-22 |

| 1-12 | I/O Signal Processing                   | 1-31 |

| 1-13 | Unit Select Logic (Single Channel)      | 1-34 |

| 1-14 | Channel I Dual Channel Logic            | 1-36 |

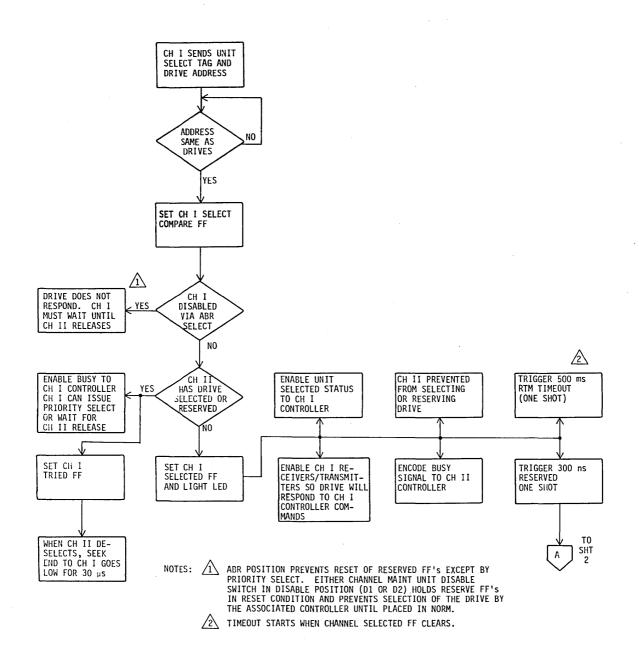

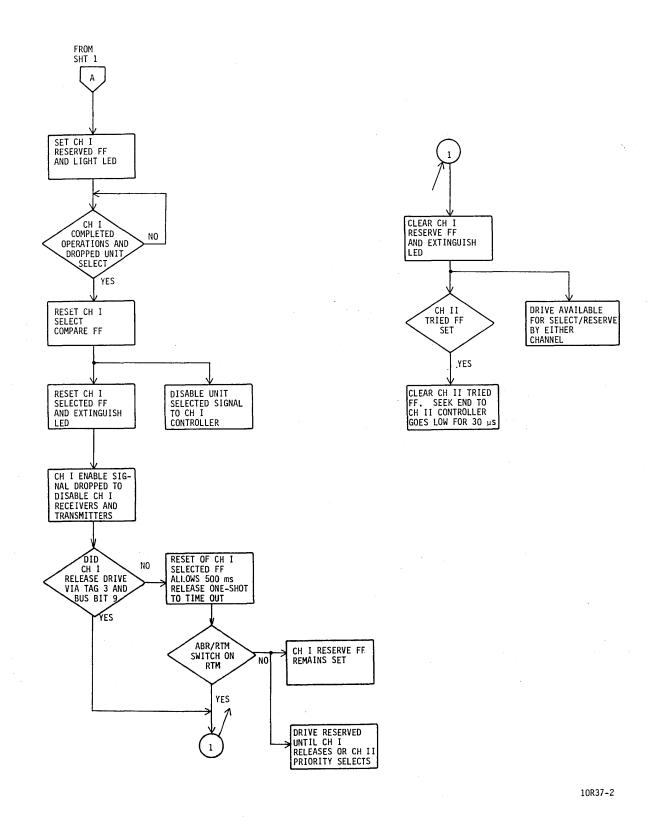

| 1-15 | Dual Channel Selection Flowchart        | 1-38 |

| 1-16 | Tribit Pattern                          | 1-46 |

| 1-17 | Tribit Signal Variations                | 1-48 |

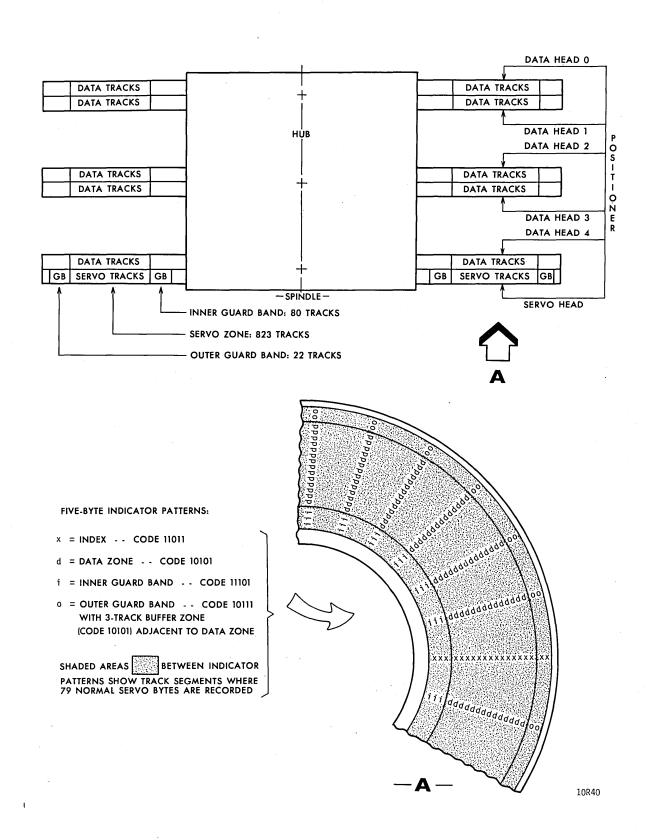

| 1-18 | Servo Disk Format                       | 1-49 |

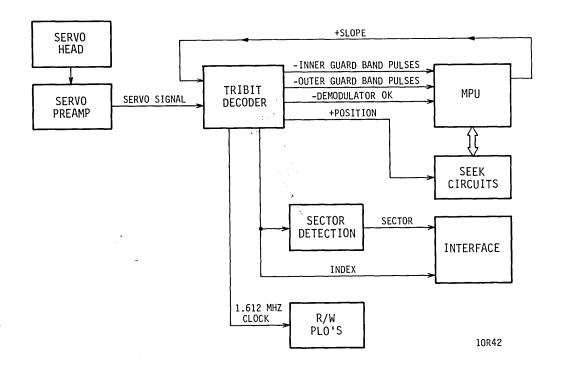

| 1-19 | Tribit Decoder System Diagram           | 1-50 |

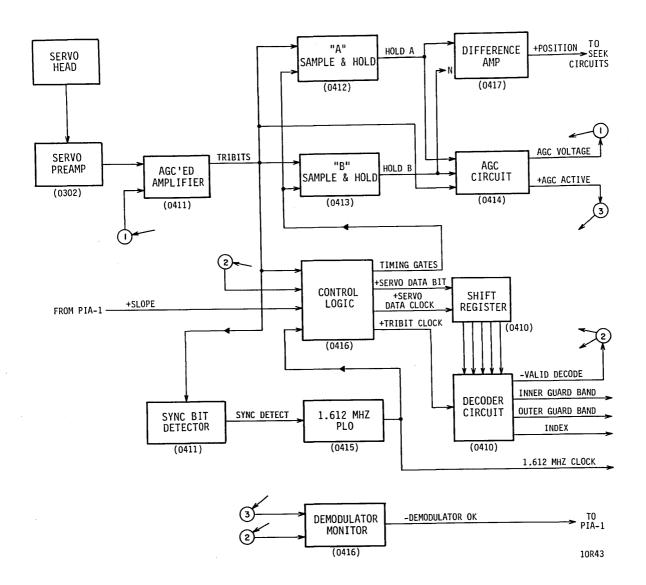

| 1-20 | Tribit Decoder Block Diagram            | 1-52 |

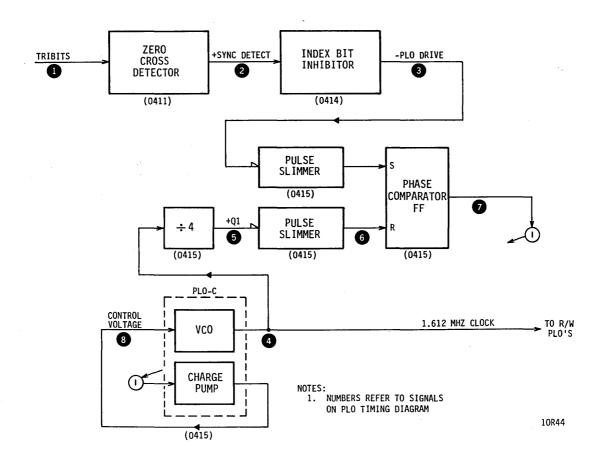

| 1-21 | PLO Block Diagram                       | 1-54 |

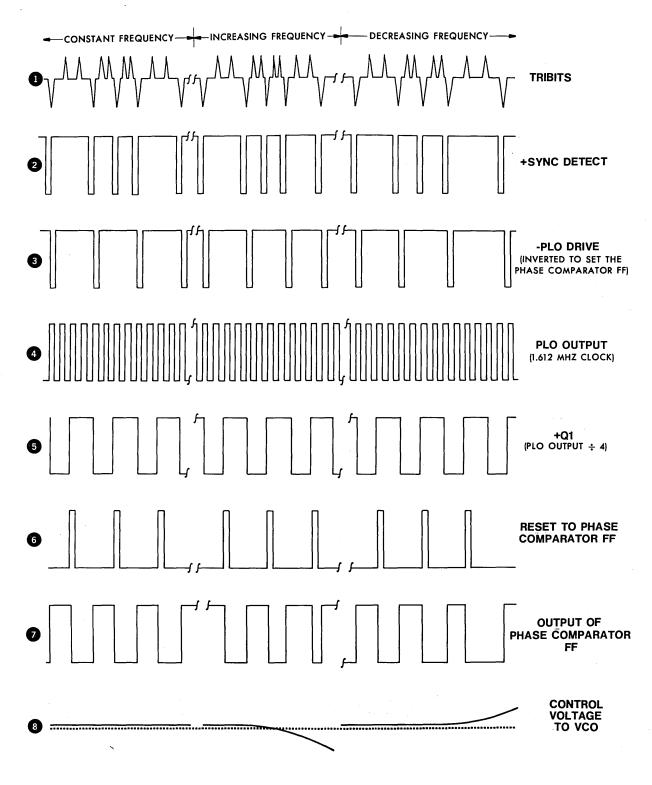

| 1-22 | PLO Timing                              | 1-55 |

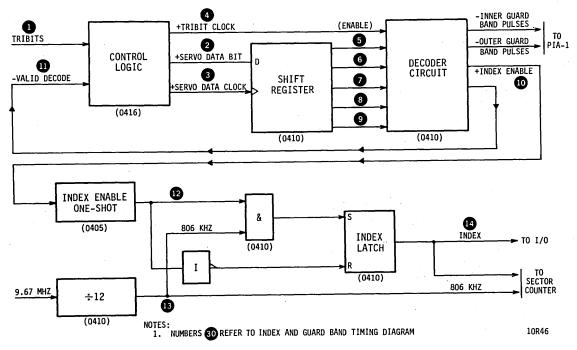

| 1-23 | Index and Guard Band Decoding Circuitry | 1-57 |

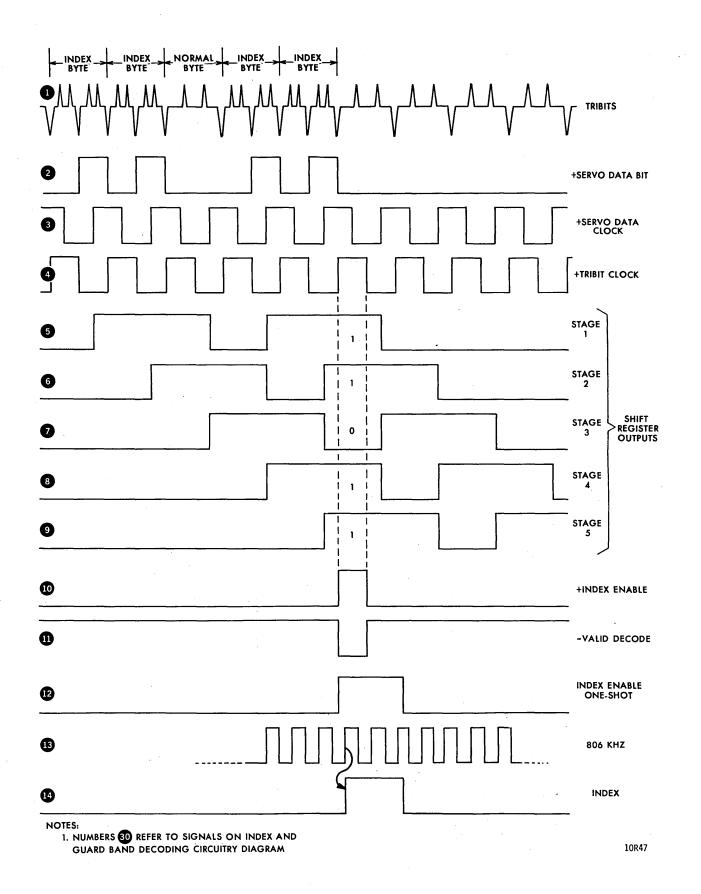

| 1-24 | Timing Relations in Index Decoding      | 1-58 |

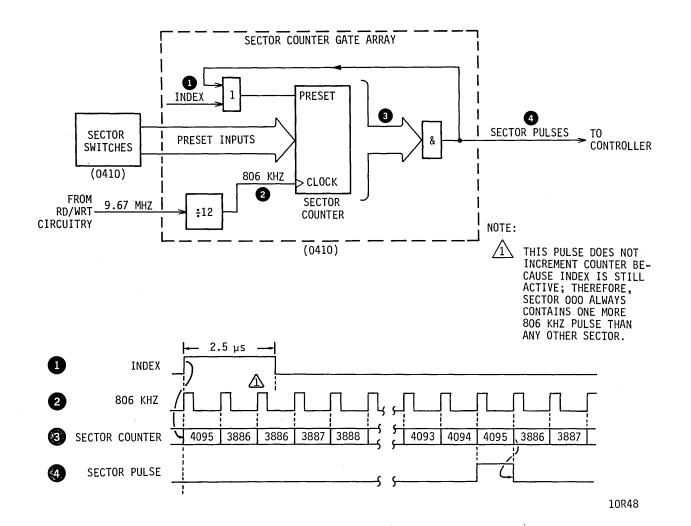

| 1-25 | Sector Detection - Logic and Timing     | 1-60 |

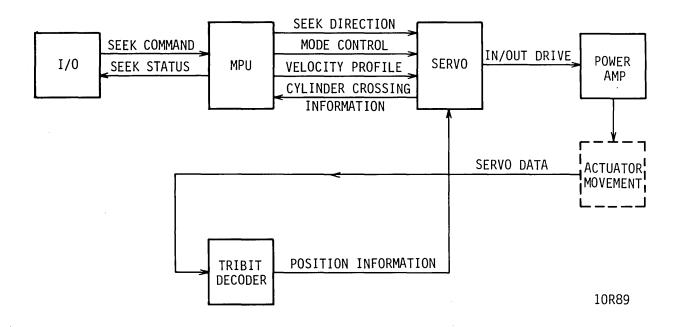

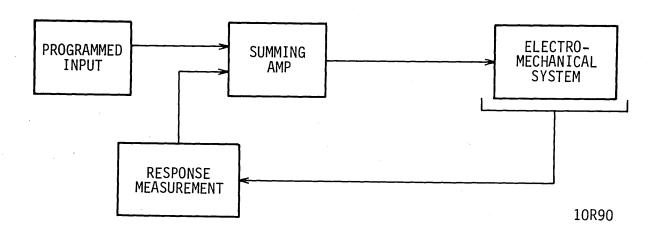

| 1-26 | Seek Functions Block Diagram            | 1-62 |

| 1-27 | Generalized Servo Loop                  | 1-63 |

| 1-28 | Simplified Coarse Servo Loop            | 1-63 |

| 1-29 | Simplified Fine Servo Loop              | 1-64 |

| 1-30 | Coarse Loop Block Diagram                | 1-66  |

|------|------------------------------------------|-------|

| 1-31 | Microprocessor Control System            | 1-68  |

| 1-32 | Desired Velocity Circuit                 | 1-71  |

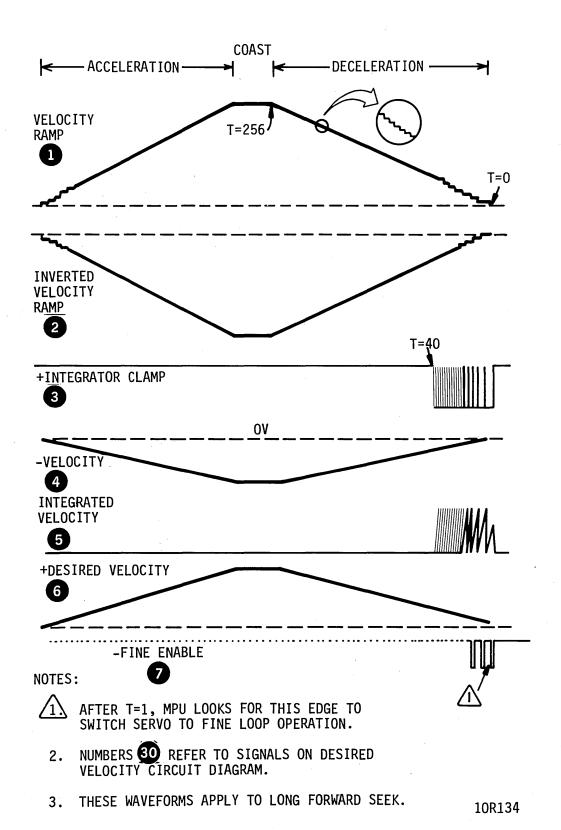

| 1-33 | Desired Velocity Waveforms               | 1-72  |

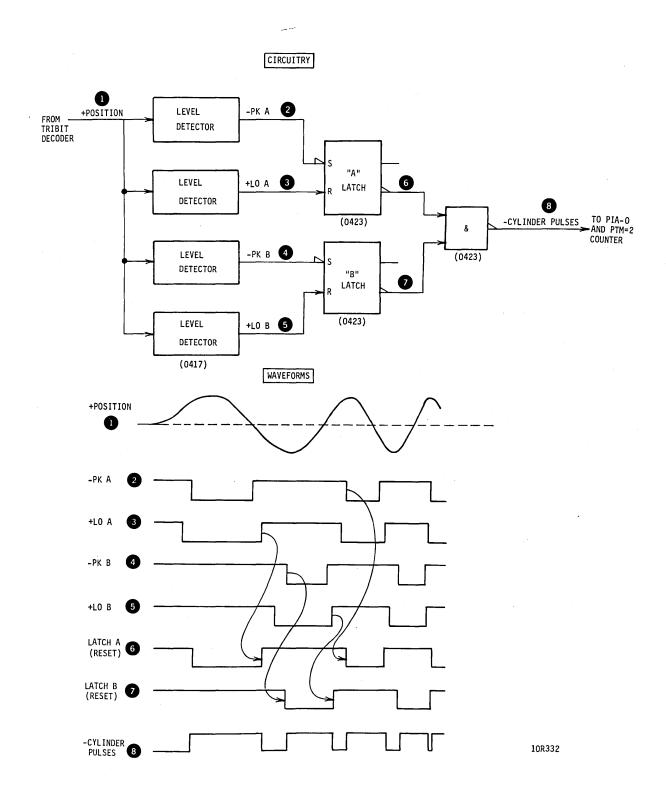

| 1-34 | Cylinder Pulse Circuitry and Waveforms   | 1-73  |

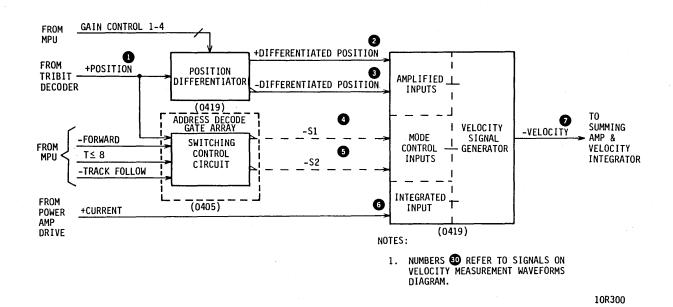

| 1-35 | Velocity Measurement Circuits            | 1-75  |

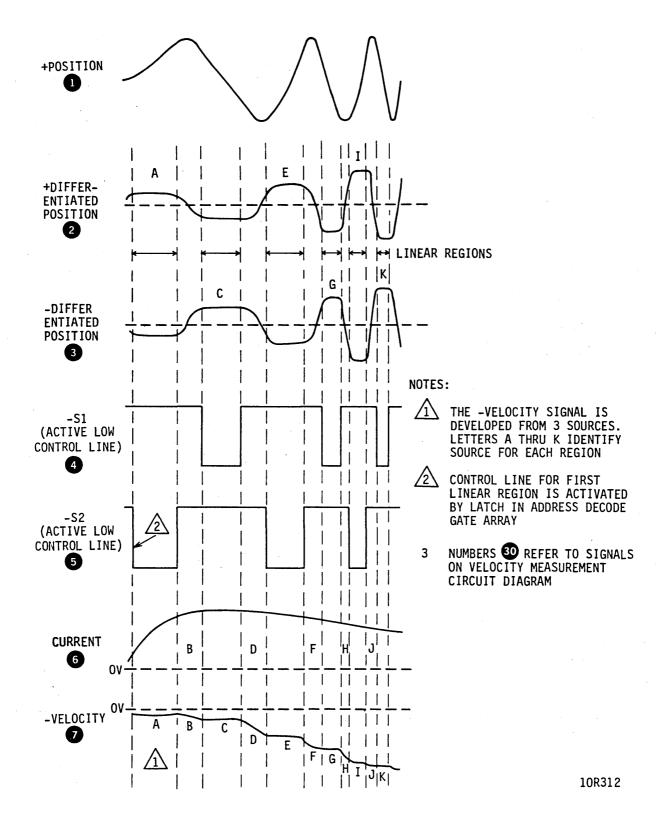

| 1-36 | Velocity Measurement Waveforms           | 1-76  |

| 1-37 | Power Amp Drive Circuitry                | 1-78  |

| 1-38 | Power Amp Circuitry                      | 1-79  |

| 1-39 | Fine Loop Block Diagram                  | 1-81  |

| 1-40 | Position Error Circuitry                 | 1-82  |

| 1-41 | Load/Retract Loops Block Diagram         | 1-85  |

| 1-42 | Load Operation Flowchart                 | 1-87  |

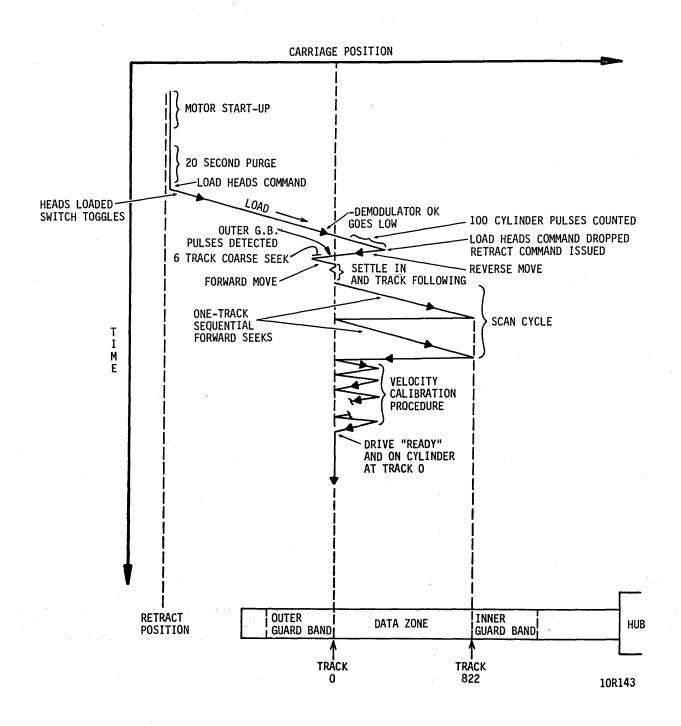

| 1-43 | Load Seek Trajectory                     | 1-91  |

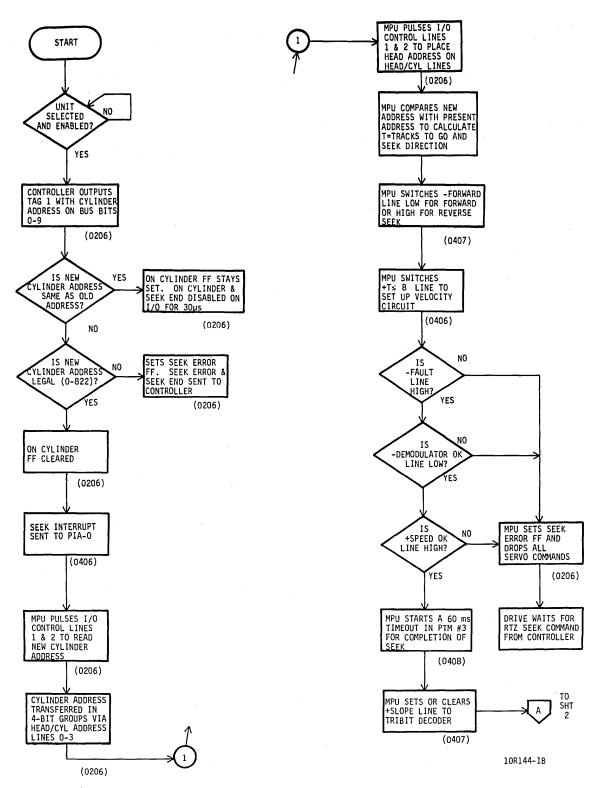

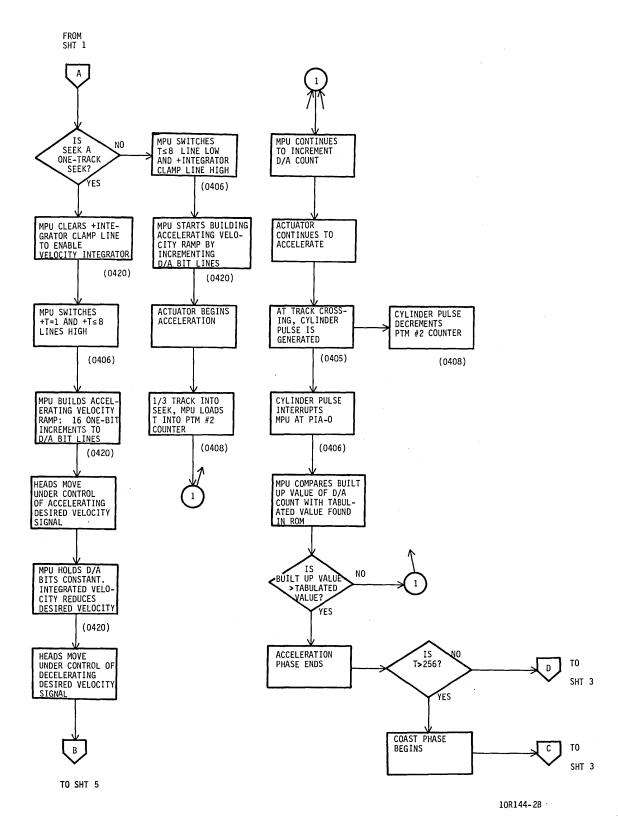

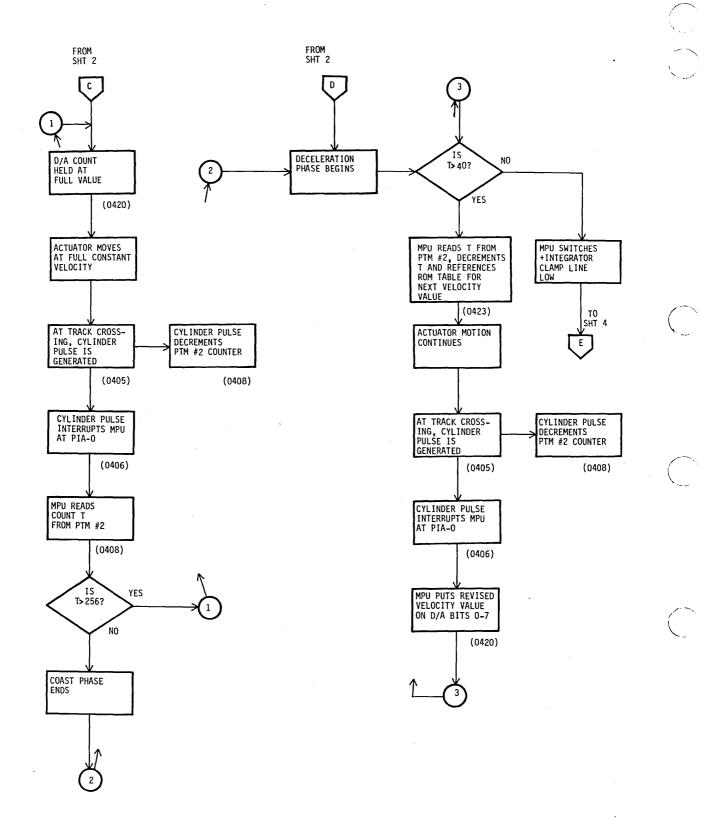

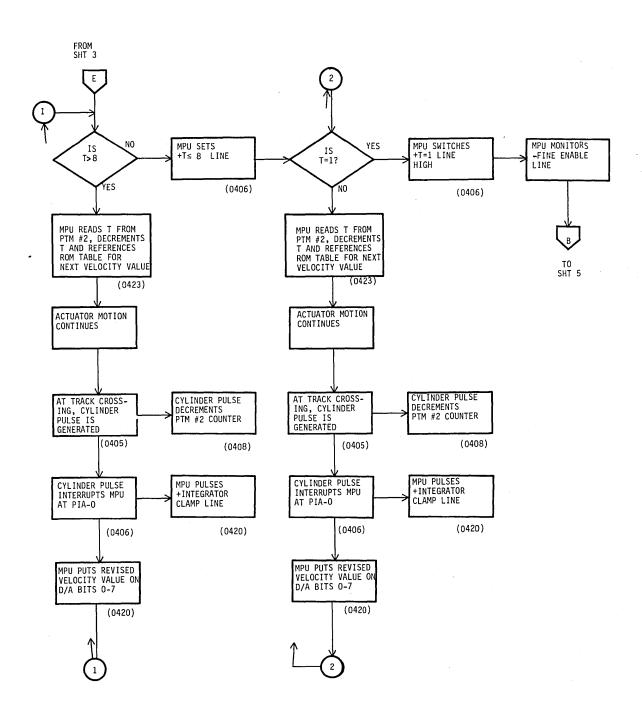

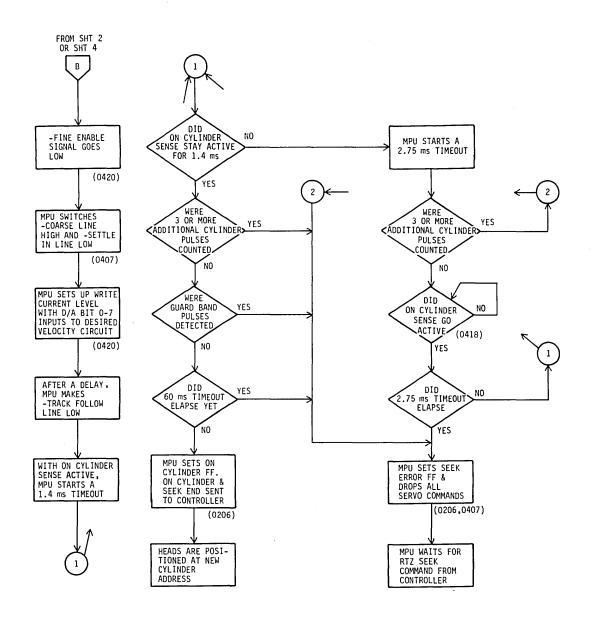

| 1-44 | Normal Seek Flowchart                    | 1-94  |

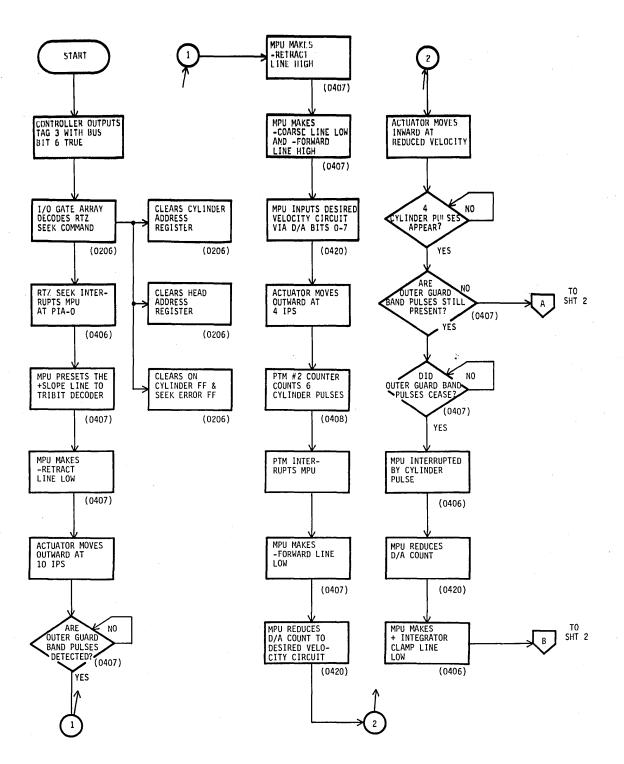

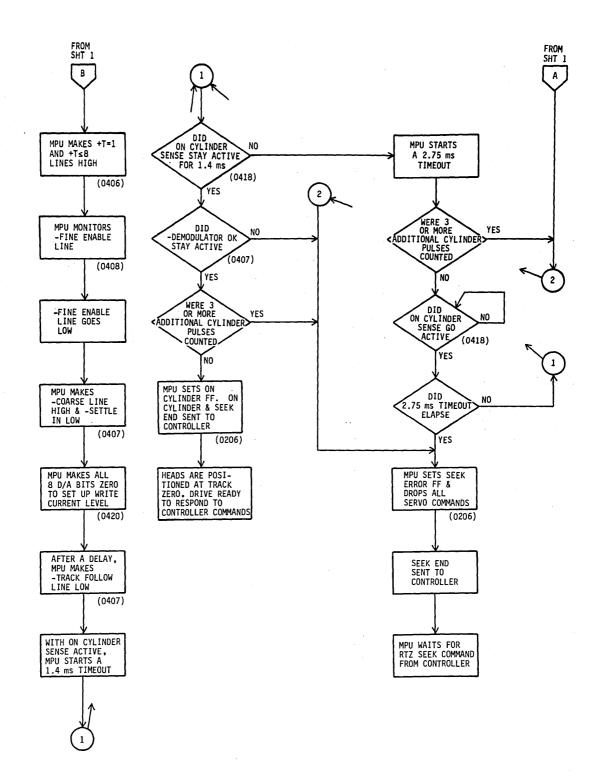

| 1-45 | Return to Zero (RTZ) Seek                | 1-102 |

| 1-46 | Read/Write Heads                         | 1-107 |

| 1-47 | Writing Data                             | 1-108 |

| 1-48 | Reading Data                             | 1-109 |

| 1-49 | Head Selection Circuits                  | 1-110 |

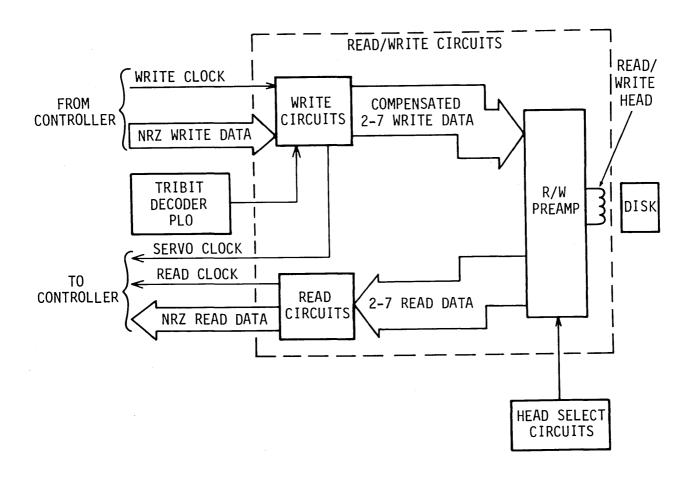

| 1-50 | Read/Write Circuits                      | 1-113 |

| 1-51 | Peak Shift Waveforms                     | 1-115 |

| 1-52 | Write Circuits Block Diagram             | 1-117 |

| 1-53 | Write PLO Block Diagram                  | 1-119 |

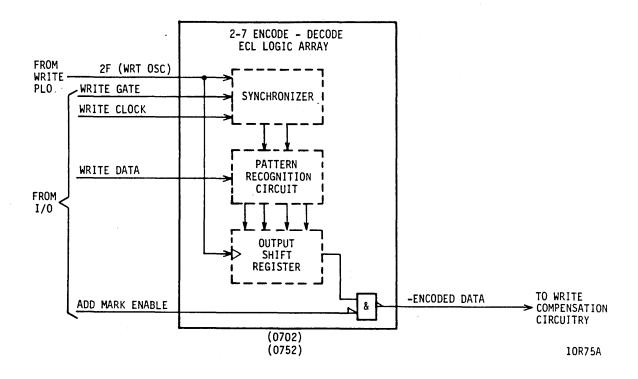

| 1-54 | 2-7 Encoder Block Diagram                | 1-120 |

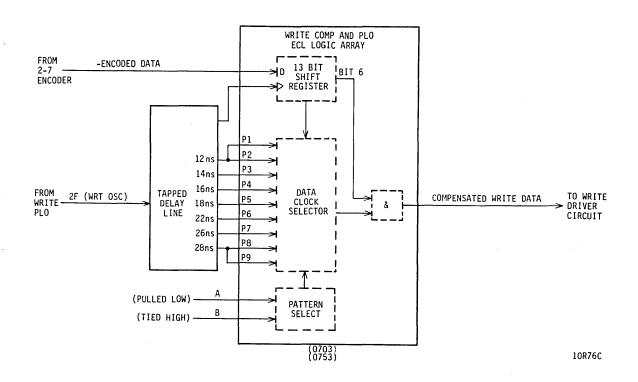

| 1-55 | Write Compensation Block Diagram         | 1-123 |

| 1-56 | Write Current Control and R/W Preamp     | 1-125 |

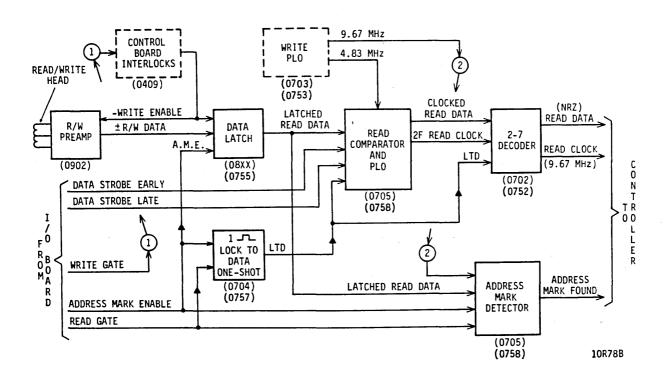

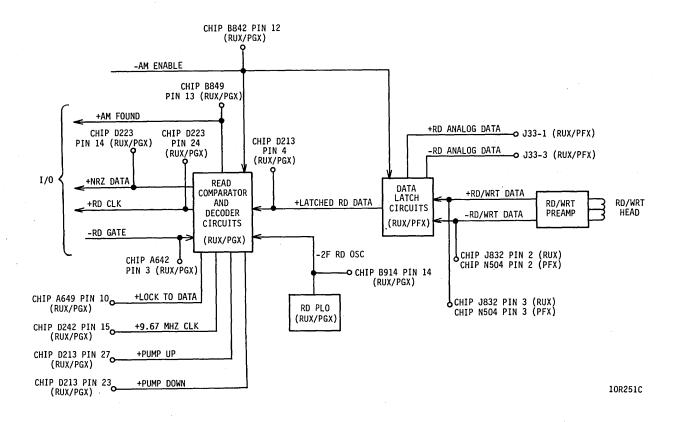

| 1-57 | Read Circuits Block Diagram              | 1-126 |

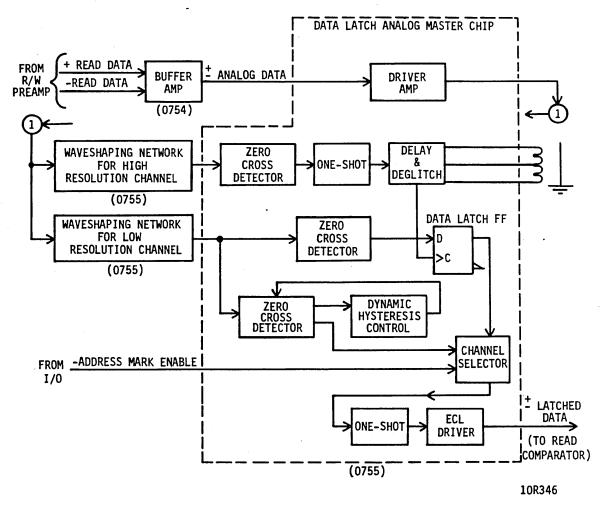

| 1-58 | Data Latch Block Diagram (One Board R/W) | 1-128 |

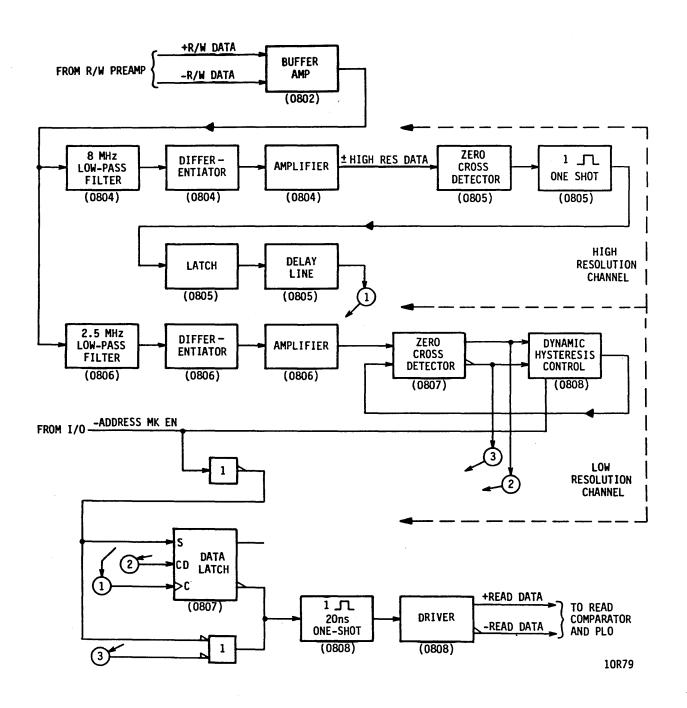

| 1-59 | Data Latch Block Diagram (Two Board R/W) | 1-130 |

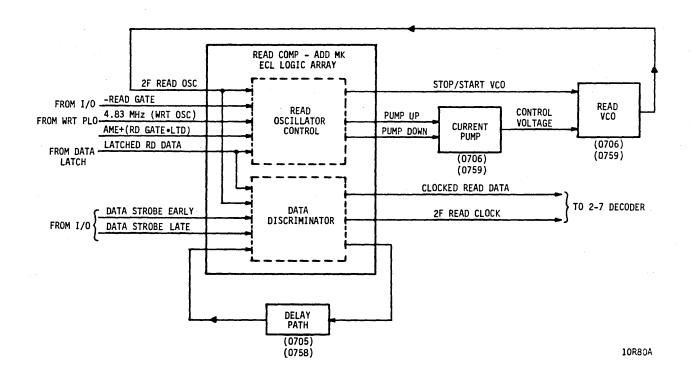

| 1-60 | Read Comparator and PLO Block Diagram    | 1-133 |

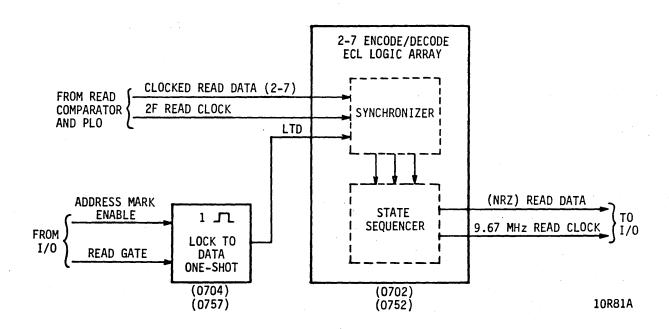

| 1-61 | 2-7 Decoder Block Diagram                | 1-135 |

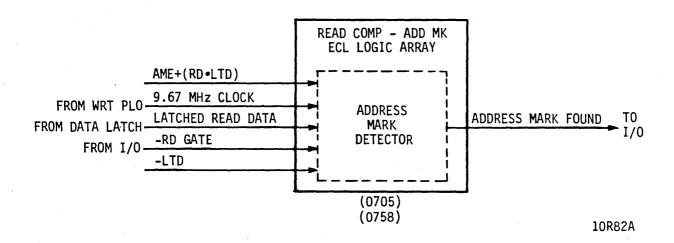

| 1-62 | Address Mark Detector Block Diagram      | 1136  |

83324490 G xxi

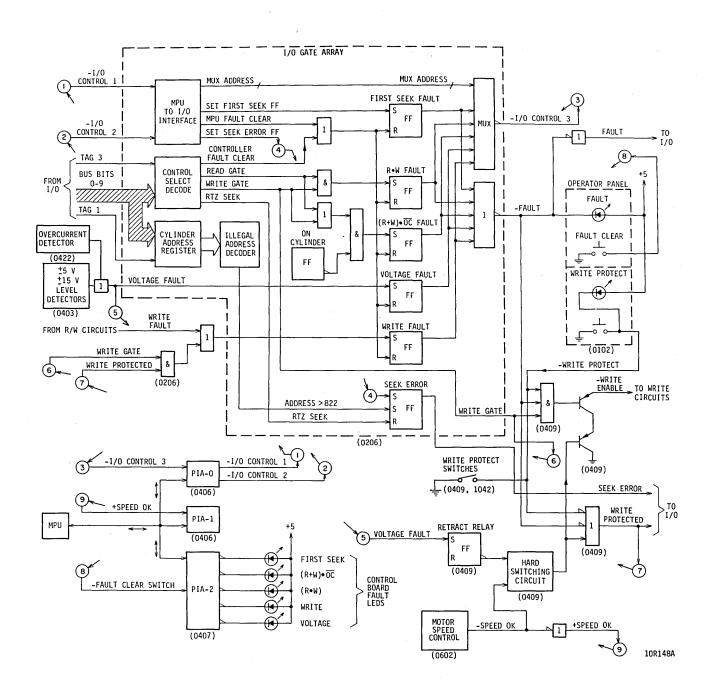

| 1-63 | Fault and Error Detection Circuitry             | 1-138 |

|------|-------------------------------------------------|-------|

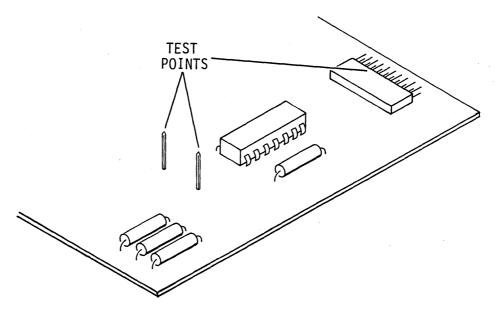

| 2-1  | Test Points                                     | 2-9   |

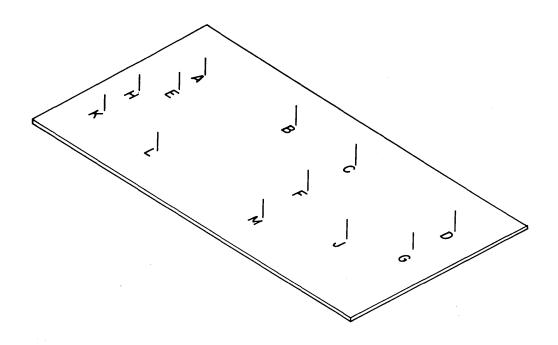

| 2-2  | Test Point Letter Designators                   | 2-10  |

| 2-3  | Component Locator                               | 2-11  |

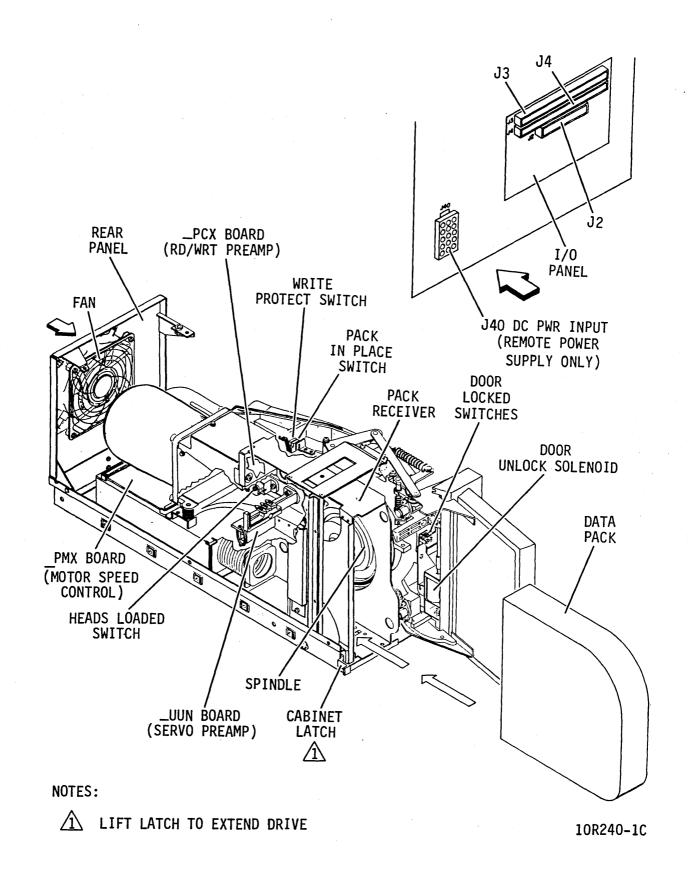

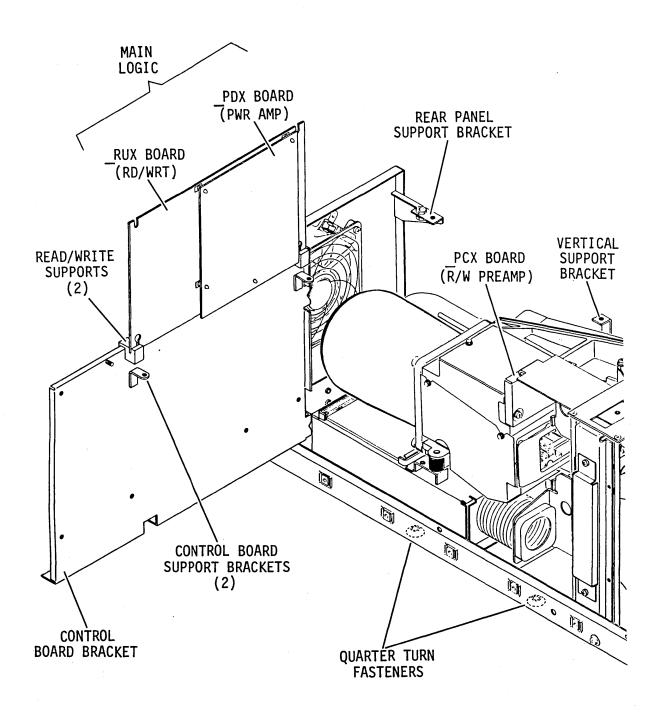

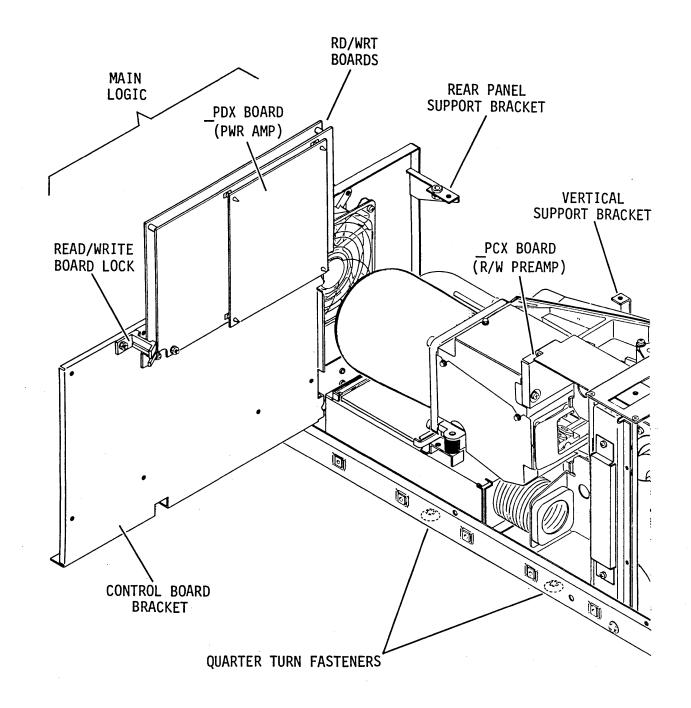

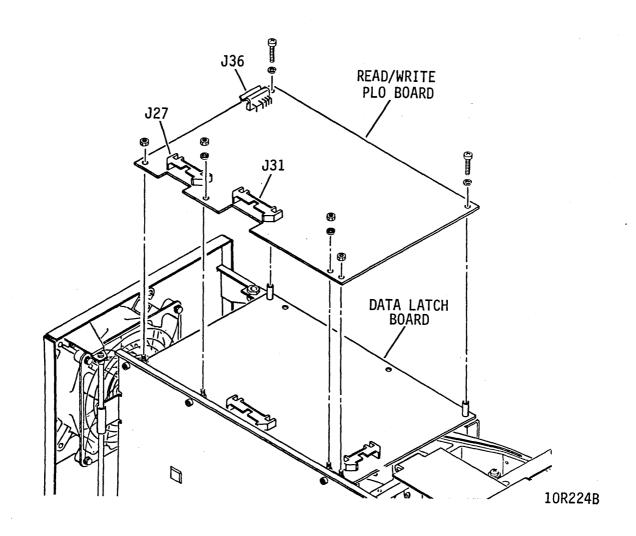

| 2-4  | One Board R/W Main Logic (Maintenance Position) | 2-20  |

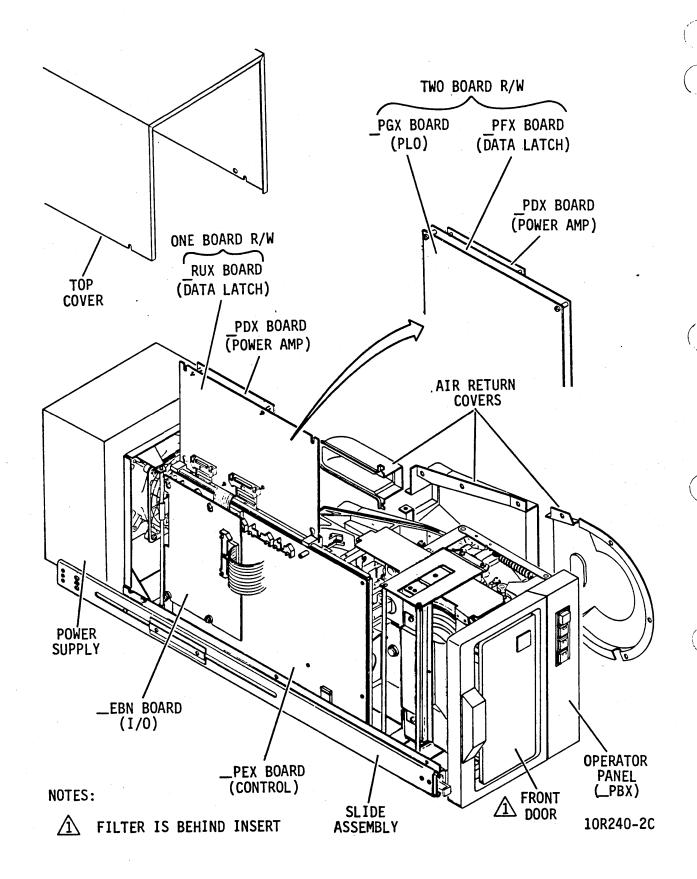

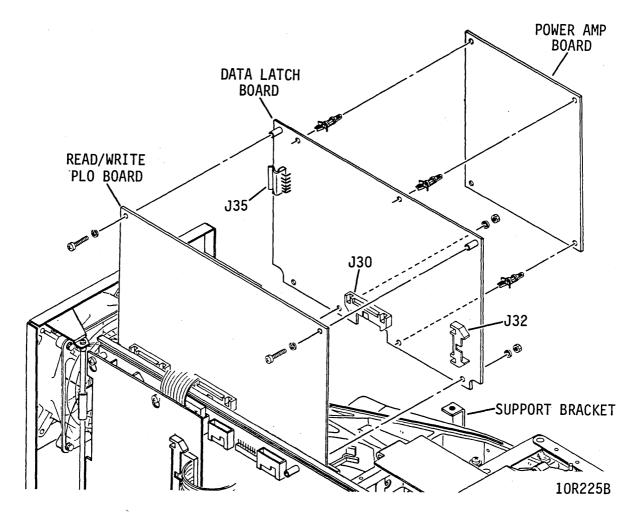

| 2-5  | Two Board R/W Main Logic (Maintenance Position) | 2-22  |

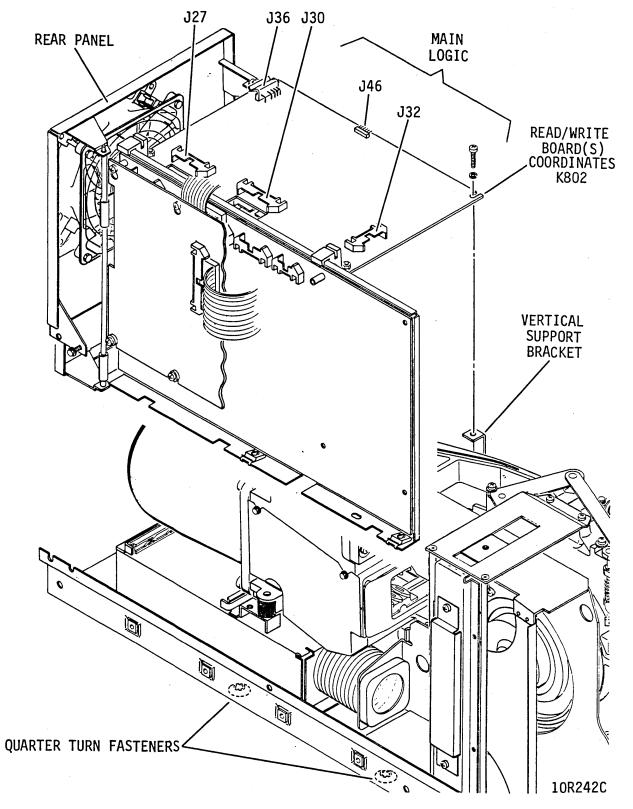

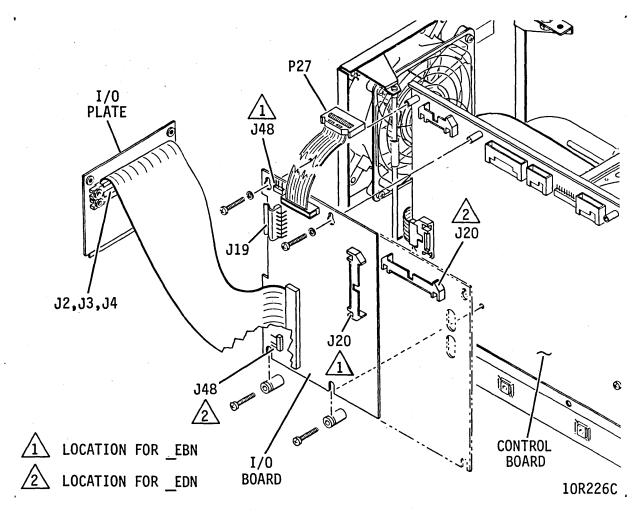

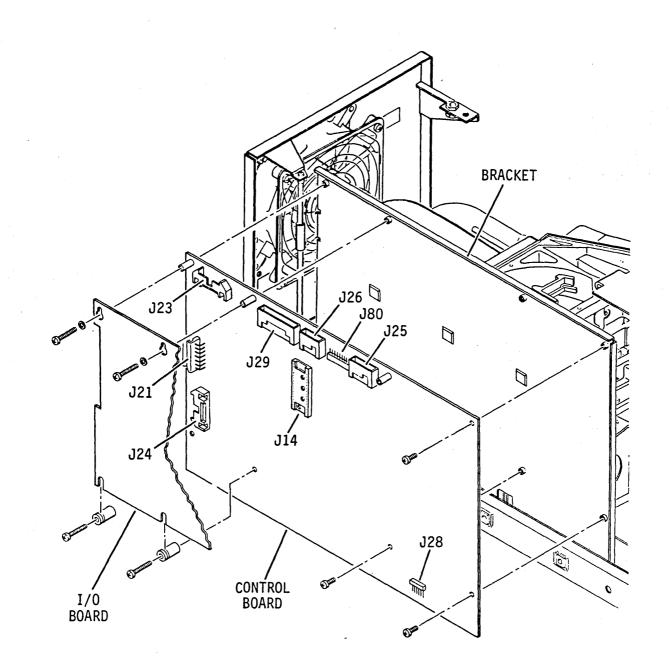

| 2-6  | Main Logic (Removal/Replacement)                | 2-24  |

| 2-7  | Releasing Door Unlock Solenoid                  | 2-27  |

| 3-1  | Example of Troubleshooting Procedure            | 3-4   |

| 3-2  | Servo Status Display Card Installation          | 3-26  |

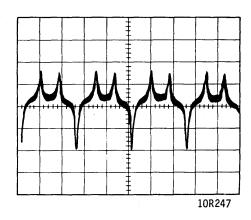

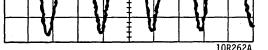

| 4-1  | Servo Signal Waveform                           | 4-7   |

| 4-2  | Tribits Waveform                                | 4-7   |

| 4-3  | Position Signal (Tracks 0-274)                  | 4-9   |

| 4-4  | Position Signal (Tracks 0 to 822)               | 4-9   |

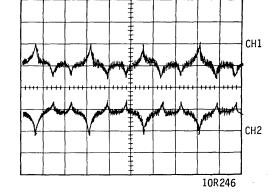

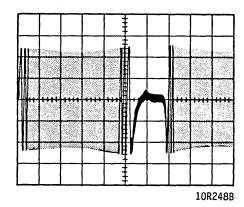

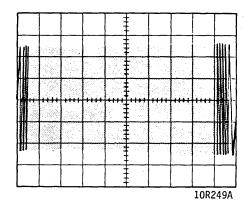

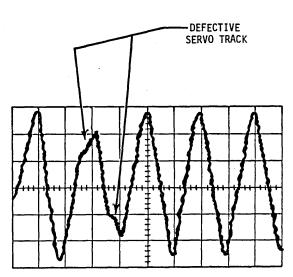

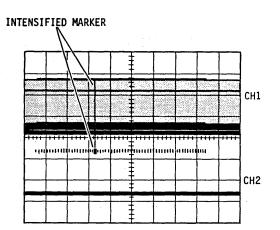

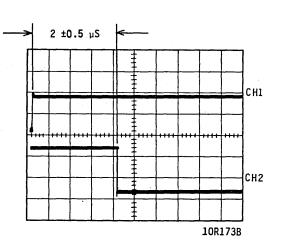

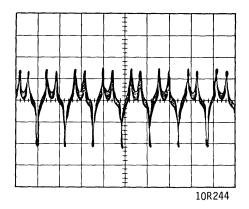

| 4-5  | Normal Servo Tracks                             | 4-15  |

| 4-6  | Defective Servo Tracks                          | 4-15  |

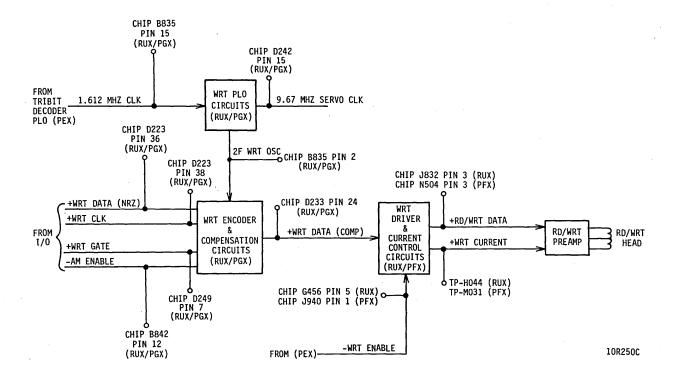

| 4-7  | Write Circuits Test Points                      | 4-16  |

| 4-8  | 1.612 MHz Clock Timing                          | 4-18  |

| 4-9  | 9.67 MHz Clock Timing                           | 4-19  |

| 4-10 | 2F Write Oscillator Timing                      | 4-19  |

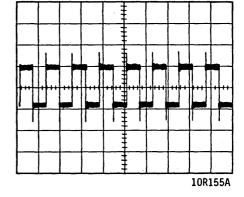

| 4-11 | Write Gate Timing                               | 4-21  |

| 4-12 | Write Data to Clock Timing                      | 4-21  |

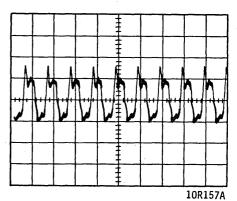

| 4-13 | Compensated Write Data Timing                   | 4-23  |

| 4-14 | Write Driver Output                             | 4-23  |

| 4-15 | Write Address Mark Timing                       | 4-24  |

| 4-16 | Write Current Timing                            | 4-25  |

| 4-17 | Read Circuits Test Points                       | 4-27  |

| 4-18 | 2F Read Oscillator Timing                       | 4-28  |

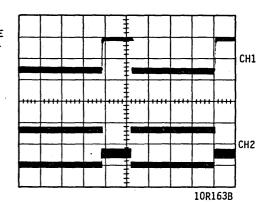

| 4-19 | Pump Up/Down Timing (Not Reading)               | 4-29  |

| 4-20 | Pump Up/Down Timing (Reading)                   | 4-29  |

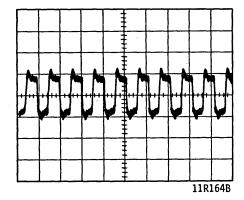

| 4-21 | Read Preamplifier Output                        | 4-31  |

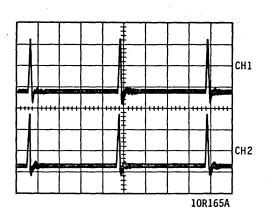

| 4-22 | Latched Read Data Timing                        | 4-31  |

| 4-23 | NRZ Read Data Timing                            | 4-33  |

| 4-24 | Read Gate to Lock to Data Timing                | 4-33  |

| 4-25 | Scope Setup for AM Found Timing                 | 4-35  |

xxii

| 4-26 | AM Found Timing                                  | 4-35 |

|------|--------------------------------------------------|------|

| 4-27 | AM to Lock To Data Timing                        | 4-37 |

| 4-28 | Index Pulse Timing                               | 4-39 |

| 4-29 | Index to Index Timing                            | 4-39 |

| 4-30 | Sector Pulse Timing                              | 4-40 |

| 5-1  | Front Panels Replacement (S/C 01)                | 5-9  |

| 5-2  | Front Panels Replacement (S/C 02 & Above)        | 5-11 |

| 5-3  | Slide Removal and Replacement                    | 5-13 |

| 5-4  | Absolute Filter Replacement and Testing          | 5-15 |

| 5-5  | Fan Removal and Replacement                      | 5-17 |

| 5-6  | Operator Panel Removal and Replacement           | 5-19 |

| 5-7  | Remote Power Supply Removal and Replacement      | 5-21 |

| 5-8  | Integral Power Supply Removal and Replacement    | 5-25 |

| 5-9  | Magnet Removal and Replacement                   | 5-29 |

| 5-10 | Coil Assembly Removal and Replacement            | 5-32 |

| 5-11 | Coil Alignment                                   | 5-33 |

| 5-12 | Carriage Removal and Replacement                 | 5-35 |

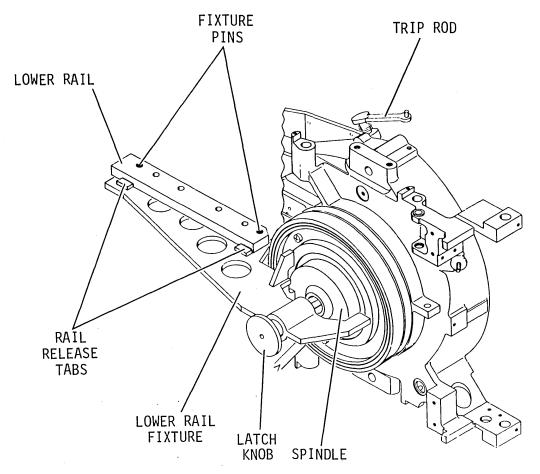

| 5-13 | Upper and Lower Rails Removal and Replacement    | 5-37 |

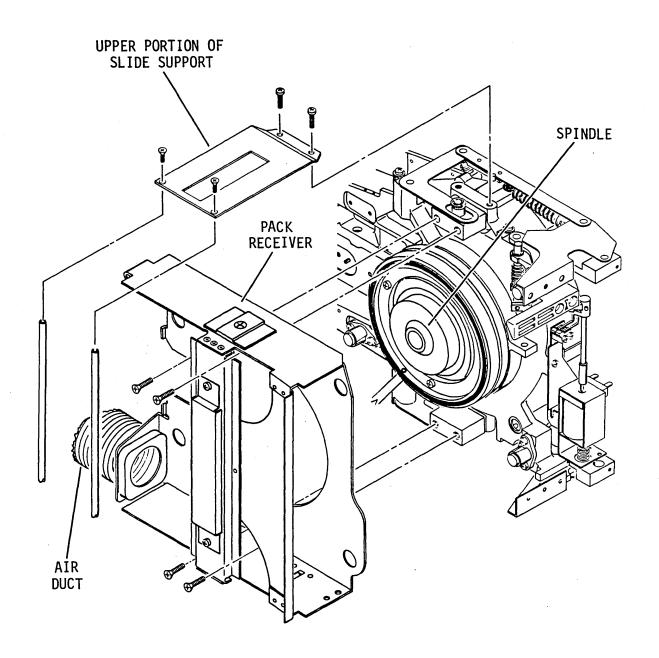

| 5-14 | Pack Receiver Removal and Replacement            | 5-38 |

| 5-15 | Lower Rail Installation                          | 5-40 |

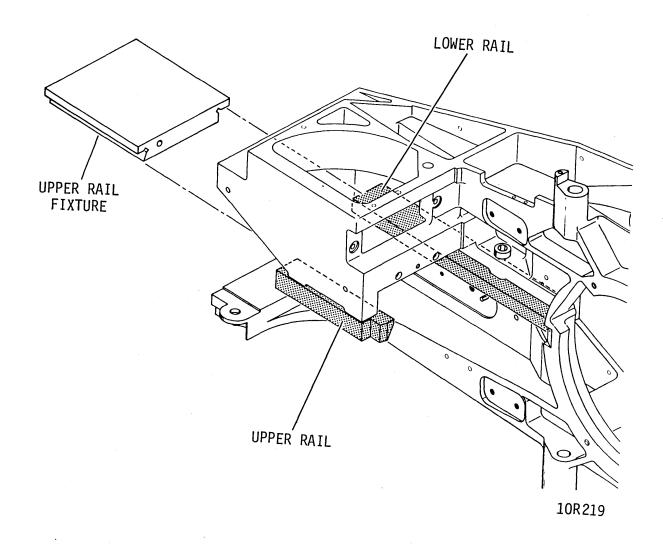

| 5-16 | Upper Rail Installation                          | 5-41 |

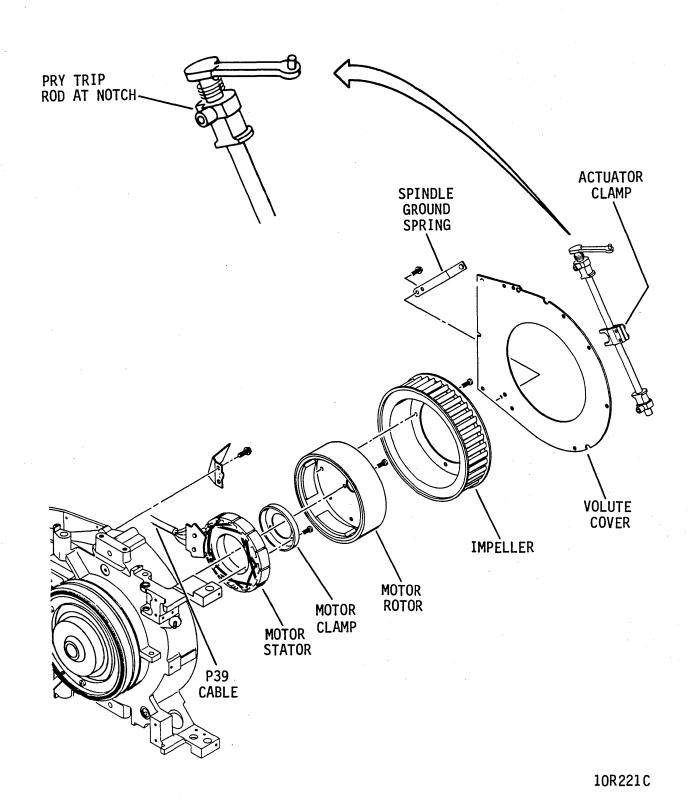

| 5-17 | Motor and Cable Assembly Removal and Replacement | 5-45 |

| 5-18 | Spindle Removal and Replacement                  | 5-49 |

| 5-19 | Spindle Lockshaft Adjustment                     | 5-51 |

| 5-20 | Head Arm                                         | 5-53 |

| 5-21 | Head Arm Removal and Replacement                 | 5-54 |

| 5-22 | Head Arm Replacement With Carriage Removed       | 5-57 |

| 5-23 | Head Alignment Setup                             | 5-61 |

| 5-24 | Head Alignment Waveform                          | 5-63 |

| 5-25 | Head Arm Alignment                               | 5-64 |

| 5-26 | Heads Loaded Switch Replacement and Adjustment   | 5-69 |

| 5-27 | Pack in Place and Write Protect Switches         | 5-71 |

83324490 G xxiii

| 5-28 | Door Unlock Solenoid Replacement and Adjustment                            | 5-75 |

|------|----------------------------------------------------------------------------|------|

| 5-29 | Door Locked Switches Replacement and Adjustment                            | 5-79 |

| 5-30 | Read/Write PLO Board (_PGX) Removal and Replacement                        | 5-81 |

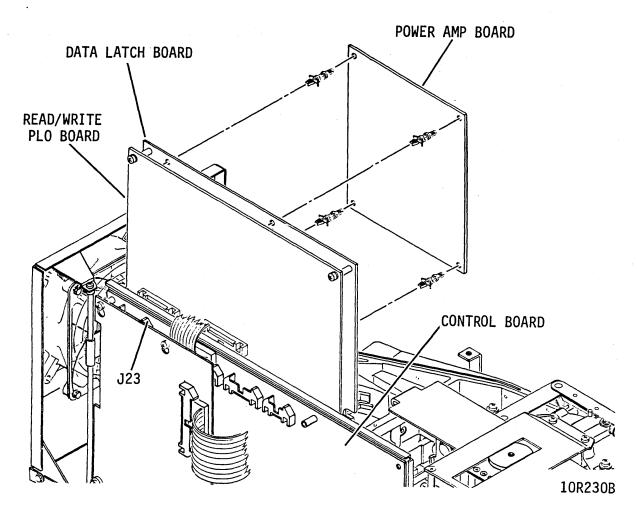

| 5-31 | Data Latch Board (_PFX) Removal and Replacement                            | 5-83 |

| 5-32 | I/O Boards (_EBN/_EDN) Removal and Replacement                             | 5-86 |

| 5-33 | Control Board (_PEX) Removal and Replacement                               | 5-89 |

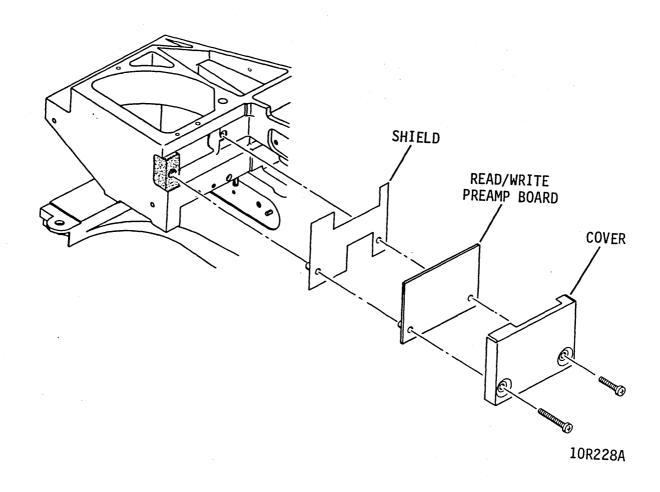

| 5-34 | R/W Preamp Board (_PCX) Removal and Replacement                            | 5-91 |

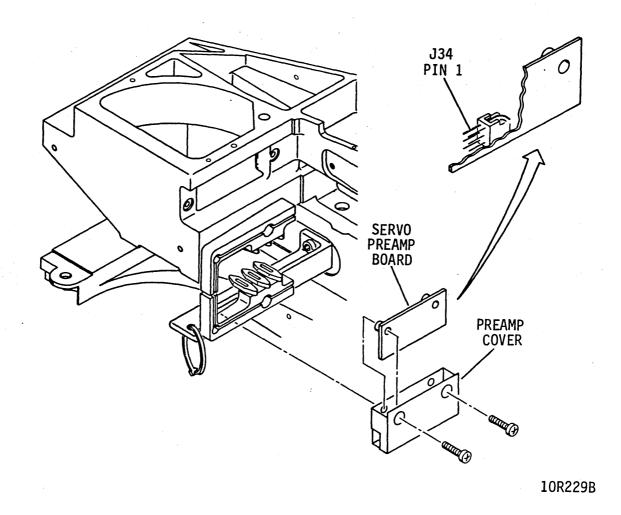

| 5-35 | Servo Preamp Board (_UUN) Removal and Replacement                          | 5-93 |

| 5-36 | Power Amp Board (_PDX) Removal and Replacement                             | 5-95 |

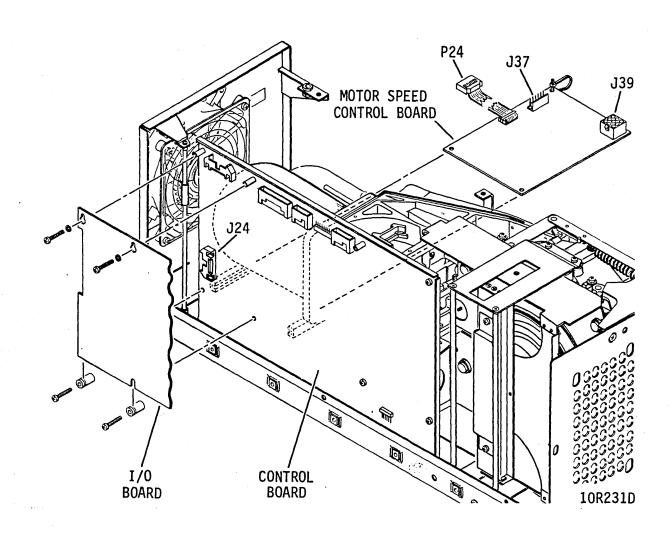

| 5-37 | Motor Speed Control Board (_PMX) Removal and Replacement                   | 5-97 |

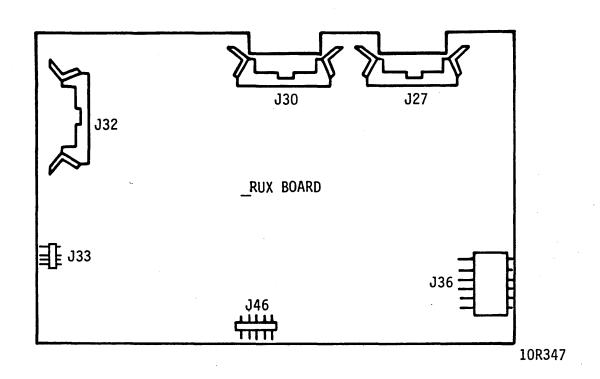

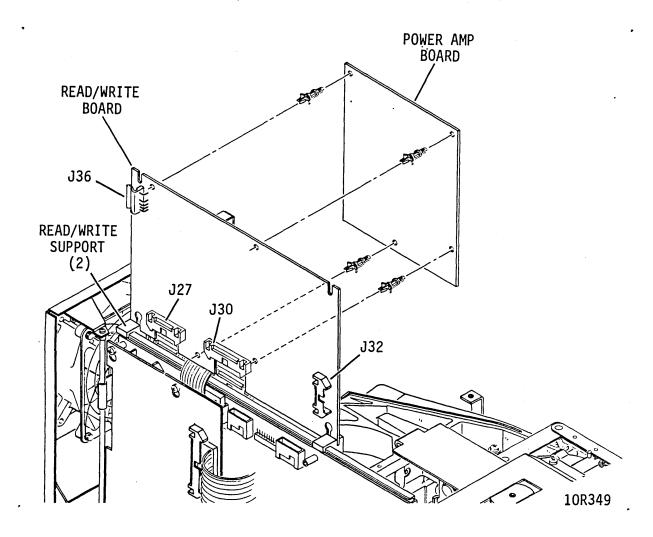

| 5-38 | Read/Write Board (_RUX) and Power Amp Board (_PDX) Removal and Replacement | 5-99 |

|      |                                                                            |      |

### **TABLES**

| 1-1 . | Interface Lines                            | 1-23  |

|-------|--------------------------------------------|-------|

| 1-2   | Dual Channel Unit Select Circuit Functions | 1-40  |

| 1-3   | Head Select Addressing                     | 1-111 |

| 1-4   | Translation Between NRZ and 2-7 Codes      | 1-114 |

| 1-5   | Write Circuit Functions                    | 1-118 |

| 1-6   | Write Compensation for Each Data Pattern   | 1-122 |

| 1-7   | Read Circuit Functions                     | 1-127 |

| 2-1   | Maintenance Tools and Materials            | 2-4   |

| 3-1   | Status Code Summary                        | 3-27  |

| 3-2   | Status Code Definitions                    | 3-36  |

| 4-1   | DC Voltage Distribution                    | 4-5   |

xxiv

### IMPORTANT SAFETY INFORMATION AND PRECAUTIONS

Proper safety and repair is important to the safe, reliable operation of this unit. Service should be done by qualified personnel only. This maintenance manual describes procedures recommended by the manufacturer as effective methods of servicing the unit. Some of these procedures require the use of specially designed tools. For proper maintenance and safety, these specially designed tools should be used as recommended.

The procedures in this maintenance manual and labels on the unit contain warnings and cautions which must be carefully read and observed in order to minimize or eliminate the risk of personal injury. The warnings point out conditions or practices that are potentially hazardous to maintenance personnel. The cautions point out practices which, if disregarded, could damage the unit and make it unsafe for use.

For the safety of maintenance and operating personnel, the following precautions must be observed:

- Perform all maintenance by following the procedures given in this manual and using only CDC/MPI replacement parts.

- Read and observe all cautions and warnings provided in the procedures and labeled on the unit.

- Use the special tools called out in the maintenance procedure.

- Observe sound safety practices when performing maintenance.

- Use caution when troubleshooting a unit that has voltages present. Remove power from unit before servicing or replacing components.

- Wear safety glasses when servicing units.

- Wear safety shoes when removing or replacing heavy components.

It is also important to understand that these warnings and cautions are not exhaustive. The manufacturer could not possibly know, evaluate and advise maintenance personnel of all conceivable ways in which maintenance might be performed or the possible risk of each maintenance technique. Consequently, the manufacturer has not completed any such broad evaluation. Thus, any persons who use any non-approved maintenance procedure or tool must first satisfy themselves that neither their safety nor the unit performance will be jeopardized by the maintenance techniques they select.

83324490 F xxv

### **ABBREVIATIONS**

| A    | Ampere                     | CLK   | Clock                       |

|------|----------------------------|-------|-----------------------------|

| ABV  | Above                      | CLR   | Clear                       |

| ac   | Alternating Current        | cm    | Centimeter                  |

| ADD  | Address                    | CNTR  | Counter                     |

| ADDR | Address                    | COMP  | Comparator                  |

| ADJ  | Adjust                     | CONT  | Control                     |

| ADRS | Address                    | CONTD | Continued                   |

| AGC  | Automatic Gain Control     | CT    | Center Tap                  |

| ALT  | Alternate                  | CYL   | Cylinder                    |

| AM   | Address Mark               | D/A   | Digital to Analog           |

| AME  | Address Mark Enable        | dc    | Direct Current              |

| AMP  | Amplifier, Ampere          | DET   | Detect                      |

| ASSY | Assembly                   | DIFF  | Differential                |

| BLW  | Below                      | DIV   | Division                    |

| С    | Celsius                    | DLY   | Delay                       |

| СВ   | Circuit Breaker            | DRVR  | Driver                      |

| CDA  | Complete Drive<br>Assembly | ECL   | Emitter Coupled Logic       |

| CDC  | Control Data Corporation   | ECO   | Engineering Change<br>Order |

| СН   | Channel                    | EN    | Enable                      |

| СНК  | Check                      | ENBL  | Enable                      |

83324490 F

xxvii

# ABBREVIATIONS (Contd)

| EXT   | External            | IND    | Index                          |

|-------|---------------------|--------|--------------------------------|

| F     | Fahrenheit, Fuse    | INTRPT | Interrupt                      |

| FCO   | Field Change Order  | I/O    | Input/Output                   |

| FDBK  | Feedback            | IPB    | Illustrated Parts<br>Breakdown |

| FIG   | Figure              | TDC    | •                              |

| FLT   | Fault               | IPS    | Inches per Second              |

| FSD   | Fixed Storage Drive | kg     | Kilogram                       |

| ft    | Foot                | kPa    | Kilopascal                     |

|       |                     | kW     | Kilowatt                       |

| FTU   | Field Test Unit     | 1b     | Pound                          |

| FWD   | Forward             | lbf    | Pounds/Force                   |

| GND   | Ground              | LED    | •                              |

| HD    | Head                |        | Light Emitting Diode           |

| HEX   | Hexagon             | LSI    | Large Scale<br>Integration     |

| Hg    | Mercury             | LTD    | Lock to Data                   |

| HR    | High Resolution     | m      | Meter                          |

| HYST  | Hysteresis          | MAX    | Maximum                        |

| Hz    | Hertz               | MB     | Megabyte                       |

| IC    | Integrated Circuit  | MEM    | Memory                         |

| IDENT | Identification      | MHz    | Megahertz                      |

| in    | Inch                | mm     | Millimeter                     |

# ABBREVIATIONS (Contd)

|           | MPI                 | Magnetic Peripherals,<br>Inc. | PROG         | Programmable               |

|-----------|---------------------|-------------------------------|--------------|----------------------------|

| MPU       | Microprocessor Unit | PS                            | Power Supply |                            |

|           |                     |                               | PWR          | Power Supply               |

| MRK<br>ms |                     | Mark<br>Millisecond           | RCVR         | Receiver                   |

|           |                     |                               | RD           | Read                       |

| ,         | MTR                 | Motor                         | RDY          | Ready                      |

|           | mV                  | Millivolt                     | REF          | Reference                  |

| ٠         | N                   | Newton                        |              |                            |

|           | NC                  | No Connection                 | REQ          | Request                    |

|           | NORM                | Normal                        | RES          | Resolution                 |

| 1         | NRZ                 | Non Return to Zero            | REV          | Reverse, Revision          |

|           |                     |                               | RGTR         | Register                   |

|           | ns                  | Nanosecond                    | r/min        | Revolutions Per Minute     |

| (         | oc                  | On Cylinder                   | RSD          | Removable Storage<br>Drive |

| (         | os                  | One-Shot                      |              |                            |

| (         | osc                 | Oscillator                    | RTZ          | Return to Zero             |

| 1         | P                   | Plug                          | R/W          | Read/Write                 |

| 1         | PD                  | Peak Detect                   | S            | Second                     |

|           | pF                  | Picofarad                     | S/C          | Series Code                |

| ]         | PG                  | Page                          | SEC          | Second                     |

| - 1       | РНН                 | Phillips Head                 | SEL          | Select                     |

| ]         | PLO                 | Phase Lock Oscillator         | SEQ          | Sequence                   |

| ]         | PROC                | Procedure                     | SPD          | Speed                      |

|           |                     |                               |              |                            |

83324490 G xxix

# ABBREVIATIONS (Contd)

| SS  | Sector Switch                    | M      | Watts               |

|-----|----------------------------------|--------|---------------------|

| T   | Tracks to go                     | W/     | With                |

| TF  | Thread Forming                   | W/O    | Without             |

| TIM | Timer                            | W PROT | Write Protect       |

| TP  | Test Point                       | W+R    | Write or Read       |

| TSP | Troubleshooting<br>Procedure     | W•R    | Write and Read      |

|     | Transistor-Transistor<br>Logic   | WRT    | Write               |

| TTL |                                  | XFR    | Transfer            |

| v   | Volts, Voltage                   | Ω      | Ohms                |

| Vbb | Bias Voltage                     | \$     | Hexadecimal Address |

| VCC | Bias Voltage                     | uF     | Microfarad          |

| vco | Voltage Controlled<br>Oscillator | us     | Microsecond         |

# SECTION 1

THEORY OF OPERATION

#### **INTRODUCTION**

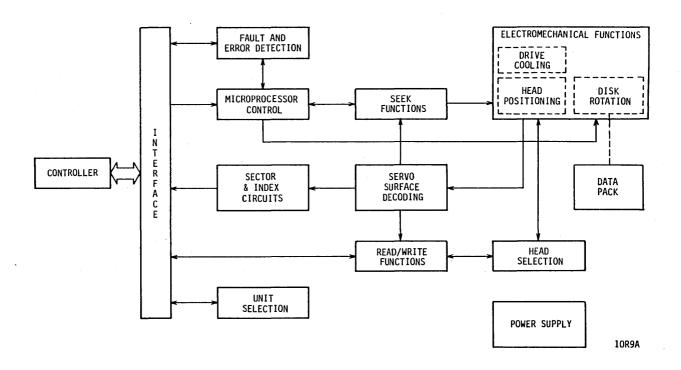

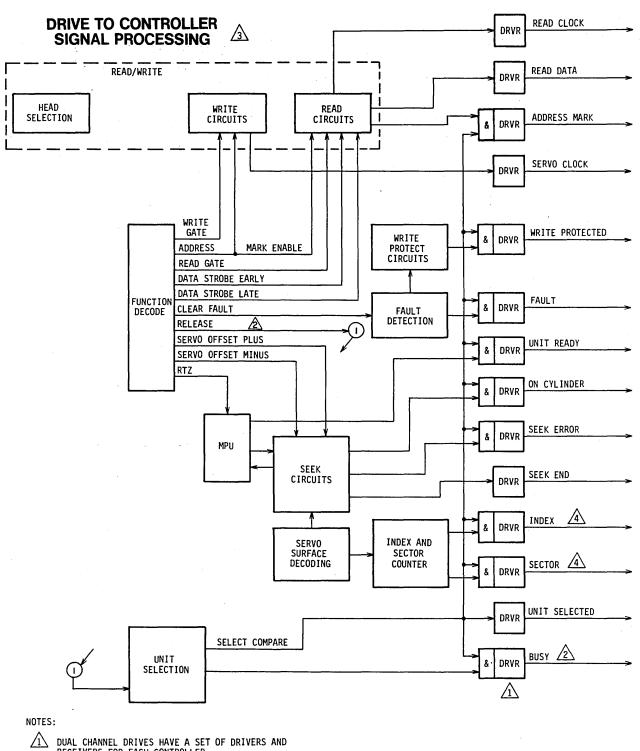

The theory of operation section describes drive operations and the hardware used in performing them. It is divided into the following major areas (refer to figure 1-1):

- Power Functions Describes how the drive provides the voltages necessary for drive operation.

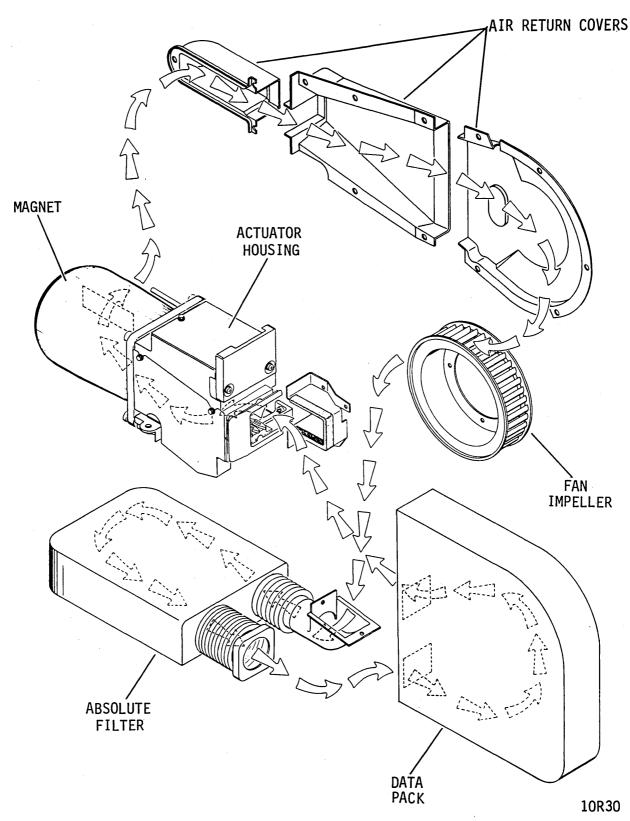

- Electromechanical Functions Provides a physical and functional description of the mechanical and electromechanical portions of the drive disk rotation, head positioning, and air flow systems.

Figure 1-1. Drive Functional Block Diagram

83324490 G

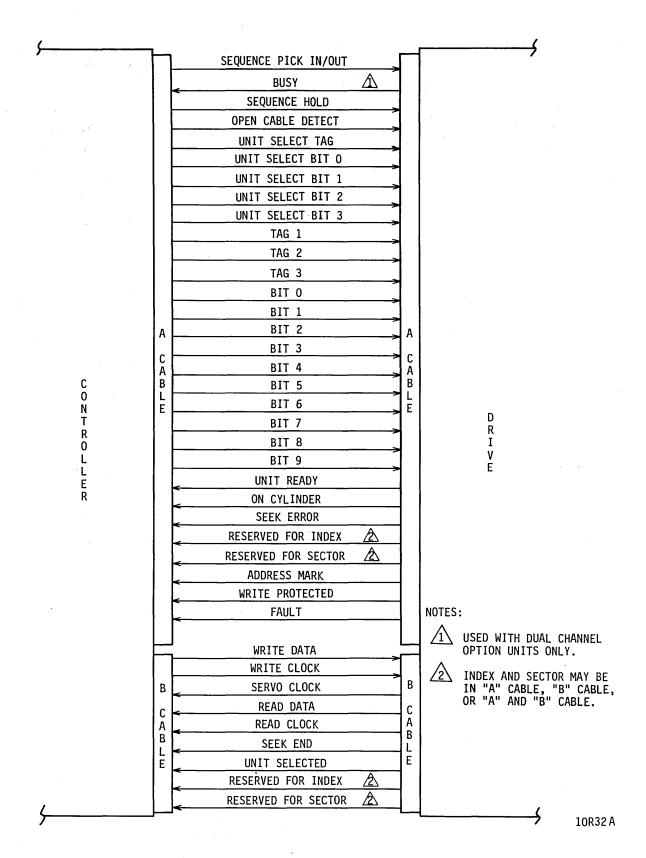

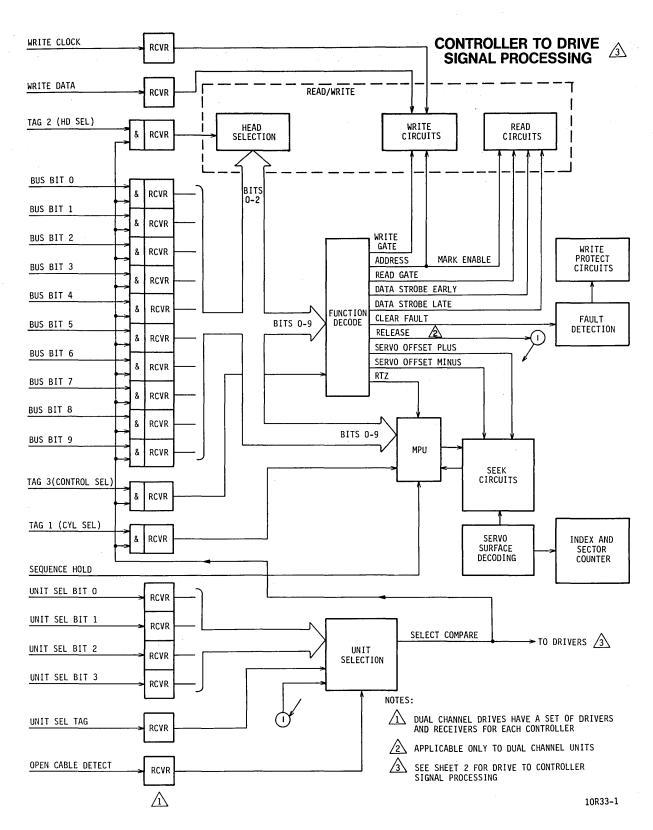

- Interface Describes the signal lines connecting the drive and controller. It also describes the I/O signals carried by these lines and how they are processed by the drive logic.

- Unit Selection Explains how the controller logically selects the drive so the drive will respond to controller commands.

- Servo Surface Decoding Explains how the decoding of the data read from the servo surface by the servo head is used to locate the radial position of the heads during a seek movement, the rotational position of the disks (indicated by the Index signal) when the heads are on track, and the exact speed of the disks (indicated by the 1.612 MHz clock signal).

- Sector Detection Explains how the drive derives the sector pulses that are used to determine the angular position, with respect to index, of the read/write heads.

- Seek Functions Explains how the servo logic controls the movements of the head positioning mechanism in positioning the heads over the disks.

- Head Selection Explains the head selection process.

- Read/Write Functions Describes how the drive processes the data that it reads from and writes on the disk.

- Fault Detection Describes the conditions that the drive interprets as faults.

The descriptions in this section are limited to drive operations only. In addition, they explain typical operations and do not list variations or unusual conditions resulting from unique system hardware or software.

Functional descriptions are frequently accompanied by simplified logic and timing diagrams. These are useful both for instructional purposes and as an aid in troubleshooting. However, they have been simplified to illustrate the principles of operation. Therefore, the diagrams (and timing generated from them) in volume 3 of the hardware maintenance manual should take precedence over those in this section if there is a conflict between the two.

The four digit numbers in parentheses that are used on the simplified logic and flowcharts are logic diagram cross reference numbers. They indicate the logic page(s) where the function or operation can be found.

#### **POWER FUNCTIONS**

#### **GENERAL**

Power functions are processes that take place within the power supply and the drive when the drive is powered up and powered down. These processes depend on whether the drive is set up for local or remote operation. In all cases, the power up and power down sequences are controlled through MPU programming that monitors whether start conditions are present and whether certain interlock and operating conditions are satisfactory. The following areas of the power functions will be discussed in detail:

- Power Distribution -- Describes how power is distributed to the drive circuitry.

- Local/Remote Power Sequencing -- Explains how the drive may be powered up either at the drive or by the controller.

- Power On Sequence -- Describes how the drive circuitry is initialized when power is applied and how the drive is prepared for normal operation.

- Power Off Sequence -- Describes how the drive is powered down, including unloading the heads and stopping the disk rotation.

#### **POWER DISTRIBUTION**

The power supply provides the drive with basic dc supply voltages when circuit breaker CBl is placed in the ON position. The drive itself has no ac power requirements. All drive circuitry, including the electronics, cooling fan, and drive motor, is operated with the dc supply voltages. The ac power cable connects the power supply (through CBl) to site ac power. The power supply can be conditioned for operation with any standard ac input voltage, as described in the Installation and Checkout section of Hardware Maintenance Manual, Volume 1.

The dc power cable connects the power supply to the drive. When CBl is ON, this cable transmits four basic dc supply voltages to the drive electronics. These voltages are +5 V, -5 V, +24 V, and -24 V. The -5, -24, and +24 V supplies are protected against overload by pop-out circuit breakers on the power supply. The dc power cable also contains signal lines, which are enabled by control circuitry in the drive, to switch on 40 V dc power to the drive motor and produce disk rotation.

83324490 F 1\_3

There are secondary power supplies on the drive's Control Board that develop additional bias voltages for certain integrated circuits. One supply steps down the +24 V input and develops a regulated +15 V source. Another supply steps down the -24 V input and develops a regulated -15 V source. A third supply steps down the -15 V supply to develop a regulated bias of -8.3 V for the servo preamp chip.

The drive has circuitry that monitors the various supply voltages and disables write and/or servo functions when dc power is unreliable. For more information about voltage faults, refer to the Fault and Error Conditions discussion.

#### LOCAL/REMOTE POWER SEQUENCING

The local/remote feature selects whether or not the controller can control starting and stopping the drive motor. Part of drive installation is setting the LOCAL/REMOTE switch (on the drive I/O Board) for either local or remote operation. The LOCAL/REMOTE switch setting determines start conditions for the drive motor during power up. With the LOCAL/REMOTE switch in LOCAL, start conditions require only that the START switch is in the On position. With the LOCAL/REMOTE switch in REMOTE, start conditions require that the START switch is in the On position and that the controller has activated the Sequence Hold signal.

In a system of several drives set up for remote operation, the Sequence Hold command affects all drives simultaneously. When Sequence Hold goes active, it enables all drives to start their drive motors at the same time. When Sequence Hold goes inactive, it causes all drives to stop their drive motors at the same time.

#### **POWER ON SEQUENCE**

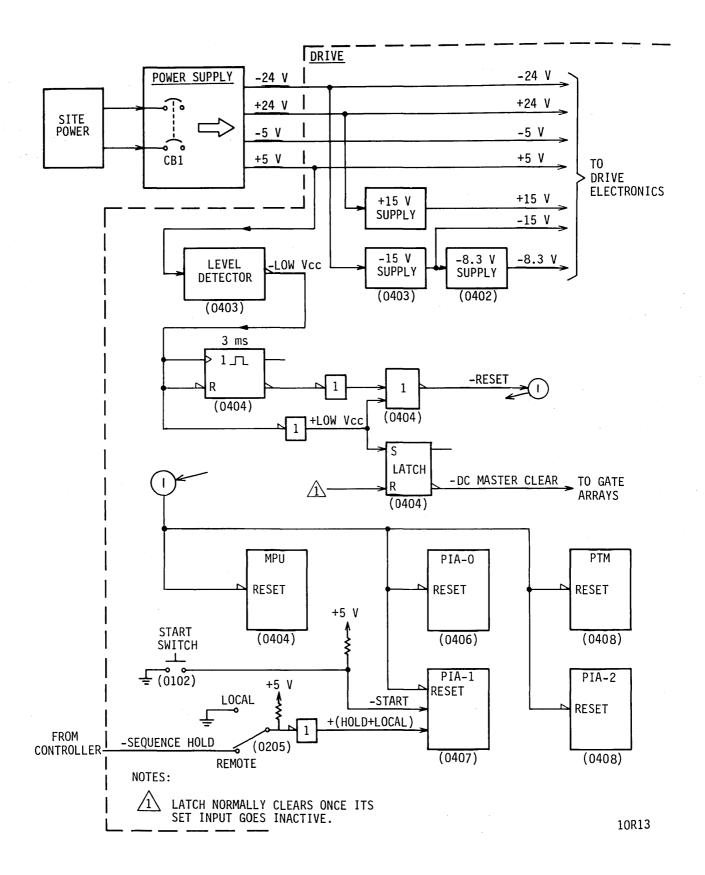

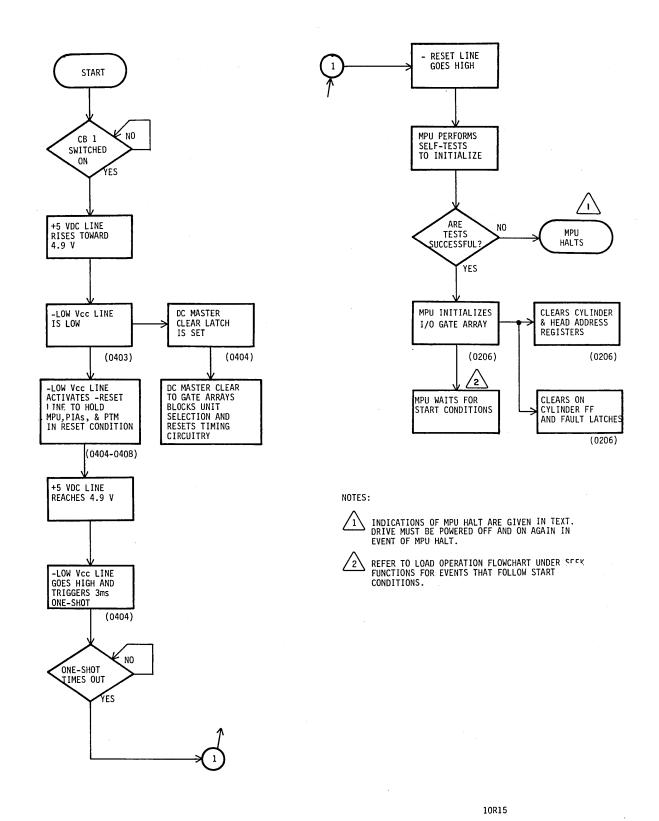

The power on sequence takes place in two steps. Power on initialization occurs when dc power is applied to the drive. Following successful initialization, a load operation occurs each time that start conditions become available. Figure 1-2 is a simplified diagram of the power on circuitry, and figure 1-3 is a flowchart of the sequence. The following paragraphs describe power on initialization in detail and summarize the load operation. More information about load operations is given under Seek Functions.

1-4

Figure 1-2. Power On Circuitry

Figure 1-3. Power On Sequence Flowchart

Placing power supply circuit breaker CBl ON enables dc power to the drive. A level detector on the Control Board monitors the +5 Vdc input from the power supply and sets the -Low Vcc line high when this input reaches +4.9 V. Until this time, the DC Master Clear latch is set, and its output, the -DC Master Clear signal, remains low. In the Sector Counter Gate Array, the low -DC Master Clear signal resets the sector counter and the servo pattern decode circuitry. In the Address Decode Gate Array, the low -DC Master Clear signal disables the interface by blocking unit selection, and it resets timing circuitry that develops Index and Cylinder pulses. In dual channel drives, the low -DC Master Clear signal blocks unit selection by either controller.

The -Reset line to the MPU goes low when -DC Master Clear goes low, and it is held low by a one-shot for about 3 ms after the -Low Vcc line goes high. When -Reset goes high, the MPU performs three self-test operations to initialize itself. These tests are as follows:

- The MPU performs a checksum calculation on the ROM contents. This test validates that the MPU's firmware instructions are readable.

- The MPU tests its internal RAM by writing information into it and reading it back.

- The MPU initializes its PIAs by sending data to them and reading it back.

If the first two tests fail, the MPU halts and all the individual fault LEDs on the Control Board remain lit. If the third test fails, the MPU tries to light the First Seek LED and halts. None of these tests can produce an operating panel FAULT indication, and there is no way to clear these faults except for turning CBl OFF.

With the self-tests complete, the MPU initializes the circuitry within the I/O Gate Array. The MPU communicates with the I/O Gate Array via I/O Control lines 1, 2, and 3. The MPU pulses I/O Control lines 1 and 2 with a serial code that clears the Cylinder Address register (CAR), the Head Address register (HAR), the On Cylinder FF, and the Fault latches.

The MPU requires that the drive motor is stopped and the heads are unloaded prior to unlocking the front door. To do this, it checks motor speed by counting -Motor Sensor pulses with the PTM #3 counter and looks at the -Heads Loaded Switch line at PIA-1. If these checks are satisfactory, the MPU issues the Unlock Door command at PIA-1 to energize the Door Unlock Solenoid, allowing the door to be opened for installing or exchanging disk packs.

At this point, power on initialization is complete. This process will not be repeated until dc power is removed and reapplied to the drive (via CB1). The MPU waits for start conditions by monitoring the START switch and (in remote operation) the Sequence Hold signal from the controller.

When start conditions are present, the MPU directs the load operation. The load operation energizes the drive motor to bring the disks up to speed and loads the heads to position them over the disks at track 0. Details of the load operation are given under Seek Functions. When the load operation is complete, the drive waits for commands from the controller.

#### **POWER OFF SEQUENCE**

The power off sequence unloads the heads and stops the drive motor. There are two conditions that initiate a power off sequence. One is a loss of start conditions, and the other is a loss of dc power to the drive. Both conditions produce retract operations: the first, a normal retract; and the second, an emergency retract. These retract operations are discussed in detail under Seek Functions. The drive motor comes to a stop after the retract is completed. The following paragraphs describe both types of power off sequences.

A loss of start conditions occurs when the START switch is pressed to release it from the Start position or (in remote operation) when the controller deactivates Sequence Hold. The MPU monitors the start conditions and commands a normal retract when they are removed. The MPU issues the -Retract command to withdraw the heads from the disk pack under servo control. When the heads are fully retracted, the contacts on the Heads Loaded switch open, indicating to the MPU that the retract is complete. The MPU then drops the Motor Run command to disable the Motor Speed Control, and dynamic braking stops the drive motor. The MPU monitors drive motor speed by counting -Motor Sensor pulses and issues the Unlock Door command at PIA-1 when the motor has stopped. This energizes the Door Unlock Solenoid, allowing the door to be opened for disk pack removal. The drive remains in this condition until start conditions reappear.

A loss of dc power results when power supply circuit breaker CBl is switched OFF or when there is a loss of site ac power. When the dc voltages drop, an emergency retract takes place under hardware control. The emergency retract operation requires no MPU intervention, and it uses voltage generated by the decelerating drive motor to drive the heads outward to the unloaded position. With a loss of dc power, the drive motor coasts to a stop.

1-8 83324490 A

## **ELECTROMECHANICAL FUNCTIONS**

#### GENERAL

Certain drive functions are a result of the electromechanical devices using drive power and working under the control of drive logic circuitry. These functions include disk rotation, head positioning, and drive cooling and ventilation.

## **DISK ROTATION**

#### General

Disk rotation is accomplished by an electromechanical system that engages the disks to the spindle during data pack installation, accelerates the disks to 3600 r/min during power up, stops disk rotation with dynamic braking during power down, and disengages the disks from the spindle during data pack removal. The mechanical and electrical aspects of this system are discussed in the following paragraphs.

## **Mechanical Description**

The mechanical components used for disk rotation are a linkage system that engages and disengages the disks and the spindle, and a drive motor that rotates the disks.

# Pack and Spindle Linkage

The pack and spindle linkage is controlled by opening and closing the front door during data pack installation and removal. When an operator closes the front door after inserting a data pack in the drive, several things happen. One set of levers moves the data pack toward the spindle, and the shaft on the disk hub enters the spindle receptacle. A second set of levers activates a bayonet lock within the spindle receptacle, which locks the shaft on the disk hub to the spindle and allows the spindle to rotate the disk hub. Interlock switches sense whether the door is locked and whether a data pack is in place; these interlock conditions must be satisfied before the powering up the drive motor is enabled.

The front door is locked by a solenoid while the disks are rotating. However, when the disks are not rotating, opening the door operates the two sets of levers with the following results. The bayonet lock in the spindle releases the shaft on

the disk hub, and the pack receiver moves the data pack away from the spindle until it lines up with the front door opening. The pack retainer releases the data pack from the pack receiver so that it can be removed from the drive.

# Drive Motor

The drive has a direct drive system for disk rotation with the drive motor mounted concentrically on the spindle. The motor has a three-phase stator surrounded by a four-pole rotor. The motor speed control (described in the next topic) provides pulsed excitation to the three stator windings. To keep the stator pulses in phase with rotor position, the speed control uses feedback from sensors located in the motor. These sensors employ the Hall Effect to sense flux reversals from the rotor magnets. As the rotor magnets pass each sensor, its output line toggles.

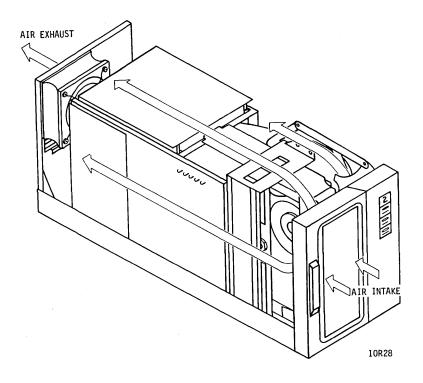

In addition to rotating the disks, the drive motor produces air flow through the data pack and positioner assembly. Air flow is circulated in a closed loop by an impeller attached to the rotor of the drive motor (see Air Flow System discussion).

# **Electrical Description**

## General

Electrical operation of the drive motor is discussed in two functional areas:

- Motor Control System -- discusses how the drive motor is started and how its speed is regulated.

- Dynamic Motor Braking -- discusses how the drive motor is decelerated and the front door is unlocked.

## Motor Speed Control

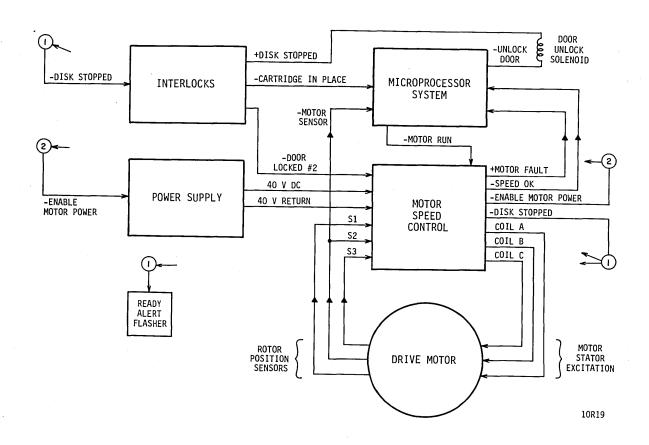

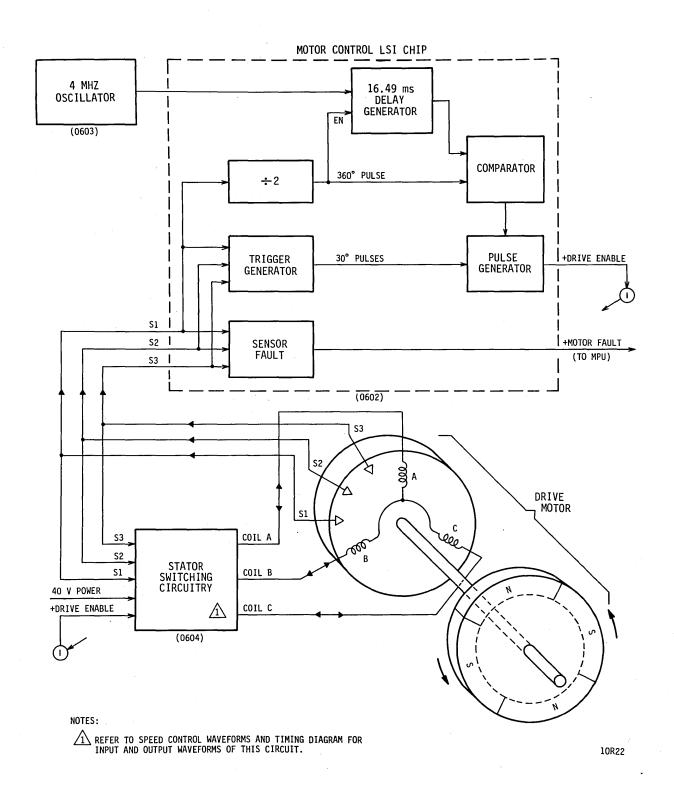

The motor speed control regulates operation of the drive motor. Subject to interlocks, the microprocessor issues a command to start the drive motor during the power on sequence (see Power On Sequence discussion). The motor speed control activates the 40 V dc output of the power supply and uses this power source to excite the stator windings in the drive motor. The control and status lines between these system elements are shown in figure 1-4.

1-10 83324490 A

Figure 1-4. Motor Speed Control System Diagram

To start the drive motor, the microprocessor drops the -Motor Run line. The drive motor receives power as long as this line is held low. With the -Motor Run and the -Door Locked #2 lines low, the motor speed control issues the -Enable Motor Power command to switch on the 40 V dc output of the power supply.

The motor speed control divides each shaft rotation of the motor into twelve 30° segments. During each segment, a current path is selected through two of the three stator coils. These stator excitations are timed so that, in each segment, the selected stators exert a counterclockwise torque on the permanent magnets of the rotor.

83324490 E 1-11

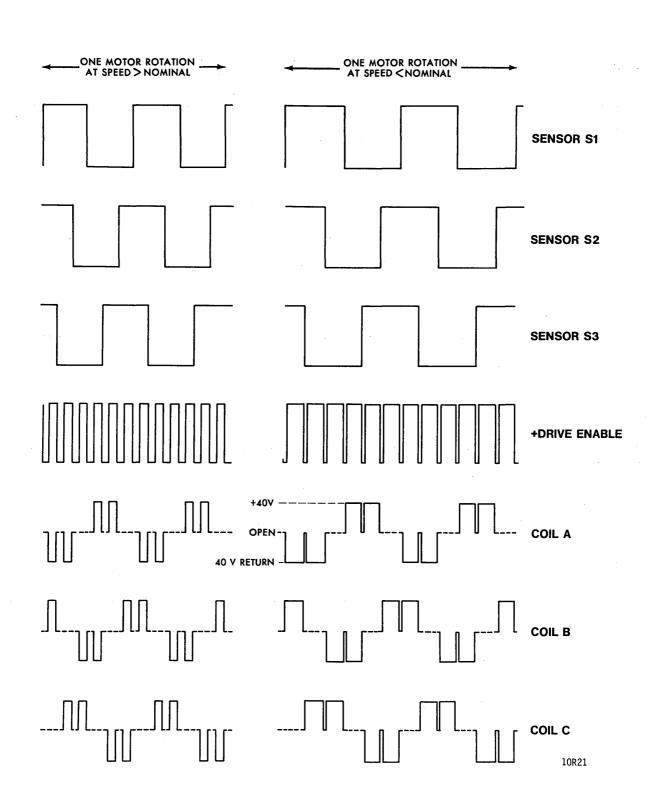

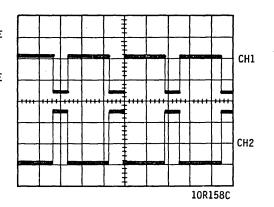

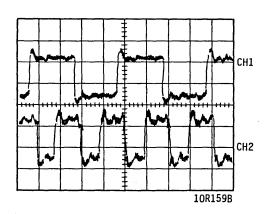

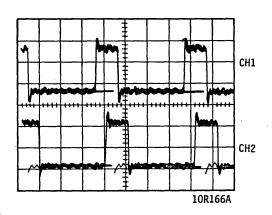

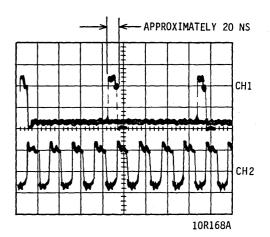

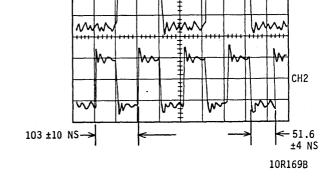

Rotational position of the motor shaft is relayed to the motor speed control by sensors S1, S2, and S3 located inside the motor. The sensors are positioned at 30° intervals. Each sensor employs the Hall Effect to output a digital level that switches when the polarity of the local magnetic field reverses. The waveforms of S1, S2, and S3 are shown in figure 1-5.

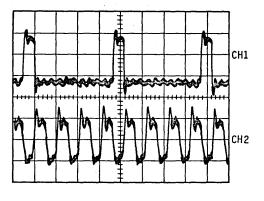

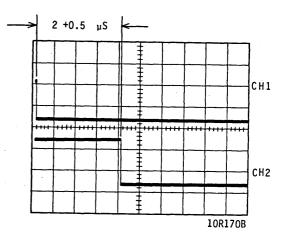

The motor speed control regulates motor speed by modulating the width of the pulses applied to the stator coils. The motor speed is kept within the following range: 3564 r/min (16.83 ms/rev) to 3636 r/min (16.49 ms/rev). The pulses have maximum width until the rotation time decreases to 16.83 ms. Then the pulse width decreases linearly to a near-zero value corresponding to a rotation time of 16.49 ms.

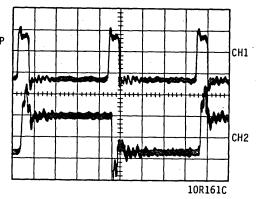

Figure 1-6 shows simplified logic for the motor speed control. The control modulates the motor pulses as follows: rotation, a signal called +360° Pulse goes active. This signal triggers a 16.49 ms reference delay, derived by subdividing the 4 MHz clock in the motor speed control. This reference delay corresponds to one motor rotation at the maximum allowable A comparator circuit outputs a pulse that is active speed. end of the reference delay until the next The active time for the comparator output pulse determines the on-time of the +Drive Enable line during each 300 segment of motor rotation. Power is applied to the stator windings only when +Drive Enable is high. This condition is updated once per motor rotation, and the duty cycle of the motor is readjusted to keep the motor speed within its specified range.

Three status outputs are generated by the motor speed control and are used as follows:

- +Motor Fault -- indicates to the MPU that the drive motor has a bad magnetic sensor.

- -Speed OK -- indicates to the MPU that the drive motor speed is between 3564 and 3636 r/min and that no motor fault is present.

- -Disk Stopped -- indicates to the interlock circuitry that the last disk rotation exceeded two seconds.

## Dynamic Motor Braking

Dynamic motor braking decelerates the drive motor during a power off sequence. Dynamic braking occurs when power is

1-12 83324490 F

Figure 1-5. Speed Control Waveforms and Timing

83324490 A

Figure 1-6. Motor Speed Control Simplified Logic

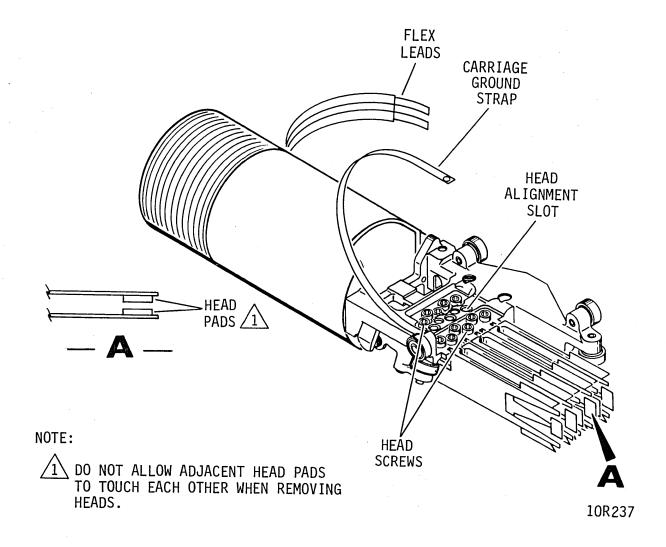

removed from the drive motor. As the motor continues to rotate, it acts as a generator. The generated current is dissipated in a resistive load, converting the rotational energy into heat.