## NOTEDS REFERENCE MANUAL NORD-10

**Test and Debugging System**

### A/S NORSK DATA-ELEKTRONIKK

## NOTEDS REFERENCE MANUAL NORD-10

**Test and Debugging System**

|   |  | 9   |

|---|--|-----|

|   |  | 2   |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  | 0   |

|   |  |     |

|   |  | 10. |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  |     |

|   |  | 2   |

|   |  | ь   |

|   |  |     |

|   |  |     |

|   |  |     |

| 9 |  |     |

|   |  |     |

# REVISION RECORD Notes Revision 1/74 Original Printing

ND-62.004.01 January 1974

#### TABLE OF CONTENTS

+++

| Chapters                                                                                        |                                                                                                                 | Page                                                        |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1                                                                                               | INTRODUCTION                                                                                                    | 1-1                                                         |

| 2                                                                                               | HOW TO USE THIS MANUAL                                                                                          | 2-1                                                         |

| 3                                                                                               | HARDWARE                                                                                                        | 3-1                                                         |

| 3.1<br>3.2                                                                                      | Introduction Test Driver Card (TDC)                                                                             | 3 <b>-1</b><br>3 <b>-</b> 3                                 |

| 3.2.1<br>3.2.2<br>3.2.3                                                                         | Load most significant MIR<br>Load least significant MIR<br>Write Test Status                                    | 3 -3<br>3 -3<br>3 -3                                        |

|                                                                                                 | TMODE EWBUS FLICK OPINT ROMDR BUSDR SCOPE MCLIR STOP Timing                                                     | 3-3<br>3-4<br>3-4<br>3-4<br>3-4<br>3-4<br>3-4<br>3-4        |

| 3.2.4<br>3.2.5<br>3.2.6<br>3.2.7                                                                | Write to Bus Buffer Register Read Micro Program Counter Read Memory Address Read Test Status                    | 3-5<br>3-5<br>3-5<br>3-5                                    |

| 3.2.7.1<br>3.2.7.2<br>3.2.7.3<br>3.2.7.4<br>3.2.7.5<br>3.2.7.6<br>3.2.7.7<br>3.2.7.8<br>3.2.7.9 | ROM out of Range Read Request Write Request Fetch Request Indirect Request Memory out of Range STOP TRA 0 TRR 0 | 3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-6<br>3-6<br>3-6<br>3-6 |

| 3.2.8                                                                                           | Read CUT IB-bus                                                                                                 | 3-6                                                         |

| 3.3<br>3.4<br>3.5                                                                               | Test Connector Card (TCC) Test System Card (TSC) ROM Simulator Card (RSC)                                       | 3-6<br>3-7<br>3-7                                           |

| 3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.5.6<br>3.5.7<br>3.5.8                            | FLICK SMEM ROOR SKPE ROMDRY ROMSKPE DSKPE ERR                                                                   | 3-9<br>3-9<br>3-9<br>3-9<br>3-9<br>3-9<br>3-10              |

| Chapters                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page:                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 4                                                                                                                                                             | TEST SYSTEM USAGE                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-1                                                                                                                 |

| 4.1                                                                                                                                                           | Test System Monitor Commands                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-1                                                                                                                 |

| 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7<br>4.1.8<br>4.1.9<br>4.1.10<br>4.1.11<br>4.1.12<br>4.1.13<br>4.1.14                               | A - Call Assembler B - Back, restart current Test C - Continue current Test D - Debug, Register examine/deposit L - List tests in Program Table M - Master Clear N - Start next Test in Table P - Start previous Test in Table R - Restart at beginning of Test Table S - Step Function in current Table T - Form new Test Table U - Update Test System Parameters X - Call Simulator ! - Start specified Test                                 | 4-2<br>4-2<br>4-2<br>4-2<br>4-4<br>4-4<br>4-4<br>4-4<br>4-5<br>4-5<br>4-5<br>4-8<br>4-8                             |

| 4.2                                                                                                                                                           | Available Tests                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-9                                                                                                                 |

| $4.2.1 \\ 4.2.2$                                                                                                                                              | Standard Test Sequence (T <n>) Special Tests (TX<n>)</n></n>                                                                                                                                                                                                                                                                                                                                                                                   | 4-9<br>4-9                                                                                                          |

| 4.3                                                                                                                                                           | Setting up NOTEDS                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-14                                                                                                                |

| 5                                                                                                                                                             | SIMULATOR SUBSYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-1                                                                                                                 |

| 5.1                                                                                                                                                           | Simulator Monitor Commands                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-1                                                                                                                 |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>5.1.11<br>5.1.12<br>5.1.13<br>5.1.14<br>5.1.15<br>5.1.16<br>5.1.17 | A - Call Assembler C - Compare D - Debug, Register examine/deposit L - Load from Paper Tape M - CUT Master Clear P - Print Simulation Log S - Set Memory Mode T - Transfer to CUT Memory U - Update System Parameters X - Exit from Simulator Main Memory Break Point , - ROM Break Point / - Main Memory examine/deposit \ - ROM examine/deposit \ - Start CUT Execution f - Start CUT Execution R - Load ROM Program Ø - Exit from Simulator | 5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-4<br>5-4<br>5-4<br>5-5<br>5-5<br>5-5<br>5-7<br>5-7<br>5-8<br>5-8<br>5-9 |

| 5.2                                                                                                                                                           | ROM Program                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-9                                                                                                                 |

#### Appendices:

APPENDIX A - Error Loop Descriptions

APPENDIX B -  $\mu$ -instruction Format

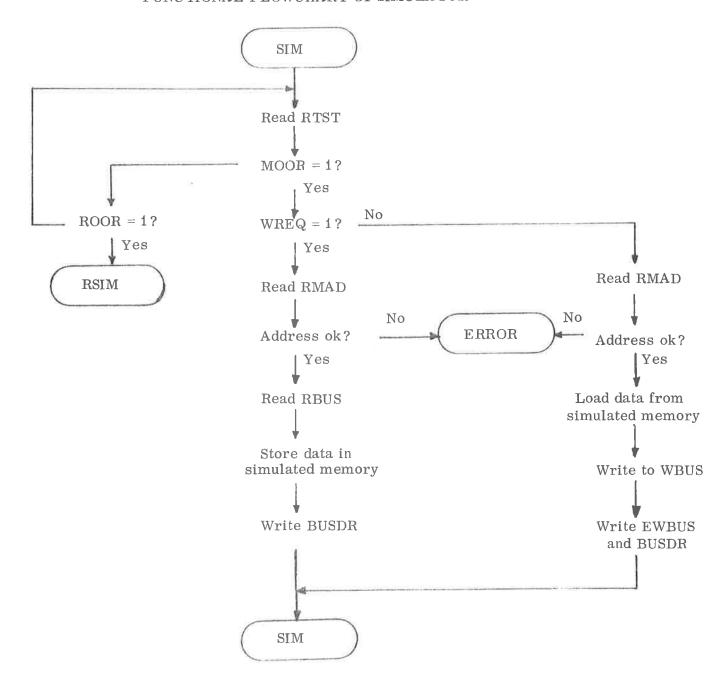

APPENDIX C - Functional Flow Chart of Simulator

#### 1 INTRODUCTION

The NORD-10 Test and Debugging System (NOTEDS) is a novel, computer-based tool for use in NORD-10 (N-10) production and maintenance. The system provides extremely accurate and powerful means for pinpointing errors in the N-10 CPU. NOTEDS rests on the idea of having one computer test another. This makes it possible to perform very extensive and systematic tests in a short period of time and still maintain an absolute accuracy in the verification of test results.

When NOTEDS discovers an error in the CPU under test (CUT), it provides all relevant data for the test in question and locks in a fixed error loop. In this loop the test conditions are kept constant and a special program-triggered signal is given once per loop. This greatly facilitates good oscilloscope triggering. A lamp is flicked on or off each time an error is detected and thus provides a visual indication as to wether the error is permanent or intermittent.

Effective use of NOTEDS is only possible if the operator has at least some knowledge of N-10 hardware. NOTEDS does not provide any information as to the exact cause of the error, it only presents the error symptoms. However, the different tests are simple and easy to comprehend. In many cases it will be possible to locate the faulty card by examination of the error printouts only. The standard test sequence is incremental in design so that only limited new hardware is tested in each test.

The design and implementation of NOTEDS were carried out in parallel with the NORD-10 prototype development. Already at this early stage NOTEDS proved its usefullness and great flexibility.

|  | ė  |

|--|----|

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  | ē  |

|  |    |

|  | 90 |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

|  | دي |

|  |    |

|  | e. |

|  |    |

|  |    |

|  |    |

|  |    |

|  |    |

#### 2 HOW TO USE THIS MANUAL

This manual is the reference manual for the NORD-10 Test and Debugging System, NOTEDS. The information contained herein will be of interest to

- 1) NORD-10 Production Engineers.

- NORD-10 Maintenance Engineers in multi-computer installations. Read Chapter 3 and 4.

- Persons making extensions to the NORD-10 micro-program. Read chapter 5.

- 4) Persons maintaining NOTEDS hardware and software.

Truely advanced use of NOTEDS will require thorough knowledge of the NORD-10 CPU, the NORD-10 micro-processor specification and this manual.

|  |  | 9   |

|--|--|-----|

|  |  |     |

|  |  | G.  |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  | V   |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  | (4) |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

|  |  |     |

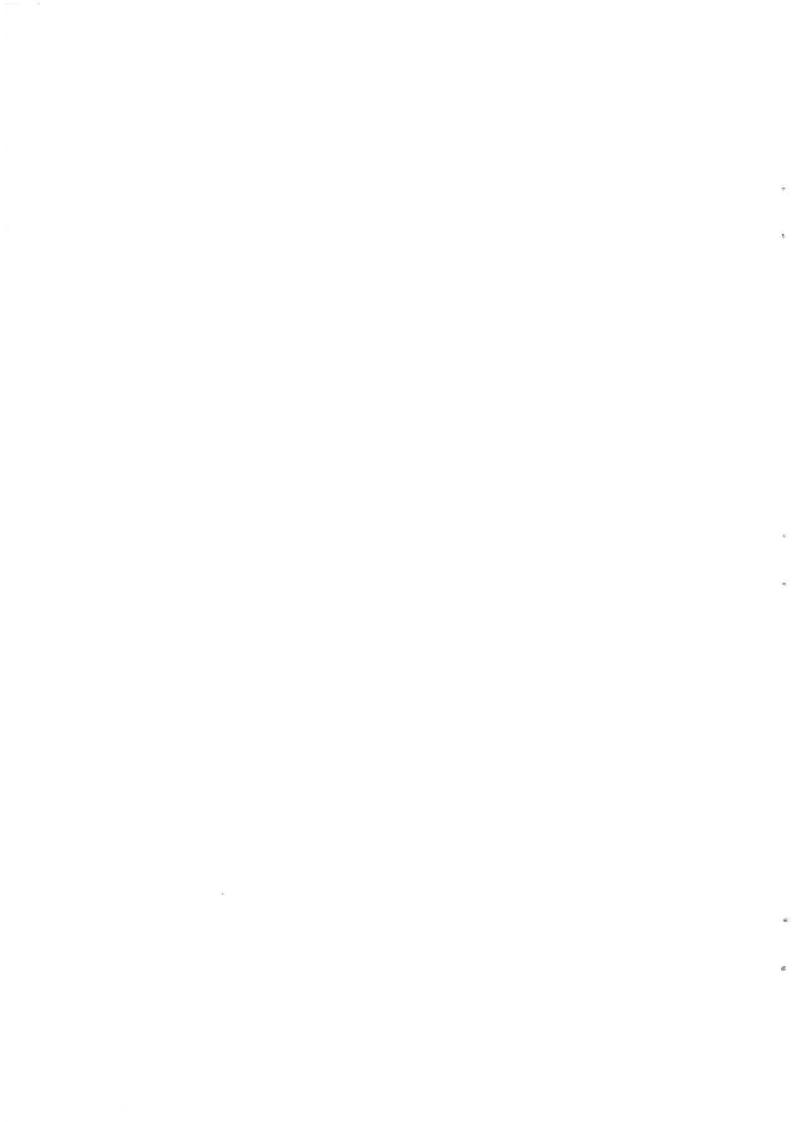

#### 3 HARDWARE

#### 3.1 Introduction

NOTEDS hardware consists of four special cards.

The Test Driver plugs into the I/O-bus of the TSC\* and accepts 8 device addresses. These addresses are fixed to  $20 - 27_8$ .

Three special cards are needed in the CUT\*\*

The Test Connector plugs into a spare memory buffer position and is connected to the Test Driver via a cable. (Slot 18.)

The Test System Card plugs into the position normally occupied by the Panel Driver. (Slot 17.)

The ROM Simulator plugs into the ROM position. (Slot 10.)

The cable normally connecting the Panel Driver position and the panel itself must be disconnected when NOTEDS is in use.

A special test bus (TW) is established between these three cards when they are plugged in. This bus is 16 bit wide with 4 additional control lines. (TWCS, TWC0-3.)

Figure 3.1 shows the special NOTEDS hardware. The interaction points with the main CUT CPU is not shown.

TSC - Test system computer

<sup>\*</sup> CUT - Computer under test

#### 3.2 Test Driver Card

The test driver card (TDC) resides in the TSC where it is connected to the I/O-bus. Its purpose is to interface the CUT to the TSC via a two-way bus (TWL).

The TDC accepts 8 device addresses:

#### 3.2.1 Load most significant MIR

IOX HMIRL

% 164023

The TSC A register is transferred to a buffer register on the RSC (refer to Section 3.5) to simulate bits 16 - 31 in the ROM.

#### 3.2.2 Load least significant MIR

IOX HMIRR

% 164021

The TSC A register is transferred to a buffer register on the RSC (refer to Section 3.5) to simulate bits 0 - 15 in the ROM.

#### 3.2.3 Write Test Status

IOX HWTST

% 164025

The TSC A register is transferred to the test system control register. The control word has the following format:

| 1 | 5 | 14 | 13               | 12               | 11      | 10                    | 9                     | 8         | 7 | 6                     | 5 | 4                     | 3 | 2 | 1 | 0                     |

|---|---|----|------------------|------------------|---------|-----------------------|-----------------------|-----------|---|-----------------------|---|-----------------------|---|---|---|-----------------------|

|   |   |    | S<br>T<br>O<br>P | M<br>C<br>L<br>I | S COP E | B<br>U<br>S<br>D<br>R | R<br>O<br>M<br>D<br>R | O P I N T |   | F<br>L<br>I<br>C<br>K |   | E<br>W<br>B<br>U<br>S |   |   |   | T<br>M<br>O<br>D<br>E |

Figure 3.2

WTST Format

#### 3.2.3.1 TMODE

This bit defines the mode of operation of the ROM simulator. If TMODE = 1; the real ROM\* will be enabled in the 1/2K address space defined on the RSC (normally 0 - 1/2K). Refer to Section 4.1.12.

<sup>\*</sup> Real ROM is an option to NOTEDS

#### 3.2.3.2 EWBUS

This bit enables the WBUS register onto the CUT IB-bus. (Refer to Section 3.2.3.10.)

#### 3.2.3.3 FLICK

Each time FLICK = 1 two LED's on the RSC is flicked. This is used to signal an error in the test loop.

#### 3.2.3.4 OPINT

OPINT = 1 simulates an operator's panel interrupt.

#### 3.2.3.5 ROMDR

ROMDR = 1 gives a data-ready pulse signalling that simulated ROM data is present in MIRL and MIRR.

#### 3.2.3.6 BUSDR

BUSDR = 1 gives a bus data-ready pulse to signal completion of the read or write operation performed. (Refer to Section 3.2.3.10.)

#### 3.2.3.7 SCOPE

This bit will cause a special pulse each time it is 1. Its use is to facilitate stable oscilloscope triggering in the test loops.

#### 3.2.3.8 MCLIR

MCLIR = 1 will issue a CUT Master Clear pulse.

#### 3.2.3.9 STOP

This bit will enable the CUT CPU stop signal when equal '1'.

Note: This bit will also be set by hardware if the CUT CPU does a TRA from register 9. (Refer to Section 3.2.7.7.)

#### 3.2.3.10 Timing

For ease of use there is a small delay on the BUSDR signal. Hence, the EWBUS and BUSDR may be applied in the same instruction without any risk of racing.

#### 3.2.4 Write to Bus Buffer Register

IOX HWBUS

% 164027

The TSC A register is transferred to a buffer register. This buffer register may be enabled onto the CUT IB-bus by setting the EWBUS bit in the test status word (see Section 3.2.3.2 and 3.2.3.10).

#### 3.2.5 Read Micro Program Counter

IOX HRMPC

% 164020

The  $\mu$ -program address presented to the RSC is transferred to the TSC A-register.

#### 3.2.6 Read Memory Address

IOX HRMAD

% 164022

The CUT MR-bus is transferred to the TSC A register.

#### 3.2.7 Read Test Status

IOX HRTST

% 164024

The test system status word is transferred to the TSC A register.

The format of the status word is as follows:

| 15 | 14 | 13 | 12 | 111 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|-----|----|---|---|---|---|---|---|---|---|---|---|

| T  | T  | S  |    |     |    |   | M |   |   | I | F | W | R |   | R |

| R  | R  | Т  | 1  |     |    |   | 0 |   |   | R | R | R | R |   | 0 |

| R  | A  | 0  | 1  |     |    |   | 0 |   |   | E | Ε | E | E |   | 0 |

| 0  | 0  | P  |    |     |    |   | R |   |   | Q | Q | Q | Q |   | R |

Figure 2.3

Test System Status Word

#### 3.2.7.1 ROM out of range (ROOR)

ROOR = 1 signals that there is a request to the ROM that has not been acknowledged by a ROM data-ready.

#### 3.2.7.2 Read Request (RREQ)

This bit signals a memory read request. It is enabled by the MOOR-bit (see Section 3.2.7.6).

#### 3.2.7.3 Write Request (WREQ)

This bit signals a memory write request. It is enabled by the MOOR-bit.

#### 3.2.7.4 Fetch Request (FREQ)

This bit signals that an instruction fetch is requested from memory. It is enabled by the MOOR-bit.

#### 3.2.7.5 Indirect Request (IREQ)

This bit signals that an indirect reference is requested from memory. It is enabled by the MOOR-bit.

#### 3.2.7.6 Memory out of range (MOOR)

This bit equals 1 if the latest memory request is not satisfied by a data ready pulse from memory (or the test system). A further specification as to the type of request may be found in bits 2-5. (See the Sections 3.2.7.2 to 3.2.7.5.)

#### 3.2.7.7 STOP

This bit shows if the CPU stop-signal is on. It will be set by bit 13 in WTST (see Section 3.2.3.9), or by the CUT if it executes a TRA 9  $\mu$ -instruction.

#### 3.2.7.8 TRA 0

This bit is set if the CUT does a TRA 0 instruction.

#### 3.2.7.9 TRR 0

This bit is set if the CUT does a TRR 0 instruction.

#### 3.2.8 Read CUT IB-bus

IOX HRBUS % 164026

The CUT IB-bus is transferred to the TSC A register.

#### 3.3 Test Connector Card

The test connector card (TCC) resides in the CUT where it is placed in the spare memory address slot (position 18). The purpose of the TCC is to interface the CUT to the TSC. It merely consists of the necessary tranceiver logic.

#### 3.4 Test System Card (TSC)

The test system card resides in card slot 17 of the CUT. This is the slot normally occupied by the Panel Driver or its equivalent.

TSC holds the necessary logic to read and write the CUT IB-bus (RBUS and WBUS), including the WBUS buffer register. In addition functions normally belonging to the Panel Driver is located on this card.

These functions include the following:

- Master Clear (MCL).

- Bus Data Ready (MDRY).

- Operators Panel interrupt signal (OPINT).

- Stop signal (STOP).

- TRA0 and TRR0 status bits.

The STOP signal is set from the TSC (see Section 3.2.3.9) or from the CUT if a TRA9  $\mu$ -instruction is executed. The status of the STOP signal can be read from RTST (see Section 3.2.2).

#### 3.5 ROM Simulator Card (RSC)

The ROM simulator card replaces the normal CUT ROM card (postion 10).

Two versions of the RSC may be delivered;

- ROM simulator alone.

- ROM simulator combined with 1/2 K real ROM.

The latter has the possibility of running in mixed mode during simulation. The main test system does not use the real ROM option and may be run with the simplest version.

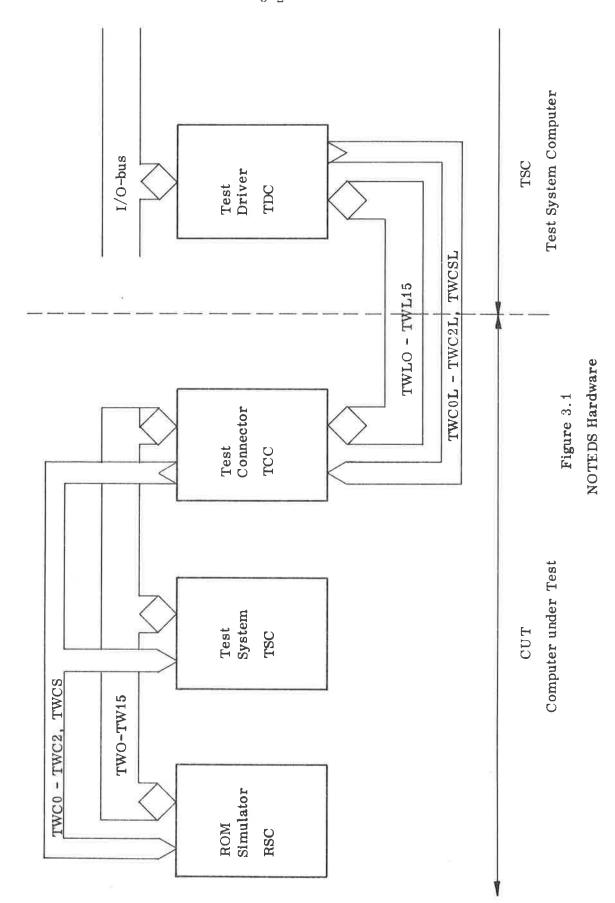

In the following refer to Figure 3.3.

Figure 3.3 ROM Simulator Card, End View

#### 3.5.1 FLICK

These two LED (Light Emitting Diode) will flick on and off each time NOTEDS discovers an error. This feature is used to display an indication of error frequency.

#### 3.5.2 SMEM

This LED is on when a request to simulated main memory is on.

#### 3.5.3 ROOR

This LED is on when a request to simulated ROM is on.

#### 3.5.4 SKPE

On this test pin there is a positive going signal once per error loop. Refer to the appropriate error loop description. (Appendix A.)

#### 3.5.5 ROMDRY

On this test pin there is a positive going signal each time ROMDRY is given from the test system.

#### 3.5.6 ROMSKPE

This test pin presents the logical or between SKPE and ROMDRY. The SKPE pulse is wider than the ROMDRY pulse. Suggested use is to connect one scope channel to this point and the external trigger input to the SKPE signal. In this way one channel can be freed for other purposes. The ROMDRY and SKPF pulses can still be distinguished as they have different widths.

#### 3.5.7 DSKPE

On this test pin a delayed SKPE pulse will occur.

The delay is given in ROMDRY pulses and is set by the DELAY switches. The delay may be varied from 0 - 15 ROMDRY pulses.

The DSKPE functions as follow:

Each time a SKPE pulse is given, a 4-bit counter is loaded with the content of the DELAY switches. This counter counts down on each of the following ROMDRY pulses. When the counter hits zero, DSKPE happens.

This feature may be useful when the SKPE pulse timing does not fit the problem at hand.  $\,$

#### 3.5.8 <u>ERR</u>

This test pin goes positive each time an error is detected in the test loop.

#### 4 TEST SYSTEM USAGE

NOTEDS contains a number of separate tests. Each test is aimed at testing a particular part of the N-10 CPU or NOTEDS hardware. The tests that work on the CPU are named T1  $\cdots$  T $\lt$ n $\gt$ . Some special tests are named TX1  $\cdots$  TX $\lt$ n $\gt$ . These include system link tests, memory check etc.

The names of the tests that are to be included in a test run are listed in the <u>Program Table</u>. Normally one will work with a standard sequence (increasing test numbers) where the CPU is tested in a logical manner. However, it is possible to modify the program table so that it contains only selected tests (see Section 4.1.11).

The test run may be started at any test in the table. When the end of the program table is encountered, the test system will automatically loop back to the top of the table.

Running tests can be interrupted any time by simply typing a command to the test system monitor.

When NOTEDS discovers an error, an appropriate error printout will be presented on the display. The exact format of this printout differs from test to test, but generally it obeys the following:

- i) Naming of the test that fails.

- ii) The expected and actual result, bit by bit.

- iii) Relevant parameters and data used in the test.

When the error printout is completed, the test system will repeat the test continously using the same test conditions. This error loop will be maintained even if the test should stop failing. A scopetrigger signal is presented once every loop. This signal is under program control and is given just ahead of the critical part in each test. Two LED's are flicked each time an error is detected. This provides an indication to whether the error is permanent or intermittent in nature. The error loops are documented in Appendix A.

#### 4.1 Test System Monitor Commands

)

As already noted, the test system will accept commands at any time. When no tests are running, the test system monitor will announce itself with the herald:

The available commands are described in the following:

#### 4.1.1 A - Call Assembler

The A command will cause an exit to the assembly system (or other external system), if available.

Initial linking can be performed by setting the assembler's start address in ASMBL. Refer to Section 4.1.12.

#### 4.1.2 B - Back, restart current Test

The B command will restart the current test.

#### 4.1.3 C - Continue current Test

The C command will continue the current test with the next data set. Refer to the appropriate test description.

#### 4.1.4 D - Debug, Register examine/deposit

The D command will enter a special routine where most of the CUT registers may be examined and modified. This routine uses the herald ':'. Exit from the Debug routine will take place when the '2' command is detected.

The general format is:

: < register name > < level > / < old content > < optional new content >

Example:

The old content of the A register on level 13 $_8$  (177037) will now be replaced by the new content 123456.

If the old content is immediately followed by a CR, then the register content is not disturbed.

Some registers can only be read. For these registers an automatic CR/LF will be given immediately after the old content. Likewise, some registers may only be written into. In this case there will be no display of old content following the /.

Examples:

:<u>HE/ 000</u>2

The special register name ALL means all registers on <u>current</u> \* level. The following registers are included in the ALL command:

AC1, AC0, SH1, SH0, SS, SP, SCR, SC, H, R T, A, D, X, B, P, L, STS, MPC,

The ACO (least significant sum register) can only be correctly displayed if there is no real memory connected to the CUT. This fact is signalled by MMASK (refer to Section 4.1.12). An appropriate warning is given if ACO is disturbed.

Note: The MPC, AC and H registers will be correctly displayed, but are disturbed during the ALL command.

Following is a list of legal register names. Note that if the level code is left out, level 0 is assumed.

#### Legal register names:

| 7 70 747          | Zero register                                               |

|-------------------|-------------------------------------------------------------|

| Z, Z0 - Z17       |                                                             |

| D, D0 - D17       | D register                                                  |

| P, P0 - P17       | P register                                                  |

| B, B0 - B17       | B register                                                  |

| L, L0 - L17       | L register                                                  |

| A, A0 - A17       | A register                                                  |

| T, T0 - T17       | T register                                                  |

| X, X0 - X17       | X register                                                  |

| S, S0 - S17       | STS register (as A operand)                                 |

| SCR, SCR0 - SCR17 | Scratch register                                            |

| SP, SP0 - SP17    | Scratch register (saved P)                                  |

| SS, SS0 - SS17    | Scratch register                                            |

| R                 | Address bus                                                 |

| Н                 | H register (hard to get at in normal cases)                 |

|                   |                                                             |

| MPC               | Micro-program counter<br>(Note: Disturbed by Master Clear.) |

| SC                | Shift counter                                               |

| SH1, SH0          | Most/least significant shift register                       |

| BM0 - BM17        | Bit mask, bit 0 - bit 17 <sub>8</sub>                       |

| XR                | R register (read as A operand)                              |

|                   |                                                             |

For all practical purposes this will be level 0.

| Read | Write | Internal Register                      |

|------|-------|----------------------------------------|

| STS  | STS   | Status register                        |

| PGS  |       | Paging status register                 |

|      | PCR   | Paging control register                |

| PVL  |       | Previous level                         |

|      | MISC  | Miscellaneous register (PON, ION etc.) |

| IIC  |       | Internal interrupt code register       |

|      | IIE   | Internal interrupt enable register     |

| PID  | PID   | Priority interrupt detect register     |

| PIE  | PIE   | Priority interrupt enable register     |

| PES  |       | Parity error status register           |

|      | CAR   | Computed address register              |

| MPA  |       | MPC (μ-program counter)                |

|      | IR    | Instruction register                   |

| PEA  |       | Parity error address register          |

#### 4.1.5 L = List tests in Program Table

The L command lists the content of the program table. The print-out may be stopped at any point by typing 'space' on the display keyboard.

#### 4.1.6 M - Master Clear

The M command issues a hardware CUT\* Master Clear pulse.

#### 4.1.7 N - Start next Test in Table

The N command aborts the current test (if running) and starts the next test found in the program table.

#### 4.1.8 P = Start previous Test in Table

The P command aborts the current test (if running) and starts the previous test found in the program table.

#### 4.1.9 R = Restart at beginning of Test Table

The R command will restart the test run at the beginning of the test table.

<sup>\*</sup> CUT - Computer under test.

#### 4.1.10 S - Step Function in current Test

The S command will step the current test to the next logical function (if applicable). Refer to the actual test description for details.

#### 4.1.11 T = Form new Test Table

This command is used to modify the standard sequence of tests. It operates on the test table in a sequential 'examine' - 'optional deposit' mode.

Example:

T1 is maintained as 1. test, but T2 is replaced by T3 and T99 and is inserted instead of T3. T99 is no test, it simply signals end of test run and restarts at the top of the test table.

2 signals end of modification and returns to the monitor. Note that all entries not specifically changed will remain untouched.

#### 4.1.12 U = Update Test System Parameters

The U command makes available an examine/deposit function on the test system parameters. Symbolic names are used to specify the parameters.

General format:

The < new value > is optional. Exit from the parameter update routine is by a ' $\mathcal{D}$ ' command.

The following is a list of available parameters and their functions.

**AMODE**

= If this parameter is ≠ 0, the tests will be terminated when an error is detected and no Master Clear pulse is issued automatically. This mode can be used to study a 'frozen' CPU if hang-up problems occur.

Normal value: 0

MASKP

Main comparison mask. A '0' in this mask will suppress errors in the corresponding (data) bit.

Normal value: 177777

RMASK

Bit mask that flags the registers (0 - 17) to test.

The registers should be legal A-operands and destinations, i.e.: D, B, L, A, T, X, SCR, SP, SS.

Normal value: 150372

LMASK

= Bit mask that flags the levels (0 - 17) to test in register addressing and register data tests.

Normal value: 177777

FLMSK

- Bit mask that flags the logical ALU functions (0 - 17) to test.

Normal value: 177777

FAMSK

Bit mask that flags the arithmetic ALU functions

(0 - 17) to test.

Normal value: 177777

**SMASK**

Bit mask that flags the shift functions to test (0 - 17, MIR12-15 in LOOP instruction).

Normal value: 177777

CMASK

Bit mask that shows the conditions to test (0 - 17, MIR12 - MIR15).

Normal value: 177777

(Note: 0 - 7 are unconditional conditions.)

CYMSK

- Bit mask to flag memory cycles to test (0 - 7).

Normal value: 000377

BMASK

- Bit mask to flag bits to test in the bit mask (0 - 17).

Normal value: 177777

IMASK

Interrupt level mask. Flags interrupt levels to test (0 - 17).

Normal value: 177777

IMIR IWTST IWBUS IMPC IMAD IRTST IRBUS - Bit masks that shows which bits should be complemented to compensate for hardware invertion of the data. It will normally not be necessary to change these masks. They are included for historical reasons. The names refer to logical test system links: MIR (MIRR and MIRL), WTST, WBUS, MPC, MAD, RTST and RBUS.

TMODE

- = Test mode

- = 0 The simulator (refer to Chapter 5) will use simulated ROM

- = 1 The simulator will use real ROM (1/2K)\*

Normal value: 0

MMODE

- Memory Mode

Bit mask to show how much real memory is connected to the CUT. Each bit signals a 8K block, 0 - 128K. Care should be taken that this mask describes the actual configuration at all times. Refer also to Section 5.1.7.

ASMBL

- Start address of assembler if available. If not available, a 0 could be deposited.

Normal value: Address of routine FAKE

ROM

- Start address of simulated ROM in TSC main memory.

Care should be taken that addresses 2\*(ROM) < 2\*(ROM)

+2\*(ROMZ) do not conflict with test system programs.

ROMZ

- Size of simulated ROM in 32-bit words.

Normal value: 2000 (1K ROM)

TOI

- IOT break address in micro-program.

Normal value: 177777 (no break) or 170

MON

Micro program break address for main memory break point.

Normal value: 2217 (entry point for 143700).

<sup>\*</sup> Real ROM is an option to NOTEDS hardware.

WAIT - Micro-program break address for trapping

WAIT instructions.

Normal value: 244 (WAIT entry point).

MBPC - Main memory break point code.

Normal value: 143700

(Note: (MON) should always contain the entry point

address of the MBPC.)

#### 4.1.3 X - Call Simulator

The X command will switch to the simulator monitor, if available. This monitor announces itself with the herald:

g

Return from the simulator monitor is by X or 2 command.

#### 4.1.4 ! - Start specified Test

The ! command will ask for a test name. When this name has been typed in, the test will be started. If no errors are detected, the test system will continue with the next test in the program table.

Example:

) 🚣

TEST NAME: T20

NOW RUNNING: T20 TG CONTROL

#### 4.2 Available Tests

The following is a summary of available tests. For more details, refer to Appendix A.

#### 4.2.1 Standard Test Sequence (T < n >)

TO − TSC ← CUT IB ← TSC

Transfers data to and from the CUTIB bus. Used to test the IB bus. The test does not involve the CUT CPU.

(Note: This test may be absent in some versions of NOTEDS. In this case TX5 will serve the same purpose.)

- T1 TRANSFER TO/FROM H-REGISTER

Transfers data to and from the CUT H register (data input register). This is a very basic test.

- T2 A AND D REGISTER TRANSFER

Transfers data to and from the A and D registers in a very basic way. This test is used to establish contact with CUT central registers.

- T3 STANDARD ROUTINES

Basically the same test as T2, but uses more general software routines.

- T4 E LOGICAL ALU FUNCTIONS

Test the logical ALU functions between A and D registers.

- T5 = REGISTER ADDRESSING

Tests the addressing of all level dependant registers.

- T6 REGISTER DATA

Tests the registers more fully with regard to data combinations.

- 77 REGISTER DISTURBANCE

Very extensive register test. Performs a thorough distrubance test on all general registers.

- TRANSFER TO/FROM STS REGISTER

Tests the setting and reading of the STS register (as A-operand).

- T9 ARITHMETIC ALU FUNCTIONS

Full test of arithmetic ALU functions including carry input and output.

T10 - CONDITIONAL ARITHMETIC

Tests the conditional arithmetic.

T11 - ABSOLUTE JUMP

Tests the micro-processor absolute jump.

T12 - CONDITIONAL JUMP

Tests the micro-processor conditioned jump.

T13 - COMPUTED ADDRESS JUMP

Tests the micro-processor computed address jump.

This also tests the setting of the 12 lower bits of the instruction register.

T14 - BIT MASK

Tests the bit mask B operand.

T15 - SC - SETTING

Tests the setting and reading of the shift counter.

T16 - TRANSFER TO/FROM SHIFT REGISTER

Tests the data transfer to and from the shift register.

T17 -

T18 - DELTA - H

Tests the sign-extended half part of the H register.

T19 - LOOP SHIFT

Tests the LOOP instruction shift functions, including the link flip-flop input and output.

T20 - TG - SETTING

Tests the setting of the TG flip-flop (floating point rounding control).

T21 -

T22 -

T23 - FETCH CYCLE

Test of fetch cycle request setting.

- T24 MICRO-ADDRESS GENERATOR

Tests all micro-processor entry points (excluding interrupt entry points).

- T25 MEMORY REQUESTS AND ADDRESS ARITHMETIC

Test all memory cycle request settings and the address arithmetic.

- T26 FETCH, CONDITIONALLY ADD 1 TO P

Test of special feature, P as destination register together with memory reference relative to the P register.

- T27 MPC COUNTING

Tests the MPC for proper counting.

- T28 = P COUNTING

Tests the P register for proper counting.

- T-29 R COUNTING

Tests the R register for proper counting.

- T30 END-INPUT FOR DIVISION

Tests the end-input to the shift register during division loops.

- T31 -

- T32 SPECIAL ENTRY POINTS

Test the entry point for STOP, MASTER CLEAR and PANEL INTERRUPT.

- T33 = 1. INTERRUPT TEST (MPC)

Tests the entry point for external interrupt.

- T24 2. INTERRUPT TEST (PIL)

Tests correct program level after interrupt and level shift.

- T35 = 3. INTERRUPT TEST (PIL)

Tests correct program level during two succeeding level shifts.

- T36 4. INTERRUPT TEST (PVL)

Tests the previous level (code) after level shift.

#### 5.1.4 L = Load from Paper Tape

The L command will load a standard Binary Format tape (as dumped by the MAC command)BPUN) from the TSC tape reader into CUT memory. The tape will be loaded into real or simulated CUT memory according to the last S command. The binary program is <u>not</u> started after successfull loading.

Note: There is no checking of simulated core limits. Care should be taken not to overlay the test system.

#### 5.1.5 M - CUT Master Clear

The M command issues a CUT Master Clear pulse.

#### 5.1.6 P - Print Simulation Log

The P command will dump the last (up to 48) references to simulated main or ROM memory on the test system console. This simulation record should be read columnwise, the last reference being the last in the rightmost column.

Each simulator reference is described by three numbers.

Format of reference:

<3 digit request word> <6 digit data> <6 digit memory address>

#### Request word

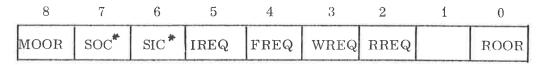

The request word shows the reference type, and it has the following format:

Figur 5.1

#### Request Word

MOOR

Memory out of range. If this bit is set, the reference is a reference to simulated main memory. Further specification is given by IREQ, FREQ, WREQ and RREQ.

SOC\*

Memory output command.

SIC\*

- Memory input command.

Not included in the standard test system.

- Indirect reference. IREQ

This bit is enabled by MOOR and signals a request

for an indirect address.

Fetch request. FREQ

This bit is enabled by MOOR and signals a request

for an instruction.

- Write request. WREQ

This bit is enabled by MOOR and signals a CPU

data write request.

RREQ -- Read request.

This bit is enabled by MOOR and signals a CPU

data read request.

- ROM out of range. ROOR

This bit signals a reference to simulated ROM.

Note: The MOOR bit has higher priority than the ROOR

when request type is decoded.

It is important to note that bits 2 - 7 are only valid if bit 8, MOOR, is set.

The following is a list of normal request words:

021 - ROM request

011

005

441, 440 - Indirect request

421, 420 = Fetch request

411, 410 - Write request

401, 404 - Read request

#### Data Word

This word has two different meanings, depending on the request type.

If the MOOR bit is set, the data word contains the actual data transferred to/from simulated memory.

If the MOOR bit is not set (the reference being a ROM reference), then the data word contains the micro-program address referenced.

#### Memory Address

This is the content of the memory address bus. In some cases the simulator will read the address bus when it is not enabled. The memory address 177777 will result. As this is of no interrest, a memory reference to address 177777 (true or false) will not be displayed as the actual number, but as 6 spaces.

The main memory references will not be "visible" if real memory is referenced.

The ROM references will not be "visible" if real ROM is referenced.

The logger table is only maintained when program execution is started by the ! command.

#### 5.1.7 S - Set Memory Mode

The 'S' command will logically split CUT memory into real and simulated parts.

Format:

\$ S

#### MMODE/XXXXXX YYYYYY

XXXXXX — Old memory mode word

YYYYYY (Optional) new memory word. Each bit = 1 flags a 8K block as belonging to real CUT memory.

Bit 0 = 1 0 - 8K Bit 1 = 1 8 - 16K Bit 15 = 1 120 - 128K

Care should be taken that the memory mode word <u>always</u> corresponds to the physical memory connected to the CUT. If this is not observed, the simulator may not function properly. The memory mode word also affects the examine and deposit function together with the L command and the main memory break point setting.

#### 5.1.8 T - Transfer to CUT Memory

The 'T' command will copy the content of TSC core (as defined by the < command) into real or simulated CUT core (as defined by the S command).

#### 5.1.9 <u>U</u> - <u>Update System Parameters</u>

This command is identical to the test system U command, see Section 4.1.12.

#### 5.1.10 X - Exit from Simulator

The X command will exit from the Simulator back to the test system monitor (see also Section 5.1.18).

#### 5.1.11 '.'- Main Memory Break Point

The '.' command has two uses. If it is given without a preceding address, it means: 'Reset break point'. If it is preceded by an (octal) address, a break point code will substitute the actual instruction in the specified address. (Any old break point will be reset first.) When the ROM simulator runs, it will check for references to the micro-program break address, ((MON)). The simulator stops if a match is found and an appropriate message is displayed together with all the registers on the current level.

Normally, the break point code is 143700 with a corresponding micro-program break address = 2217 (2217 is the entry point for the 143700 instruction.

The break point code and the corresponding break address may be modified within the parameter update routine (see Section 4.1.12).

Note: If the main memory break point is located in simulated memory, it must be within the limits defined by the '<' command (see Section 5.1.15).

#### 5.1.12 ',' ROM Break Point

The ',' command has the same use as the '.' command (see Section 5.1.11), but operates in the simulated Read-Only-Memory.

When the break point address is referenced, the simulator will stop and display all registers on current level together with an appropriate message.

Note: If an 'all zero' micro instruction is hit, then the message 'MICRO STOP' is displayed. The simulator stops and displays all registers on current level.

This fact can be used to trap references to illegal addresses.

#### 5.1.13 '/' - Main Memory examine/deposit

The / command is used to examine and modify the content of CUT real or simulated main memory.

Format:

```

$\leq \address > \setminus \text{(#)} < \text{old content} > \leq \text{new content} > \text{(#)} < \text{old content of address} + 1 > \leq \text{new content} > \text{(#)} < \text{old content of address} + 2 > \text{2} \text{2}

```

The < new content > is optional. CR will display the content of the next address. The examine/deposit function may be terminated by typing a space (or any monitor command).

The < old content > will be preceded by an # if the address belongs to real CUT memory (as defined by MMASK).

Note that no deposit is allowed in simulated main memory, outside the limits set by the '<' command (see Section 5.1.15).

If \*is typed when in examine/deposit mode, the address of the current location is printed out.

#### 5.1.14 '\' ROM examine/deposit

The '  $\$  ' is used to examine and modify the content of the simulated ROM:

Format:

#### XXXXX\

The content of ROM address XXXX is displayed in an appropriate format.

MIR TYPE: (A/I/J/L):Q

Appropriate heading

XXXX - ROM address

Q = A - arithmetic micro instruction

I - interblock

J - jump L - loop

CR - no deposit

ZZ ... ZZ - Bits 29 - 0 in the new micro instruction Note: Z = 0, 1 or 'control Z'

Edit features:

If  $Z = ASCII 32^*$ , then the previously typed bit is deleted.

If  $Z \neq 0$ , 1 or ASCII 32, then the micro instruction typed so far is dropped and the question 'MIR TYPF' is asked again.

For details regarding the micro instruction format, refer to the micro processor manual or Appendix B.

#### 5.1.15 '<' Set Memory Limits

The '<' command is used to define CUT simulated core limits.

Format:

<lower limit > <upper limit >

Note: Both limits inclusive.

When running, the CUT is not permitted to reference simulated memory outside the defined address space. The simulation is stopped and an appropriate message is displayed if this should occur.

Note that the limits defined by ' < ' also is referred to by the /, C, and T commands.

#### 5.1.16 ! - Start CUT Execution

The '!' command is used to start the CUT at a specified address.

Format:

< start address >!

<sup>\*</sup> ASCII 32 = control Z or the 'move cursor back' command on the display.

#### APPENDIX B

#### $\mu\text{--INSTRUCTION FORMAT}$

#### ARITM:

| 313029 | 252423    | 21201918 1       | 51514 1211 | 8 7   | 43 0 |

|--------|-----------|------------------|------------|-------|------|

| OP ALU | A CRYSCLL | C S H S OR SPEC. | BIT NO.    | EST B | A    |

#### INTERBLOCK:

| 313029 | 252423                | 21 2 | 2019 | 18 16      | 15 12 | 11   | 87 4 | 3 0 |

|--------|-----------------------|------|------|------------|-------|------|------|-----|

| OP ALU | A<br>R<br>S<br>E<br>L | C I  | V    | OR<br>SPEC | LEVEL | DEST | В    | A   |

#### JUMP:

| 3130292827   | 2423    | 161514 1211           | 0            |

|--------------|---------|-----------------------|--------------|

| OP A R R I V | 0 0 0 0 | 0 0 0 0 0 N TC ADDRES | S (ABSOLUTE) |

#### LOOP:

| OP ALU ALT.ALU S K A S V H OO R F E 2 M N  B T   1 L V T R N S | 3130 | 29 2 | 524 20  | 191   | 8      | 1716 | 1.5 | 141 | 3       | 1211<br>ST | 10  | 9_8<br>T | 7 | 4     | 3 2 | I O |

|----------------------------------------------------------------|------|------|---------|-------|--------|------|-----|-----|---------|------------|-----|----------|---|-------|-----|-----|

| R F E 2 M N S                                                  | OP   | ALU  | ALT.ALU | 1.1   | R<br>S | 00   | S   | HYH | H       | E          | E C |          |   | 1 1   |     |     |

|                                                                | 11   |      |         | 1 - 1 | 1 11   |      | R   | F   | F 61 21 | 2          | T O | В        |   | lar I |     |     |

10/1 \$

ERROR - Error printout.

STOP - Simulation stopped, printout.

IOT SIM - (IOT simulated, NORD-1 versions only.)

A/S NORSK DATA-ELEKTRONIKK Lørenveien 57, Oslo 5 - Tlf. 21 73 71

#### **COMMENT AND EVALUATION SHEET**

ND-62.004.01

NOTEDS Reference Manual

In order for this manual to develop to the point where it best suits your needs, we must have your comments, corrections, suggestions for additions, etc. Please write down your comments on this pre-addressed form and post it. Please be specific wherever possible.

| FROM: |  |

|-------|--|

|       |  |

|       |  |

|  | 3   |

|--|-----|

|  | 9   |

|  | . 8 |

|  | - 0 |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  | · · |

|  | *   |

|  | Ĭ.  |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  | *   |

|  |     |

|  | 19  |

|  | 15  |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

|  |     |

- we want bits of the future