NORD-10/S

**Functional Description**

### NORSK DATA A.S

# NORD-10/S Functional Description

## **REVISION RECORD** Revision Notes 08/77 **Original Printing** 10/78 Revision A Typing errors and changed examples in Section II.8. We have also added a new section — Section II.7.9.

NORD-10/S — Functional Description Publication No. ND-06.009.01

NORSK DATA A.S.

Lørenveien 57, Postboks 163 Økern, Oslo 5, Norway

### MAIN CONTENTS

+ + +

### Section:

| •                                                                    | THE CPU                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I.1<br>I.2<br>I.3<br>I.4<br>I.5                                      | NORD-10/S Architecture The Interrupt System The Input/Output System Operator's Communication Operator's Panel NORD-10/S Power Unit                                                                                                       |

| 11                                                                   | THE STORAGE SYSTEM                                                                                                                                                                                                                       |

| II.1<br>II.2<br>II.3<br>II.4<br>II.5<br>II.6<br>II.7<br>II.8<br>II.9 | The Storage System The Memory Hierarchy NORD-10/S Storage System MOS — Memory Operating Principles Local Memory Error Checking and Correction Multiport Memory System Memory Management System Cache Memory Power Fail/Automatic Restart |

| 111                                                                  | SPECIFICATIONS                                                                                                                                                                                                                           |

| III.1<br>III.2<br>III.3<br>III.4                                     | System Control Programming<br>NORD-10/S Instructions<br>Programming Specification for I/O Devices<br>Specifications                                                                                                                      |

|                                                                      |                                                                                                                                                                                                                                          |

### Appendix

A LIST OF ABBREVIATIONS

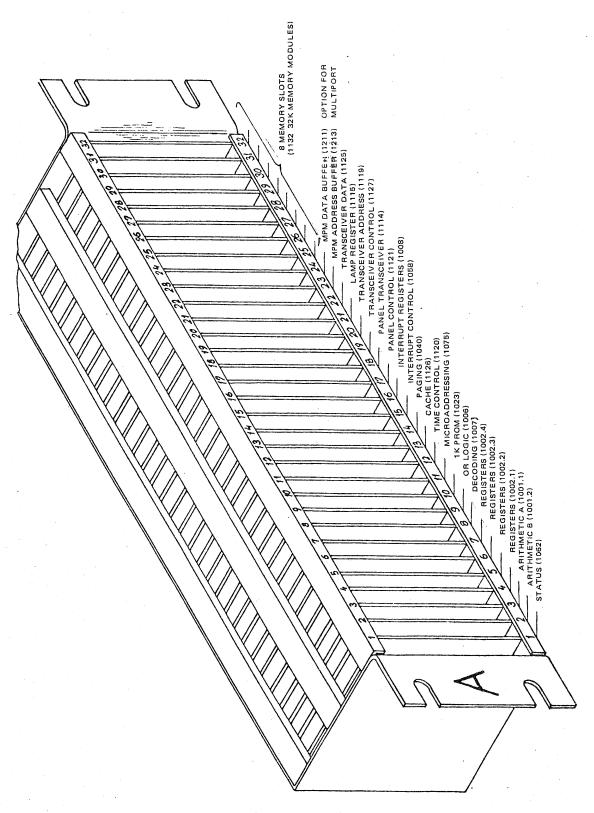

B NORD-10/S CARD ASSEMBLY

A detailed "Table of Contents" is at the beginning of each section.

ND-06.009.01

### **INDEX TO FIGURES**

+ + +

| Figure:        |                                          | Page:  |

|----------------|------------------------------------------|--------|

| <u>Section</u> | <u>1</u>                                 |        |

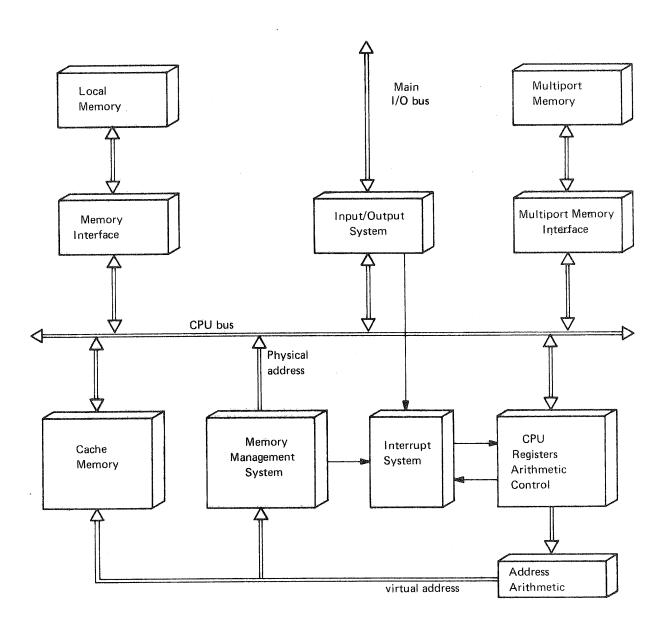

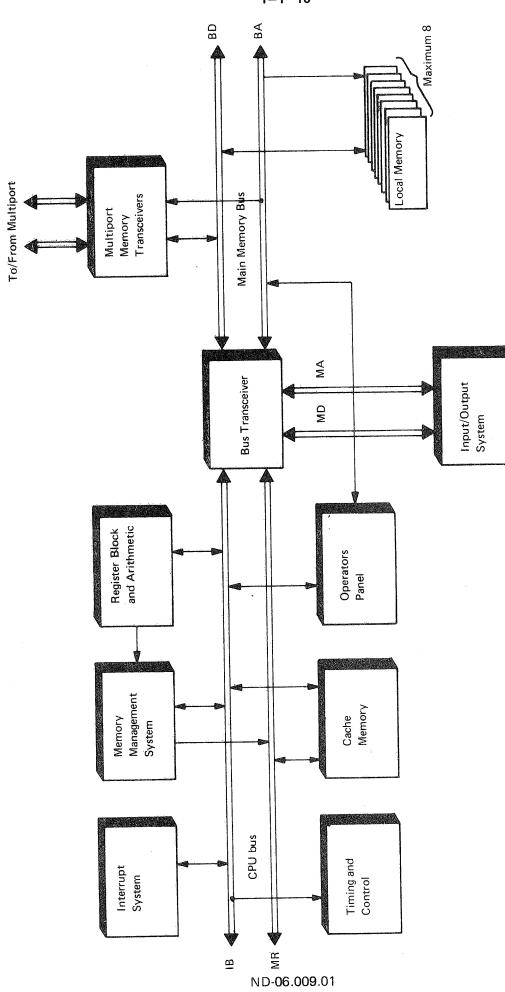

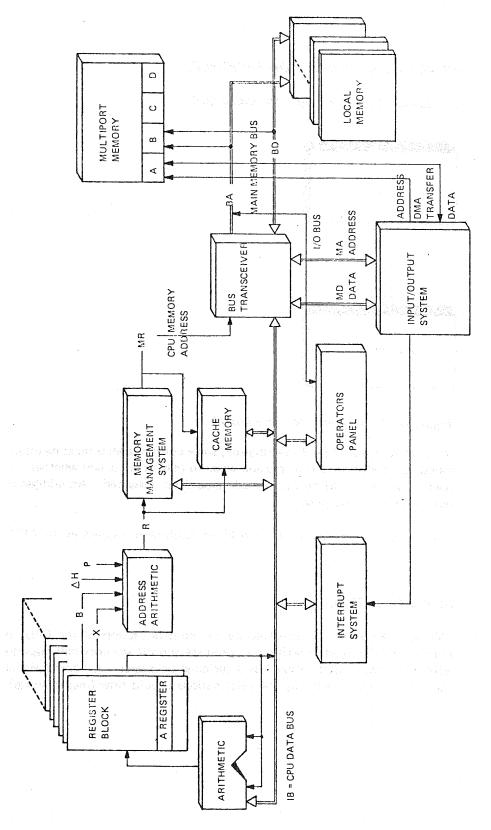

| 1.1.1          | NORD-10/S Block Diagram                  | 1-1-2  |

| 1.1.2          | MMS Main Functional Blocks               | I-1-5  |

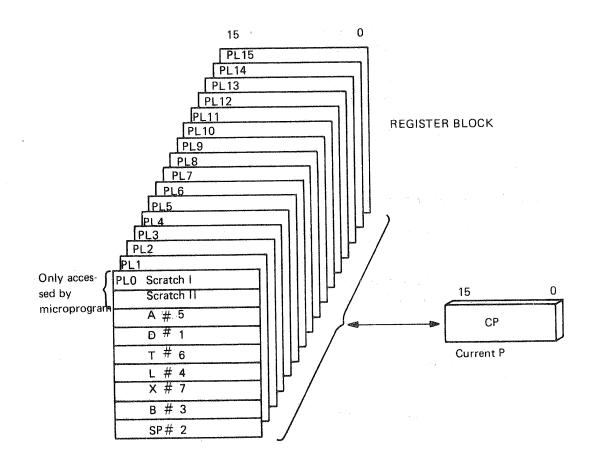

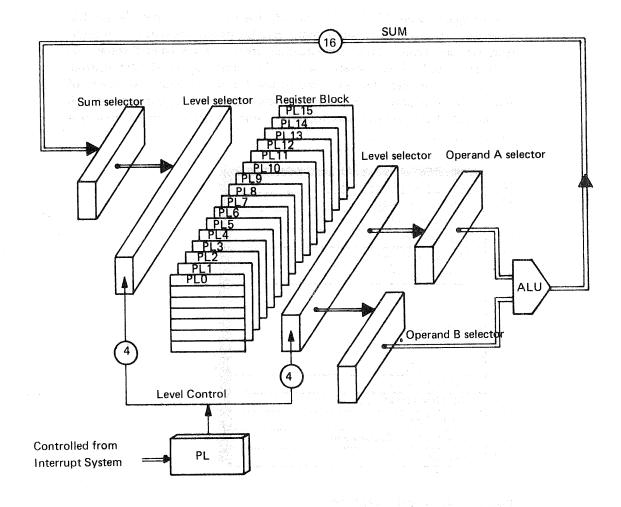

| 1.1.3          | Register Block                           | 118    |

| 1.1.4          | NORD-10/S Bus Structure                  | 1-1-10 |

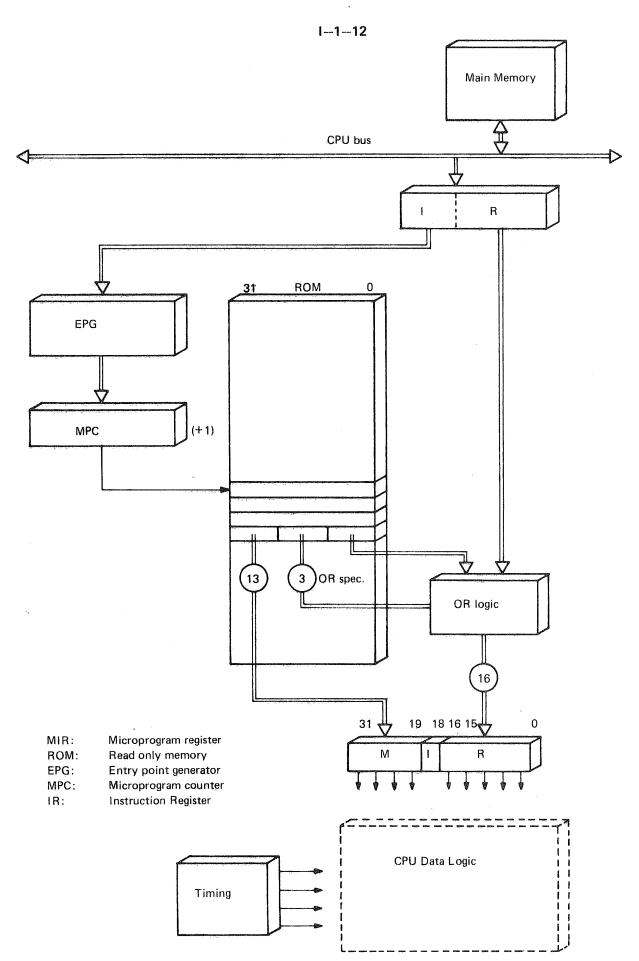

| 1.1.5          | CPU — Control Section                    | I112   |

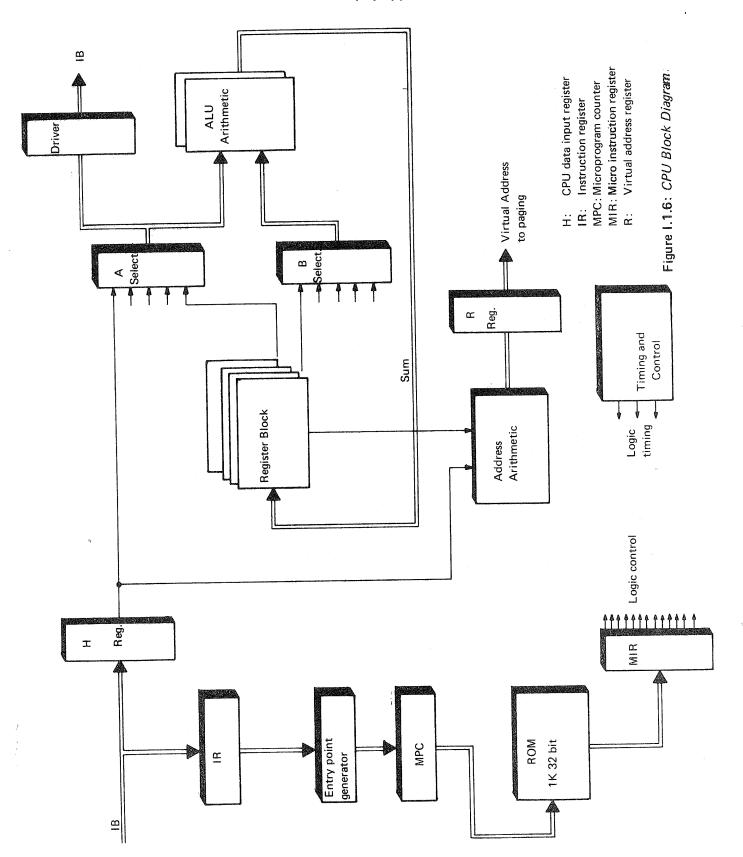

| 1.1.6          | CPU Block Diagram                        | I-1-14 |

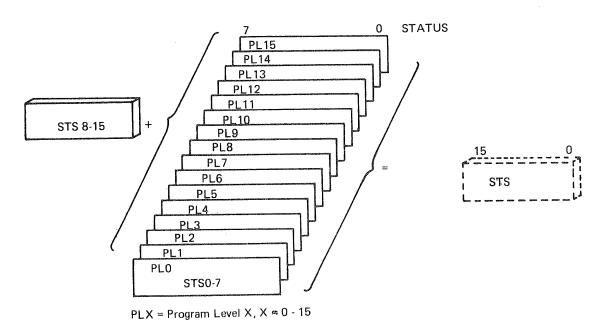

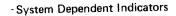

| 1.1.7          | Status - Bit Assignment                  | I—1—16 |

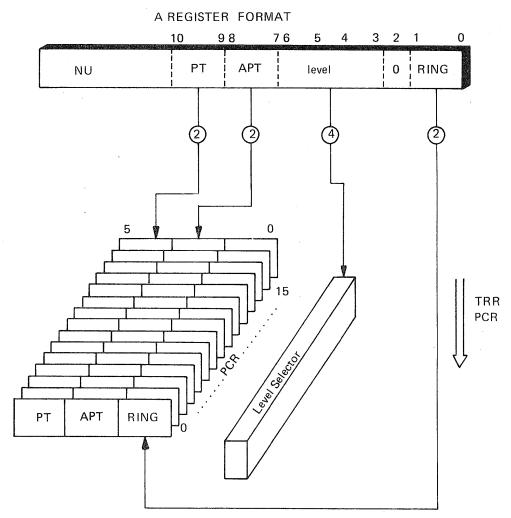

| 1.2.1          | Register Block, Level Usage              | 124    |

| 1.2.2          | Level Assignments                        | 1-2-5  |

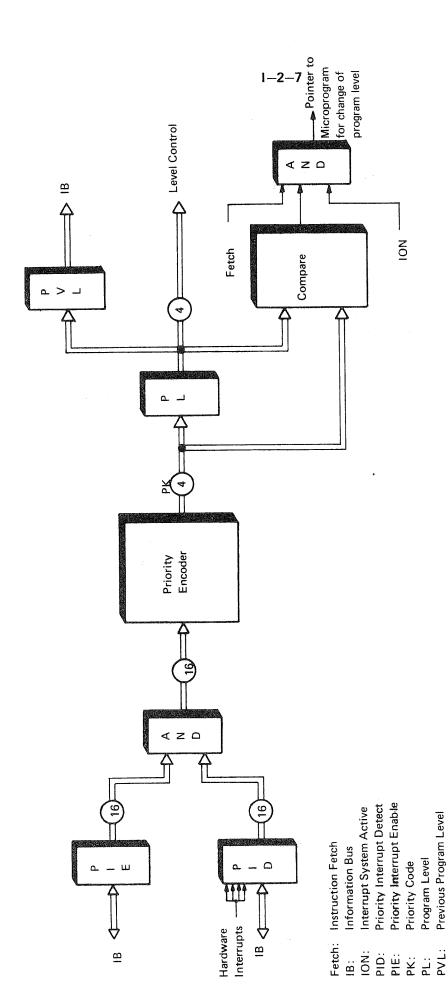

| 1.2.3          | External Interrupt System                | 1-2-7  |

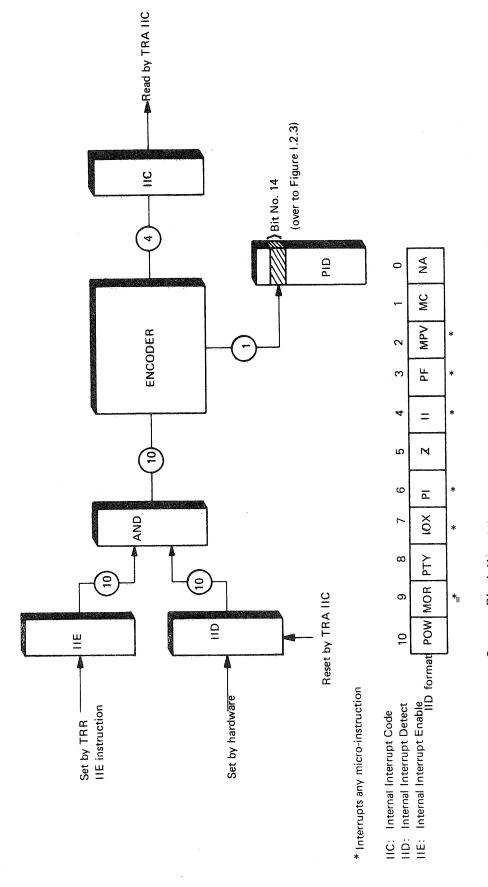

| 1.2.4          | Internal Interrupt System, Block Diagram | 1-2-9  |

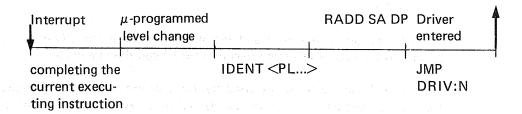

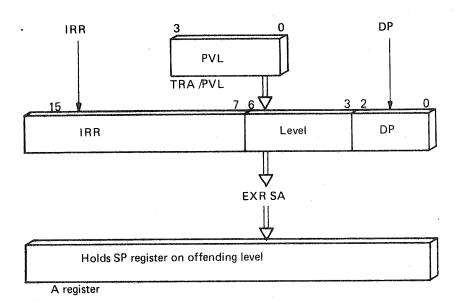

| 1.2.5          | TRA PVL, Flow Diagram                    | 1-2-19 |

| 1.3.1          | Storage Interconnection                  | 1-3-3  |

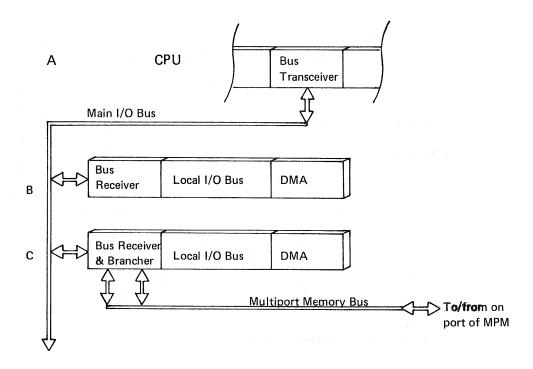

| 1.3.2          | I/O Architecture, Block Diagram          | 1-3-5  |

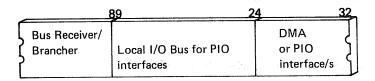

| 1.3.3          | I/O Card Crate, Physical Layout          | 1-3-5  |

| 1.3.4          | I/O Crate Control                        | 1–3–6  |

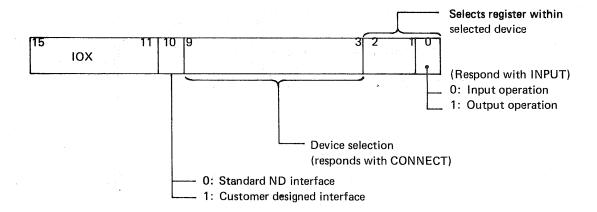

| 1.3.5          | IOX < Device Address > Decoding          | 1-3-7  |

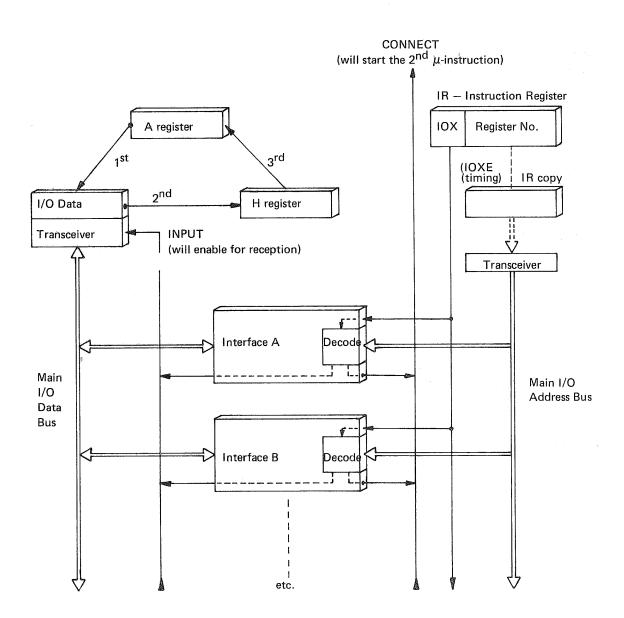

| 1.3.6          | IOX Instruction Execution                | 1–3–8  |

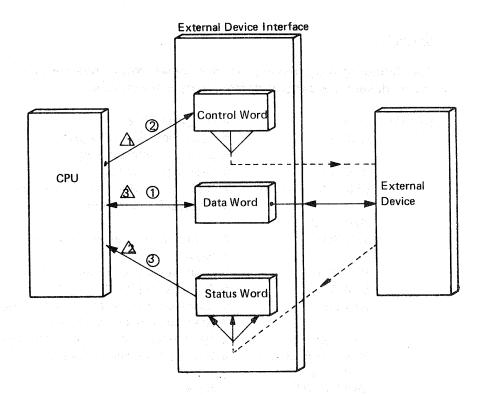

| 1.3.7          | Loading Sequence for Interface Registers | 1–3–13 |

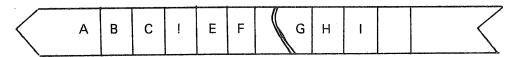

| 1.4.1          | Binary Load Format                       | 1-4-8  |

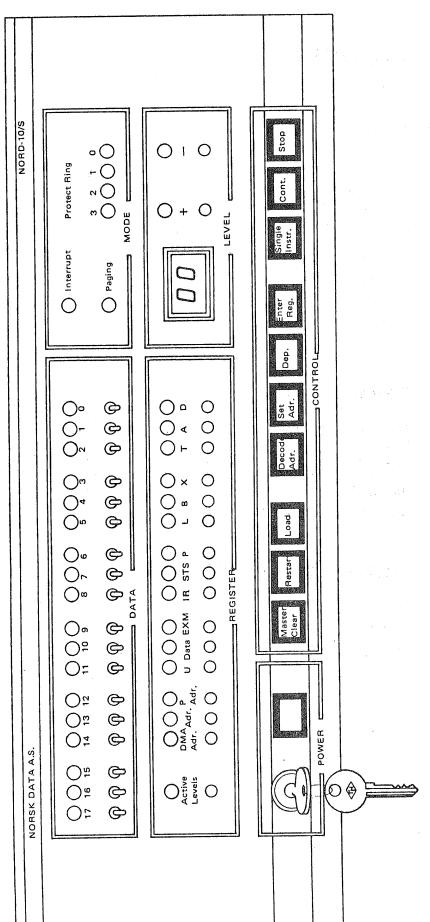

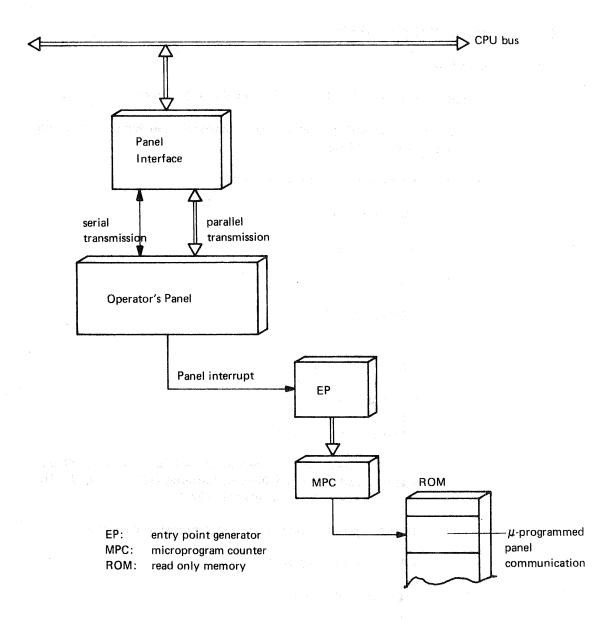

| 1.5.1          | Operator's Panel — Physical Layout       | 1-5-2  |

| 1.5.2          | Panel Data and Control                   | 1–5–9  |

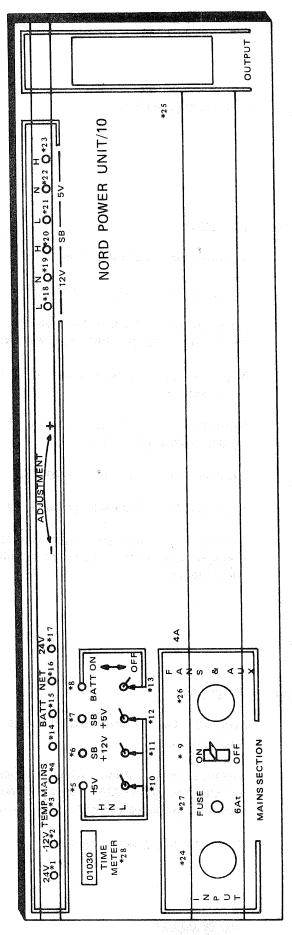

| 1.6.1          | NORD-10/S Power Unit                     | 1-6-2  |

| Figure:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | F | Page:           |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------|

| <u>, 11 4</u>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                 |

| Section II        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                 |

| <u>Jection ii</u> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                 |

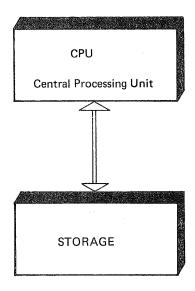

| 11.1.1            | A Simple Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 11–1–2          |

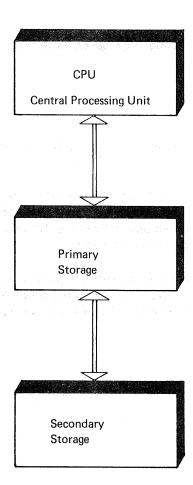

| 11.0.4            | Two Lord Storogs System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | II <b>—2</b> —1 |

| 11.2.1            | Two Level Storage System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                 |

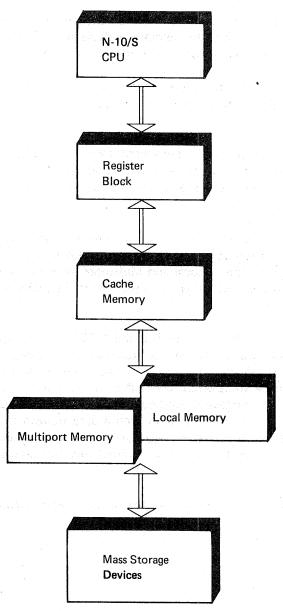

| 11.3.1            | Multilevel Storage System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | II <b>3</b> 1   |

| 11.3.2            | Storage Interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 11-3-3          |

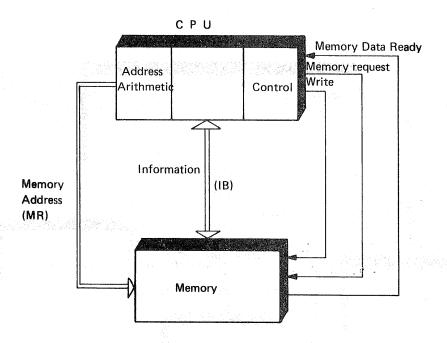

| 11.3.3            | A Simple Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 11-3-4          |

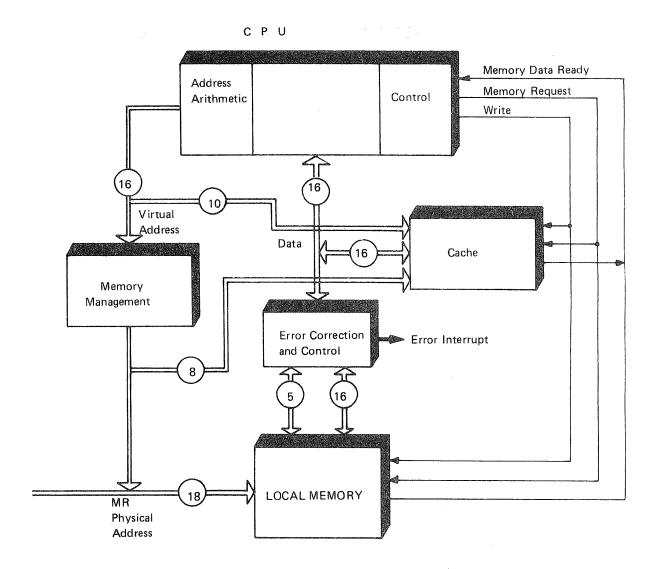

| 11.3.4            | Memory Information and Control - Principal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 11-3-5          |

| 11.3.5            | Memory Information and Control — Functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 11-3-6          |

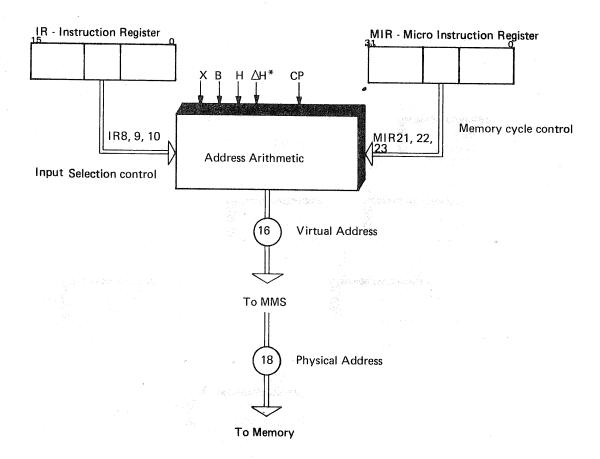

| 11.3.6            | Address Arithmetic — Input and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 11–3–9          |

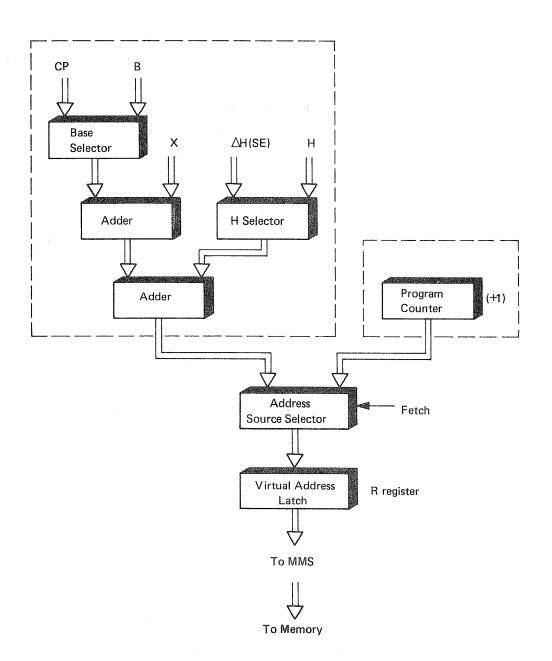

| 11.3.7            | Address Arithmetic — Functional Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 11–3–10         |

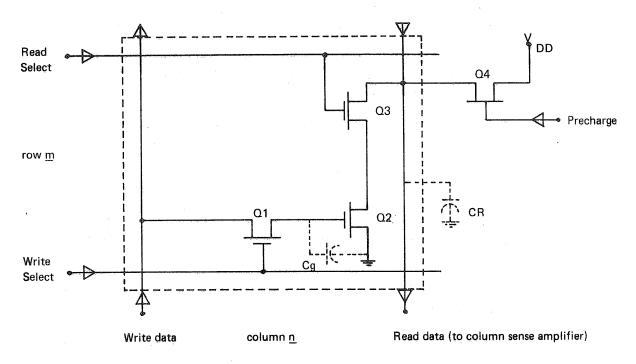

| 11 / 1            | A Memory Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 11-4-2          |

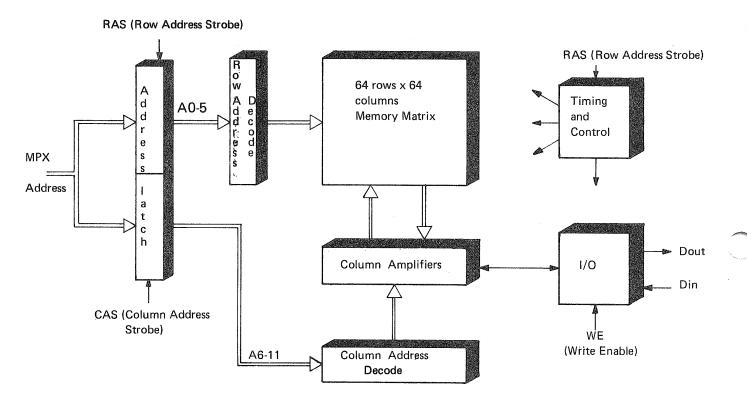

| 11.4.1<br>11.4.2  | A Memory Chip — Functional Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 11-4-4          |

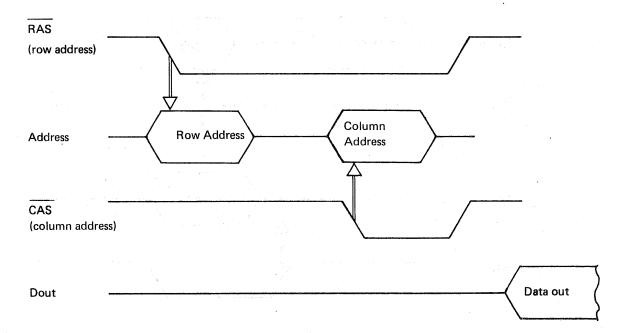

|                   | Read Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 11-4-5          |

| 11.4.3            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 11 -4-6         |

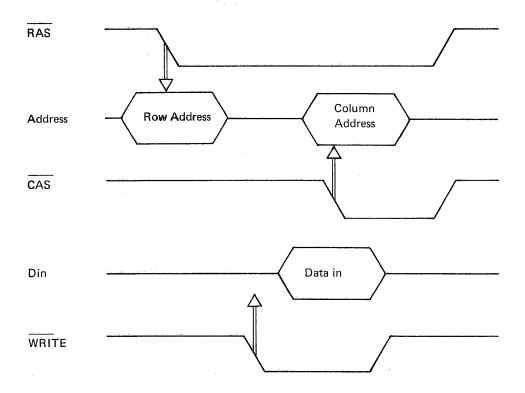

| 11.4.4            | Write Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 1146            |

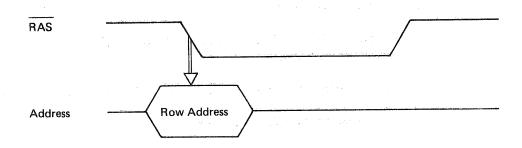

| 11.4.5            | Refresh Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |                 |

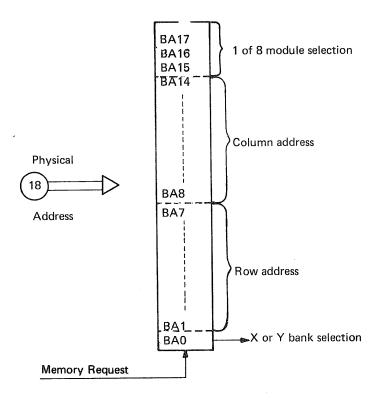

| 11.5.1            | Address Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 11-5-2          |

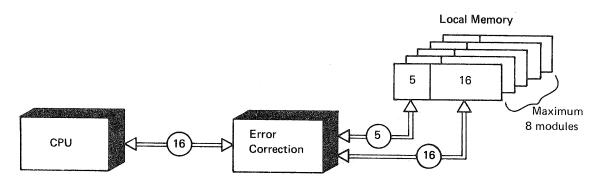

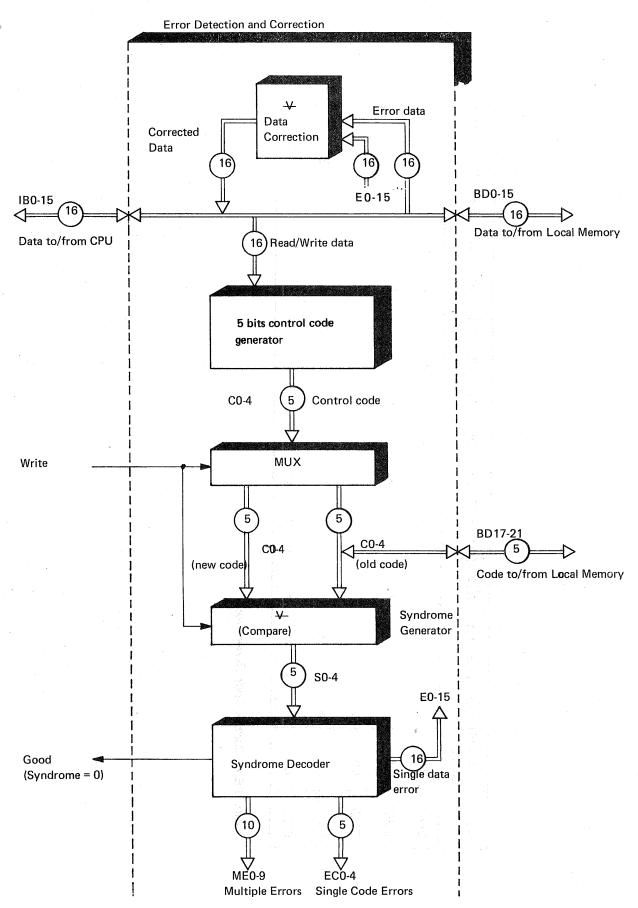

| 11.5.2            | Error Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 11-5-2          |

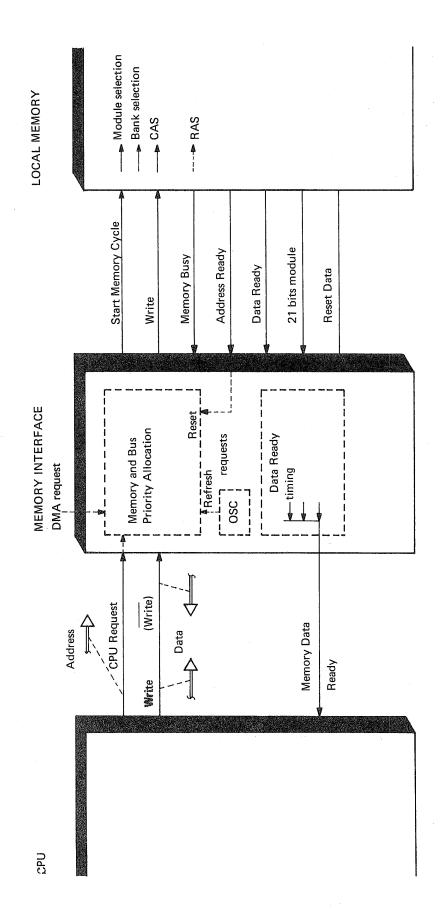

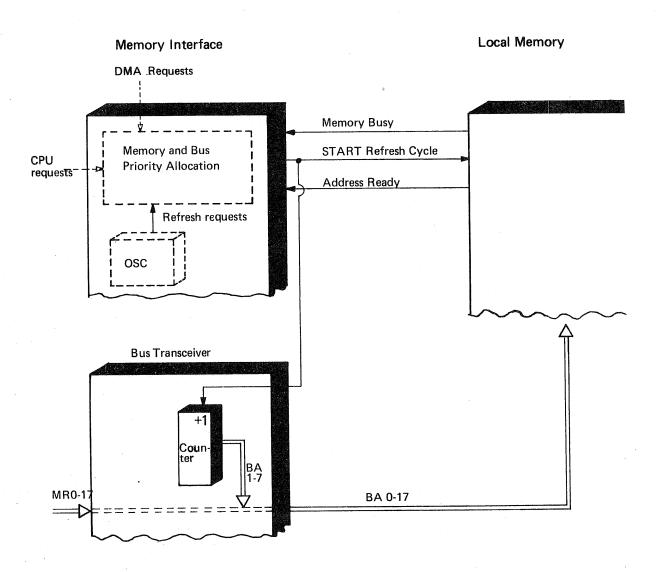

| 11.5.3            | Memory Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 11-5-4          |

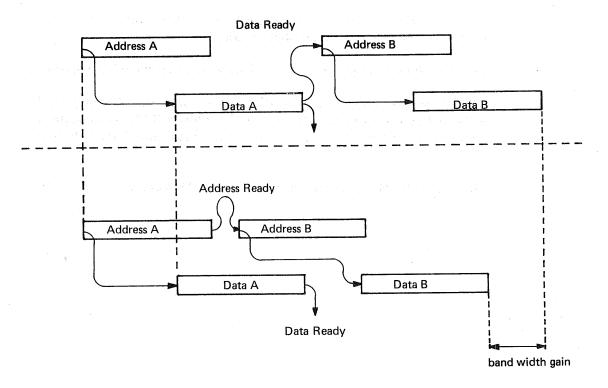

| 11.5.4            | Data and Address Ready Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 11-5-5          |

| 11.5.5            | Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 11-5-7          |

|                   | in the state of th |   |                 |

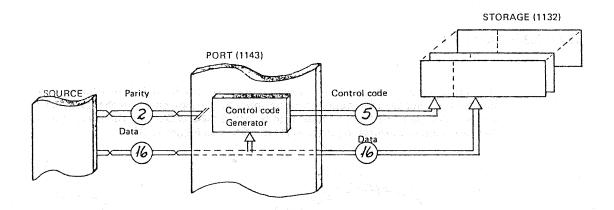

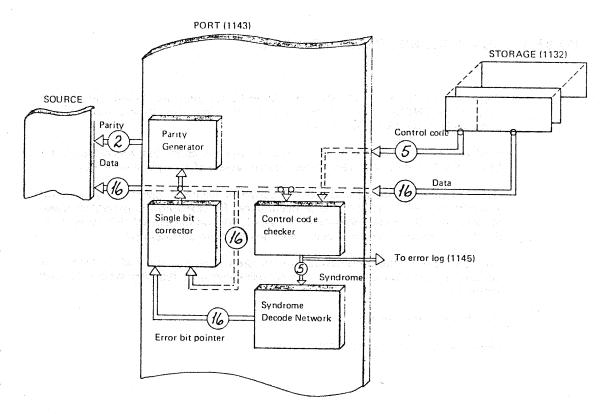

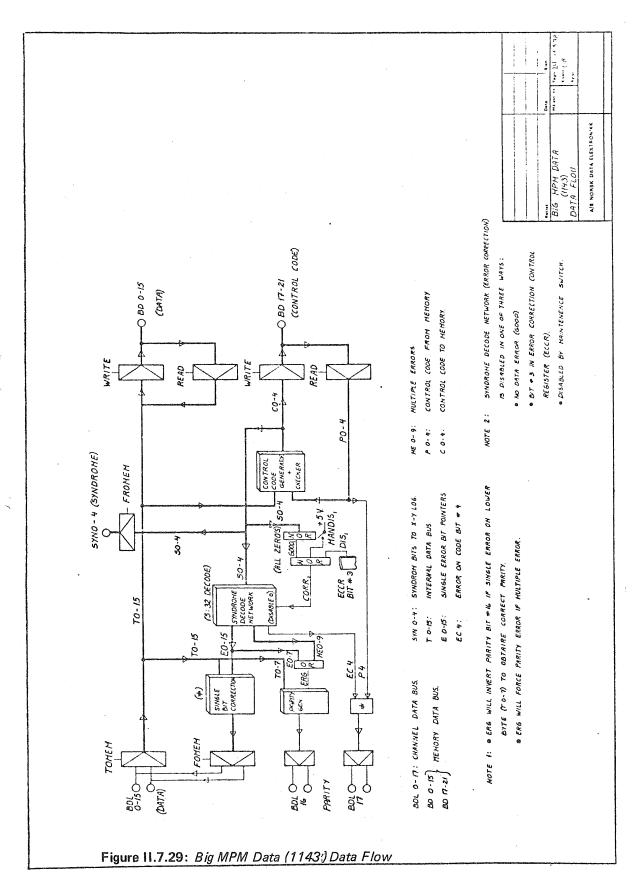

| 11.6.1            | Error Detection and Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 11-6-3          |

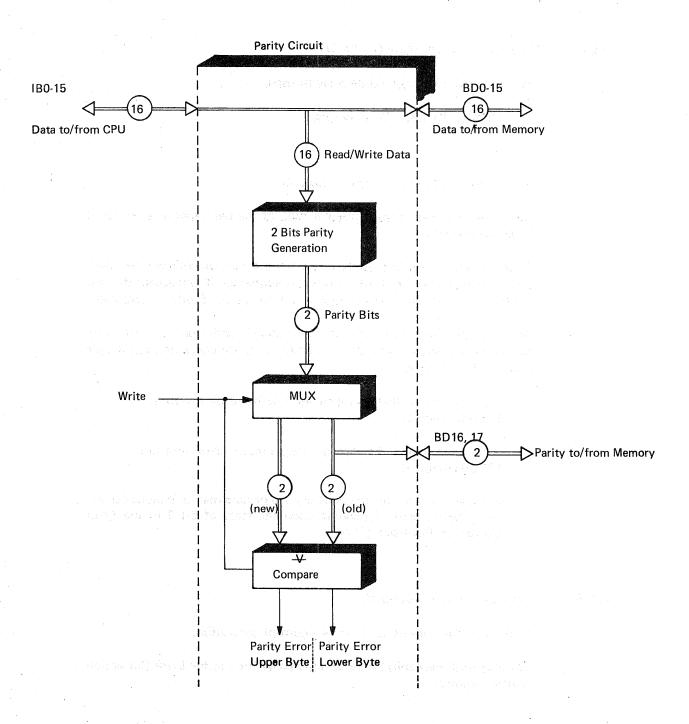

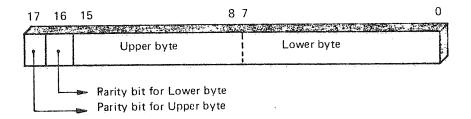

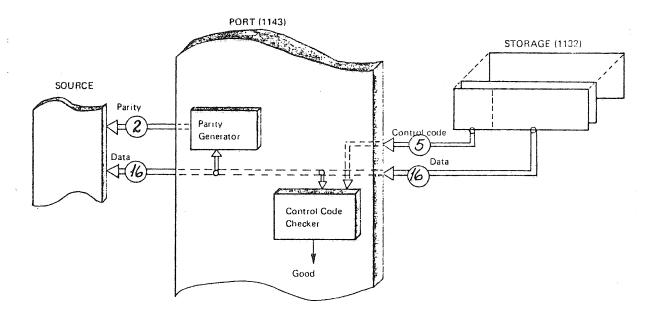

| 11.6.2            | Parity Generation and Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 11-6-7          |

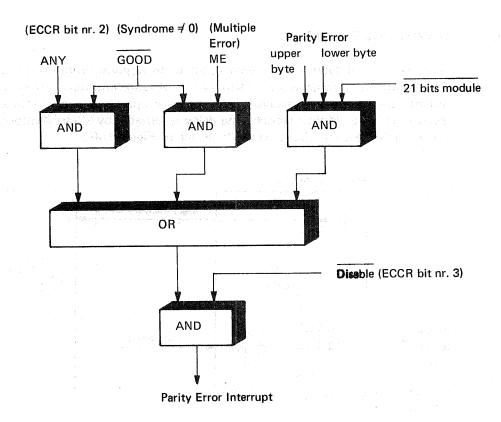

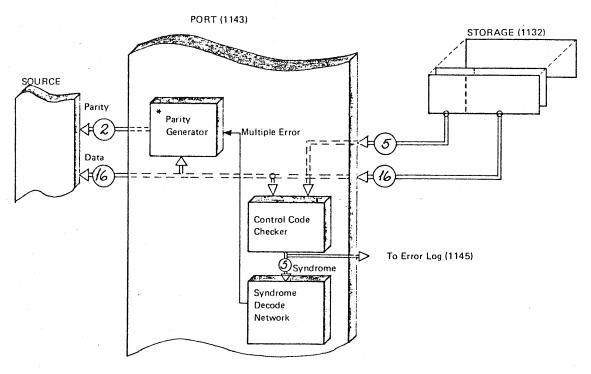

| 11.6.3            | Parity Error Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 11-6-9          |

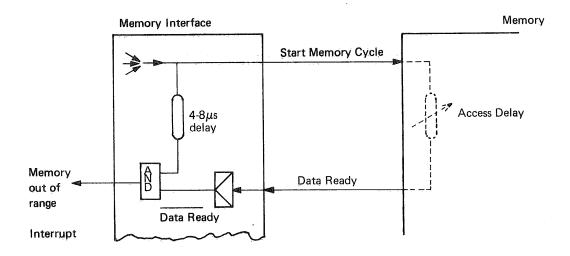

| 11.6.4            | Memory Out of Range — Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 11–6–10         |

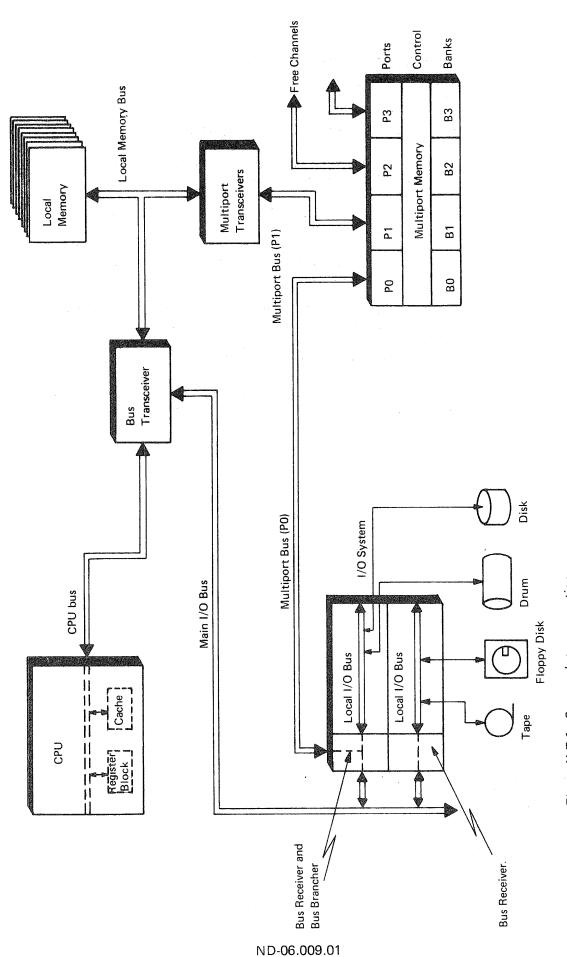

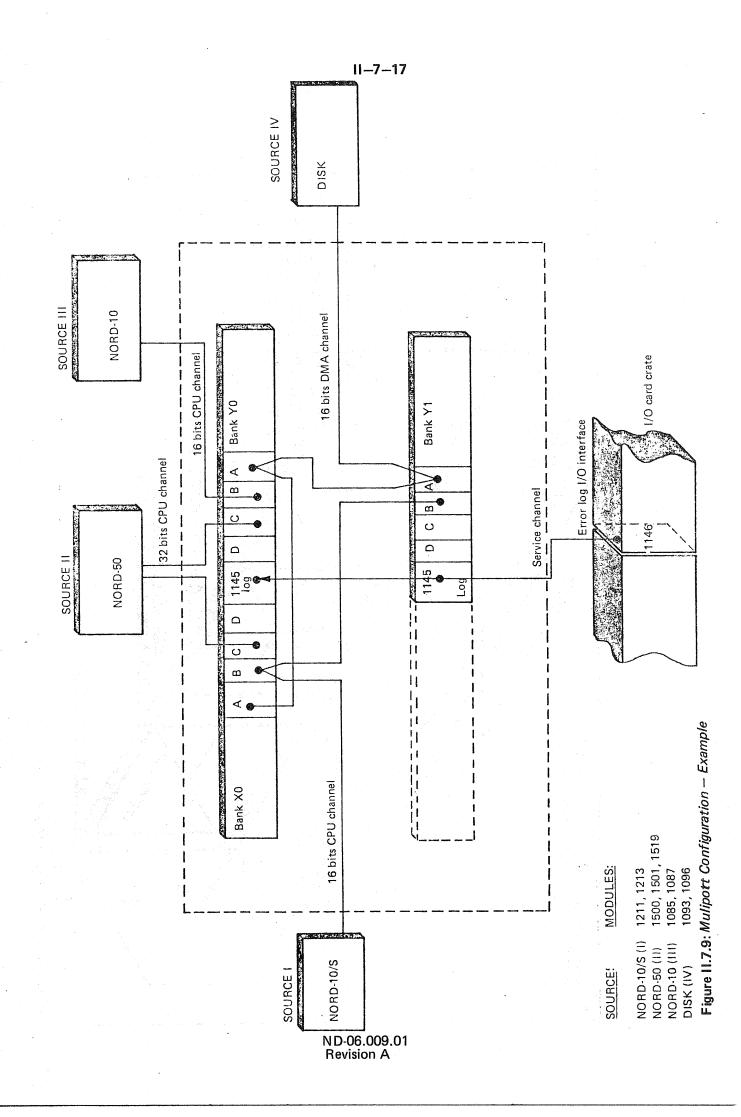

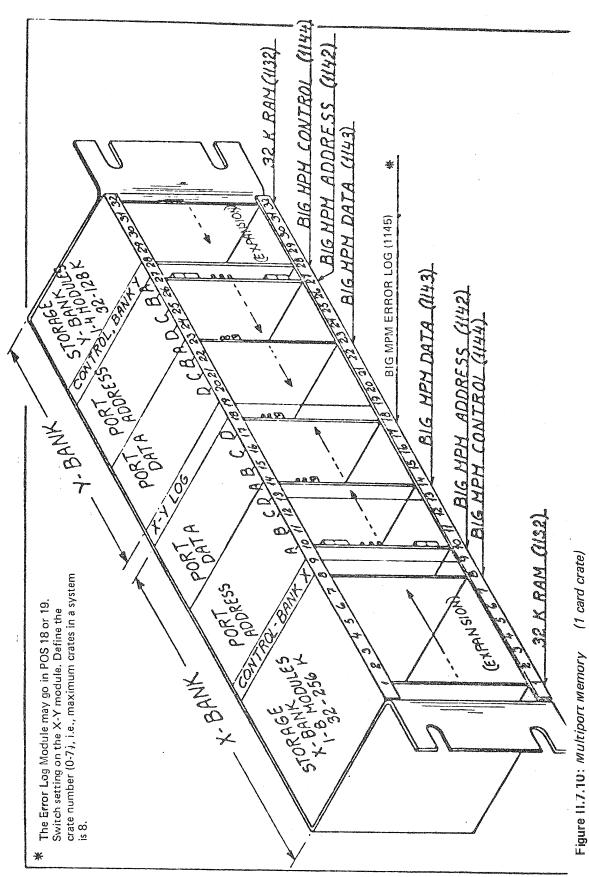

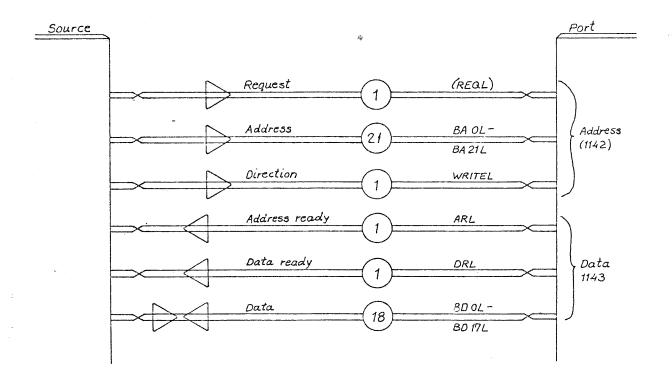

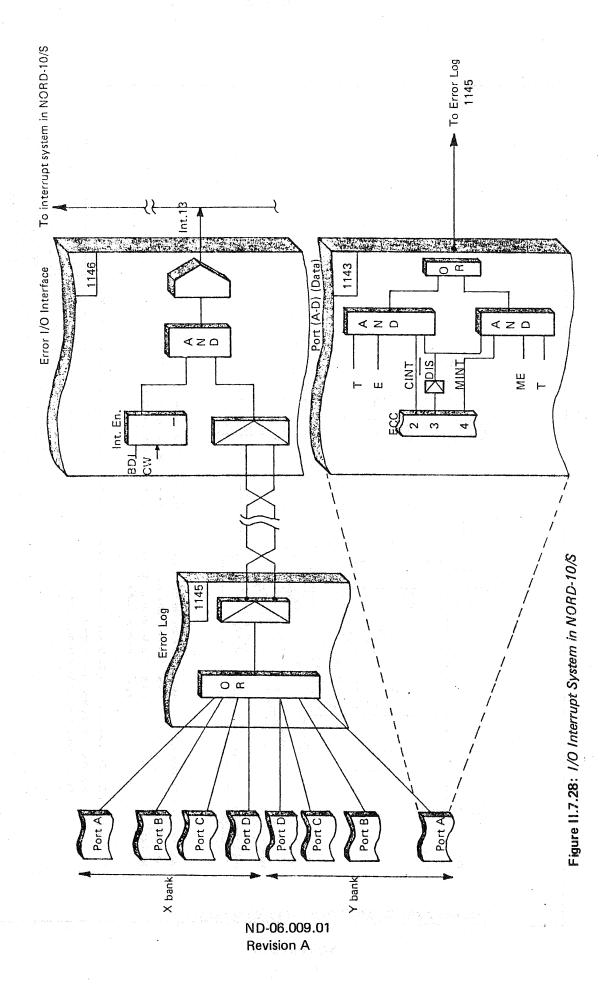

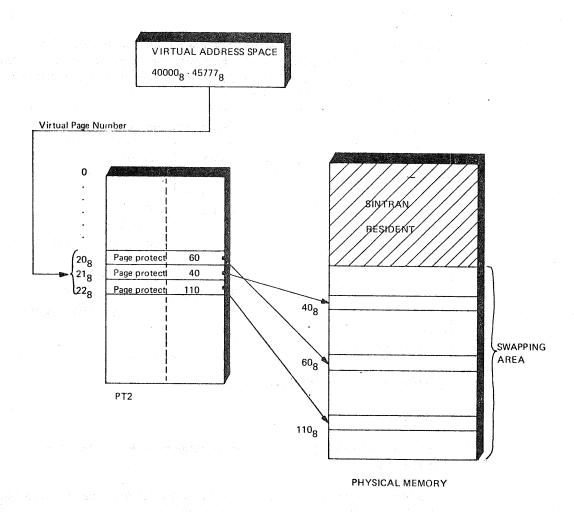

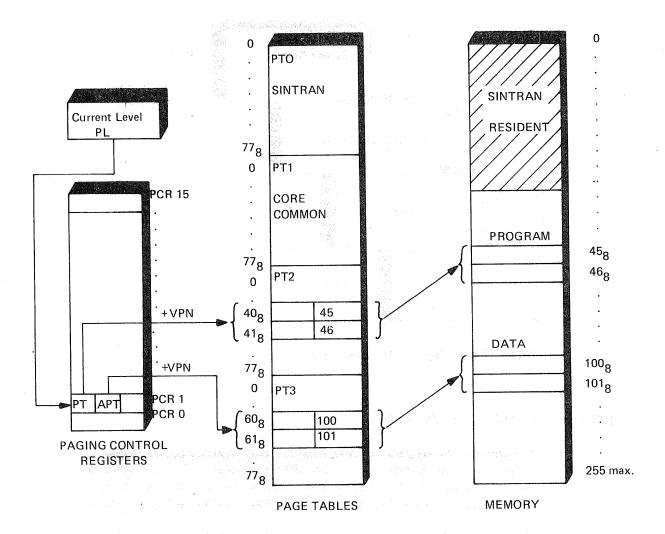

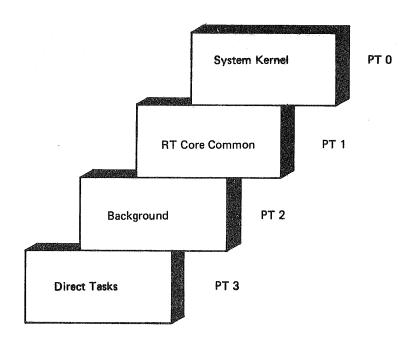

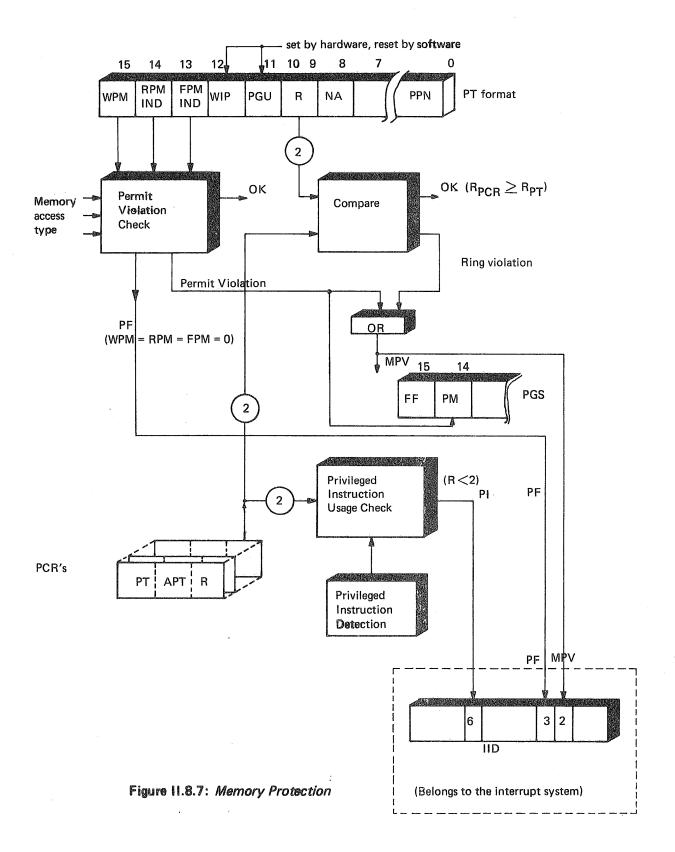

| :<br>: 11.7.1     | Storage Interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 117-2           |

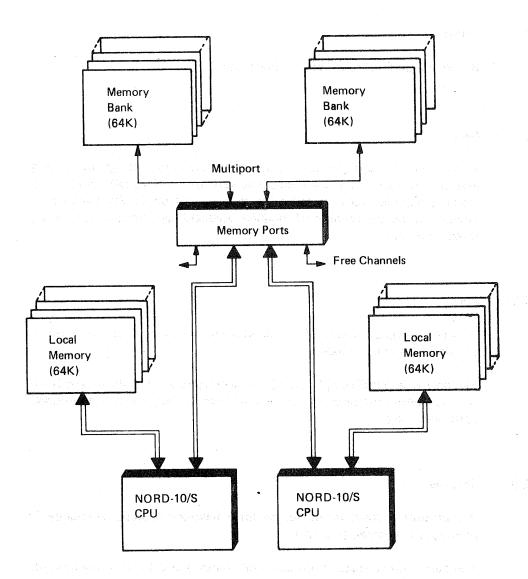

| 11.7.2            | NORD-10/S Two-Processor System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 11-7-3          |

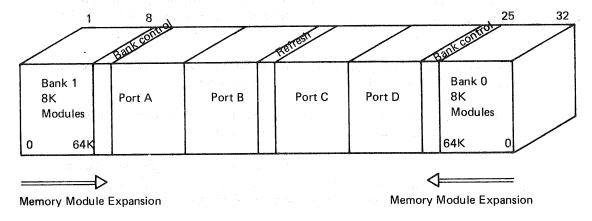

| 11.7.3            | Card Crate Principal Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 11-7-5          |

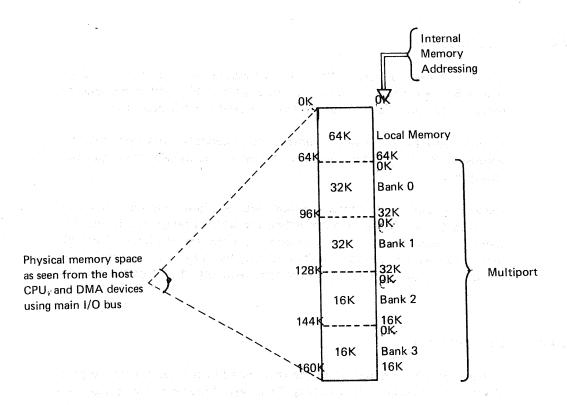

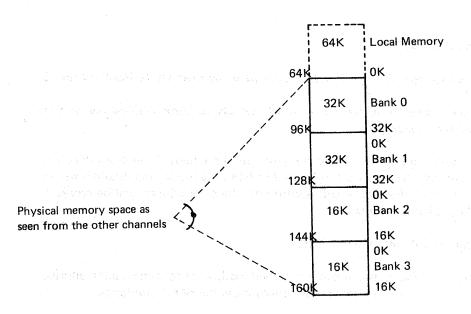

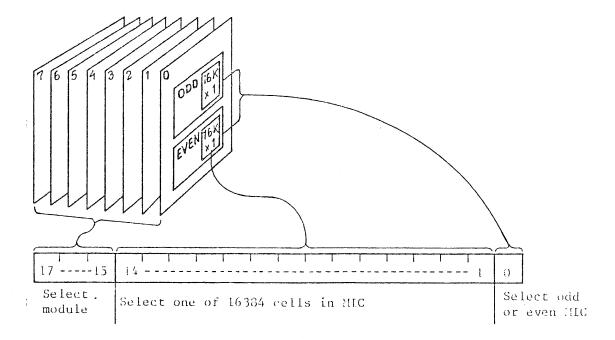

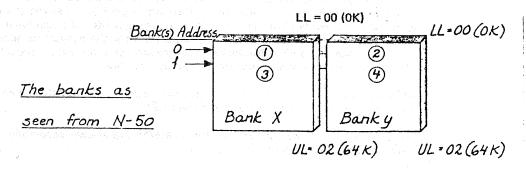

| 11.7.4            | Physical Memory Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   | 1177            |

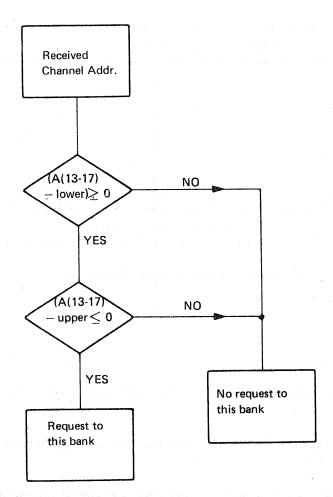

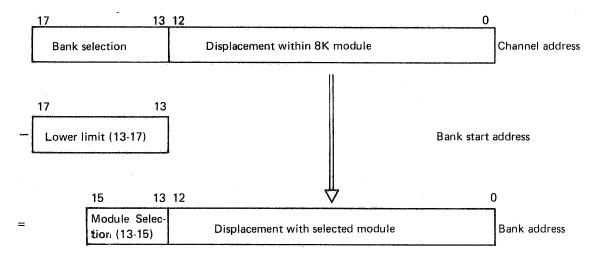

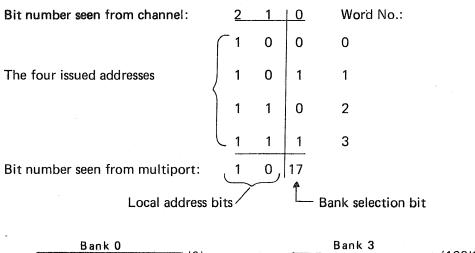

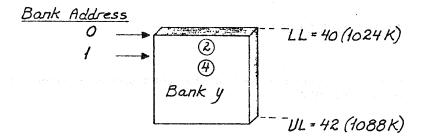

| 11.7.5            | Bank Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 1179            |