High Level Data Link Control (HDLC) Interface

TALKS I

# NORSK DATA A.S

Scanned by Jonny Oddene for Sintran Data © 201

## High Level Data Link Control (HDLC) Interface

Scanned by Jonny Oddene for Sintran Data © 2010

| <b>REVISION RECORD</b> |  |  |  |  |  |  |  |  |  |

|------------------------|--|--|--|--|--|--|--|--|--|

| Notes                  |  |  |  |  |  |  |  |  |  |

| Original Printing      |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

| · · ·                  |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

|                        |  |  |  |  |  |  |  |  |  |

HDLC – High Level Data Link Control Interface Publication No. ND-12.018.01

NORSK DATA A.S.

Lørenveien 57. Postboks 163 Økern, Oslo 5, Norway

#### MAIN CONTENTS

+++

#### Section:

#### PART I - HDLC INTERFACE

- 1.1 Introduction

- 1.2 HDLC Configuration, ND No.720 and ND No.723

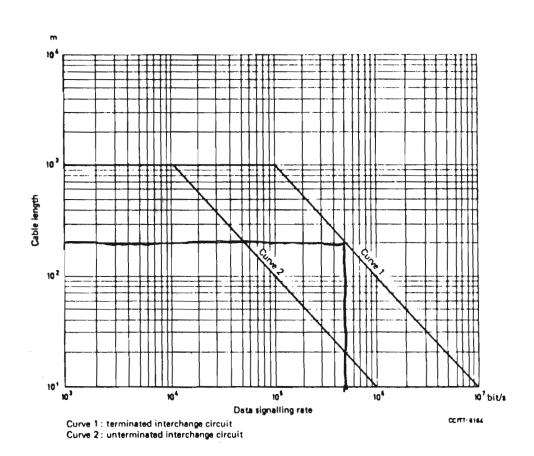

- HDLC Interface Versus Communication Standards 1.3

#### PART II -- FUNCTIONAL DESCRIPTION

- II.1 Introduction

- 11.2

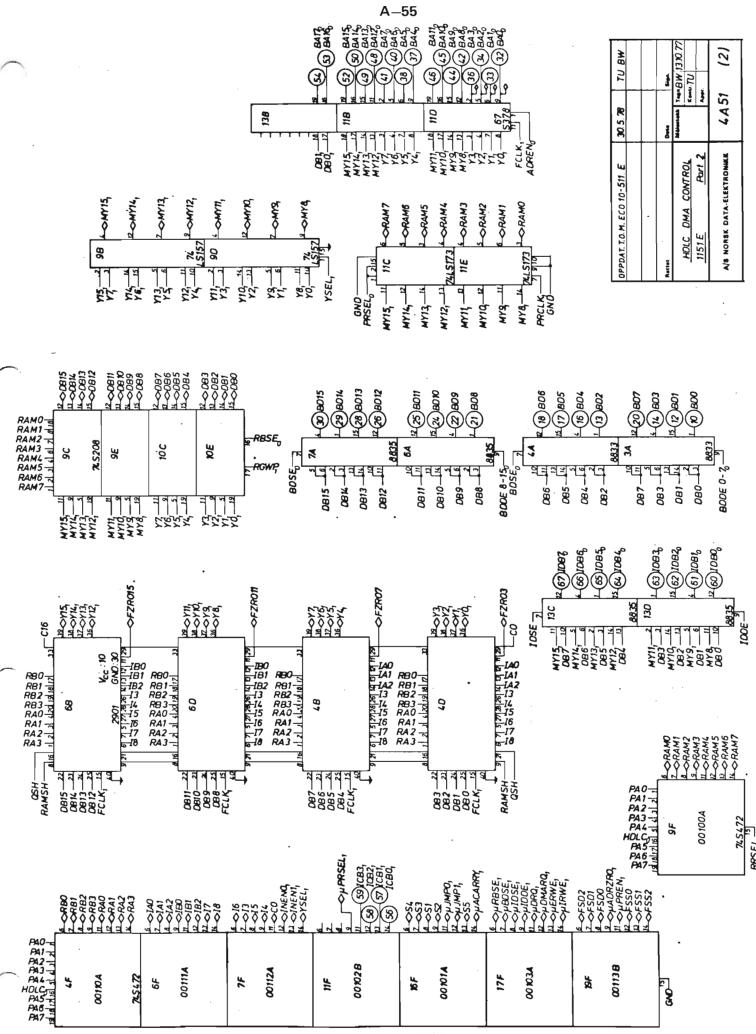

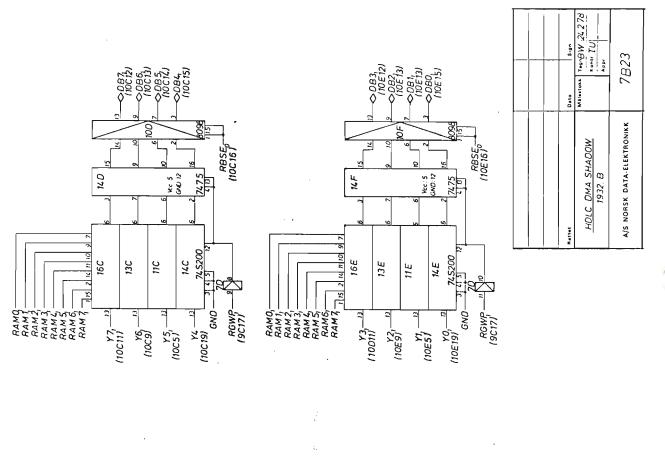

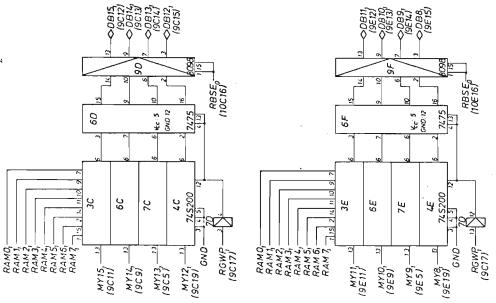

- HDLC Data HDLC DMA Control 11.3

#### APPENDIX A

- HDLC I/O CONFIGURATION A.1

- Detailed Description of the MultiProtocol Communication Controller A.2

- A.3 HDLC Line Connection and Driver Specifications

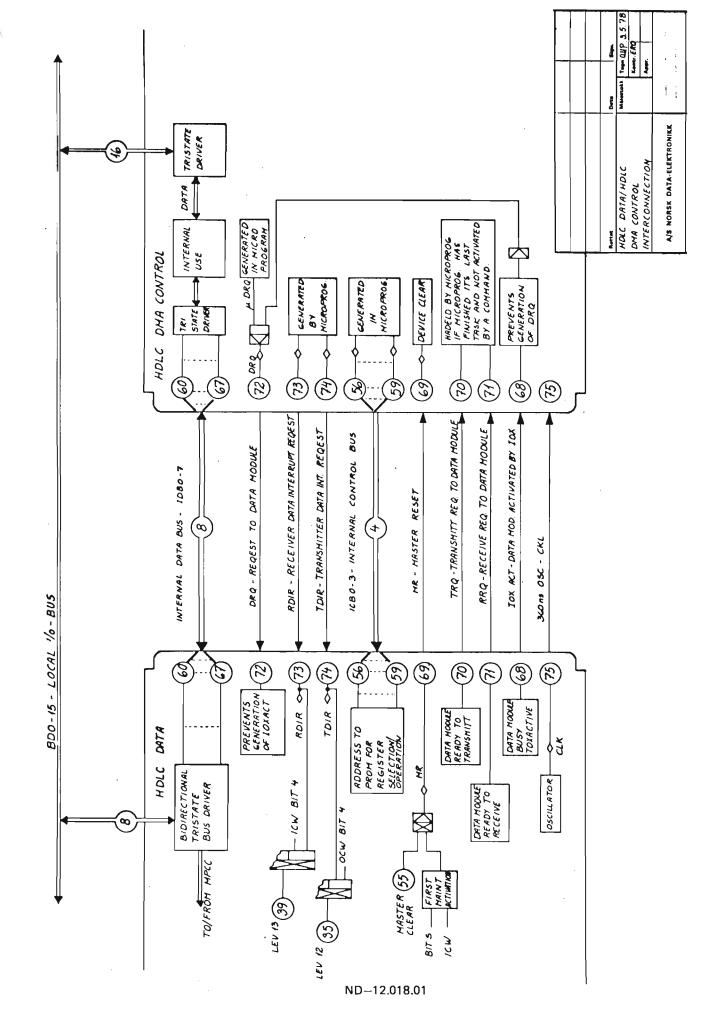

- A.4 HDLC DATA - HDLC DMA Control Interconnection

- A.5 **Programming Specifications**

- HDLC Logical Diagrams A.6

Scanned by Jonny Oddene for Sintran Data © 2010

## HDLC INTERFACE PART I

## DETAILED CONTENTS

+ + +

| Section:                                                                  |                                                                                                                                                                                                                        | Page:                                                                           |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| l.1                                                                       | INTRODUCTION                                                                                                                                                                                                           | 1-1-1                                                                           |

| 1.2                                                                       | HDLC CONFIGURATION, ND NO.720 AND ND NO.723                                                                                                                                                                            | 1-2-1                                                                           |

| 1.2.1                                                                     | HDLC I/O Interface ND No.723 Module 1141                                                                                                                                                                               | I-2-1                                                                           |

| 1.2.2                                                                     | HDLC Interface (DMA) ND No.720 Modules 1141 and 1151                                                                                                                                                                   | 1-2-2                                                                           |

| 1.3                                                                       | HDLC INTERFACE VERSUS COMMUNICATION<br>STANDARDS                                                                                                                                                                       | 1-3-1                                                                           |

| I.3.1<br>I.3.2<br>I.3.2.1<br>I.3.2.2<br>I.3.2.2<br>I.3.2.2.1<br>I.3.2.2.2 | Introduction<br>Standards<br>Hardware Protocols Electrical and Mechanical Standards<br>Data Link Control Procedures (Link Access Procedures,<br>LAP)<br>Frame Format Standards<br>Communication Procedures             | $ \begin{array}{r}  -3-1  \\  -3-2  \\  -3-3  \\  -3-3  \\  -3-4  \end{array} $ |

| 1.3.3<br>1.3.4<br>1.3.4.1<br>1.3.4.2<br>1.3.4.3                           | HDLC Frame Format<br>Standards Implemented on HDLC Interface<br>Electrical and Mechanical<br>Communication Protocols<br>Transmitting and Receiving Frames in Accordance With<br>HDLC Frame Format Using HDLC Interface | -3-4<br> -3-6<br> -3-6<br> -3-6                                                 |

I--iii

Scanned by Jonny Oddene for Sintran Data © 2010

## I.1 INTRODUCTION

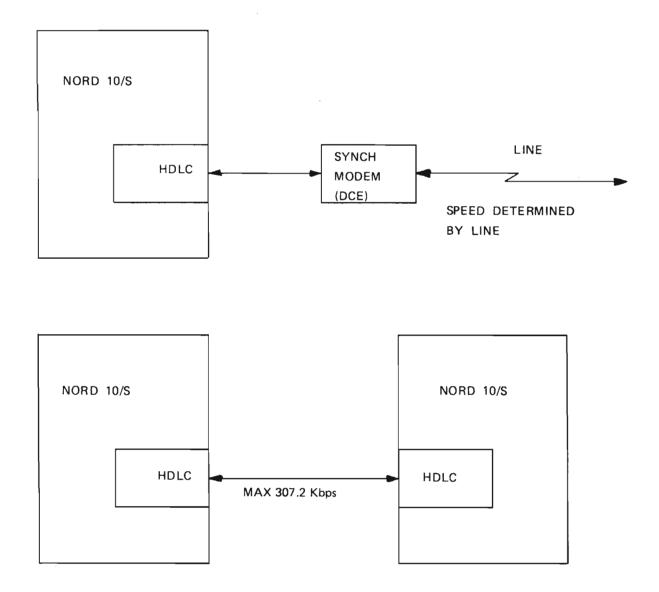

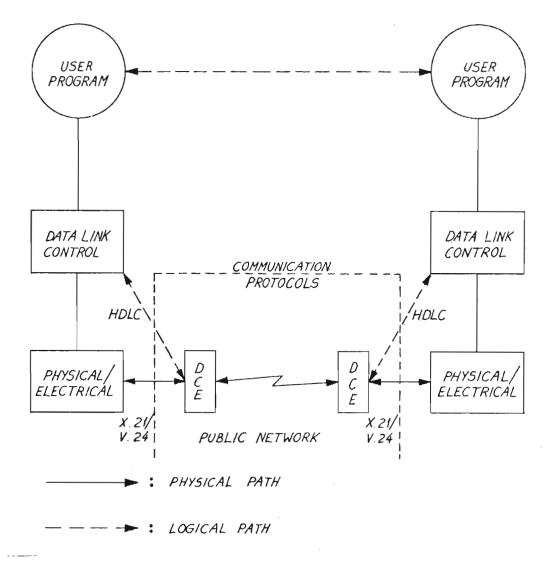

High Level Data Link Control (HDLC) INTERFACE is a synchronous modem interface, however, is also well suited as an intercomputer link interface (See Figure I.1.1).

Figure I.1.1: APPLICATIONS OF HDLC INTERFACE

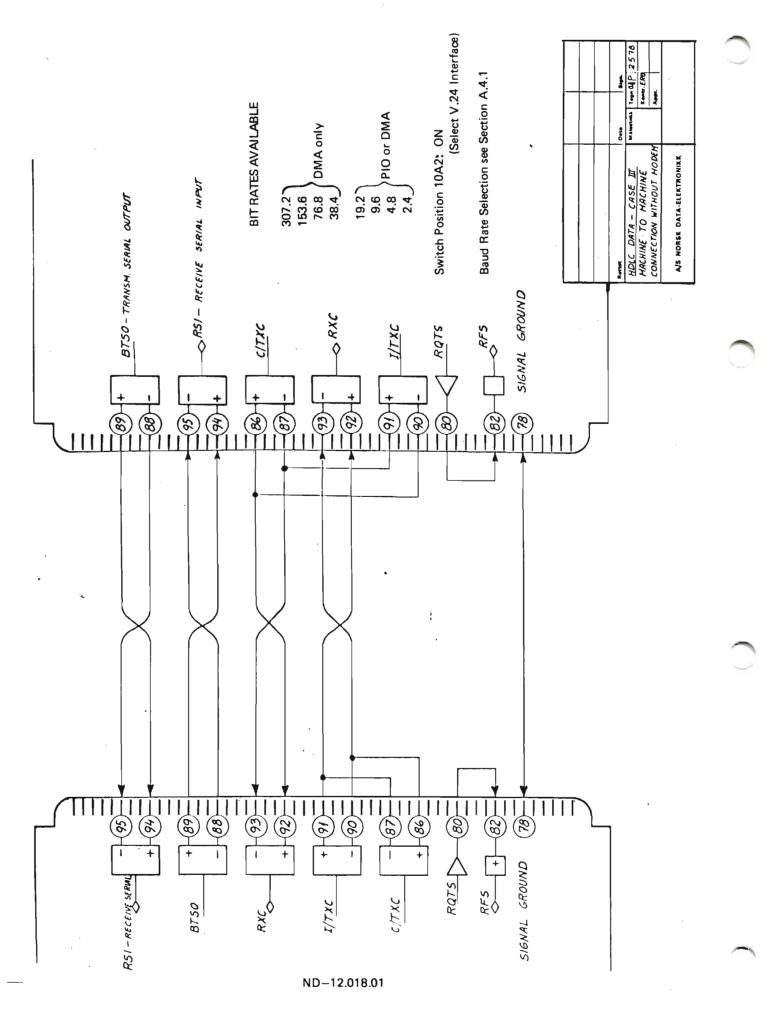

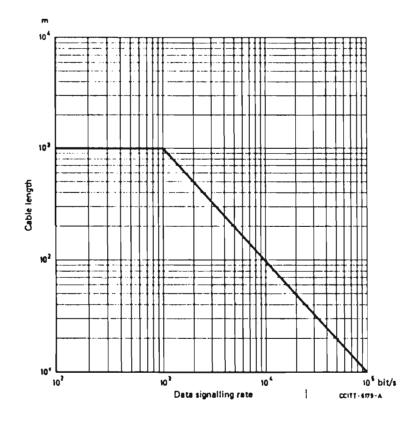

Used as an intercomputer link, HDLC INTERFACE contains internal timing. A strap switches from external timing (from modem) to internal timing which allows transfer rates from 2.4 kbps (kilo bits per second) up to 307.2 kbps.

Independent of the use, dependent of the maximum required speed, HDLC could be delivered as two different products serving the same functions as observed in the external device (modern line, connected computer).

— ND No. 723:

CPU controlled input/output transfer (PIO) Maximum speed 19.2 kbps

— ND No. 720:

Direct Memory Access (DMA) transfer including a DMA controller Maximum speed 307.2 kbps

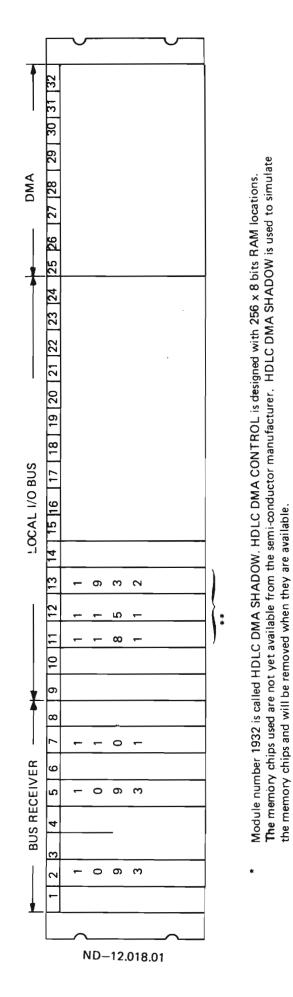

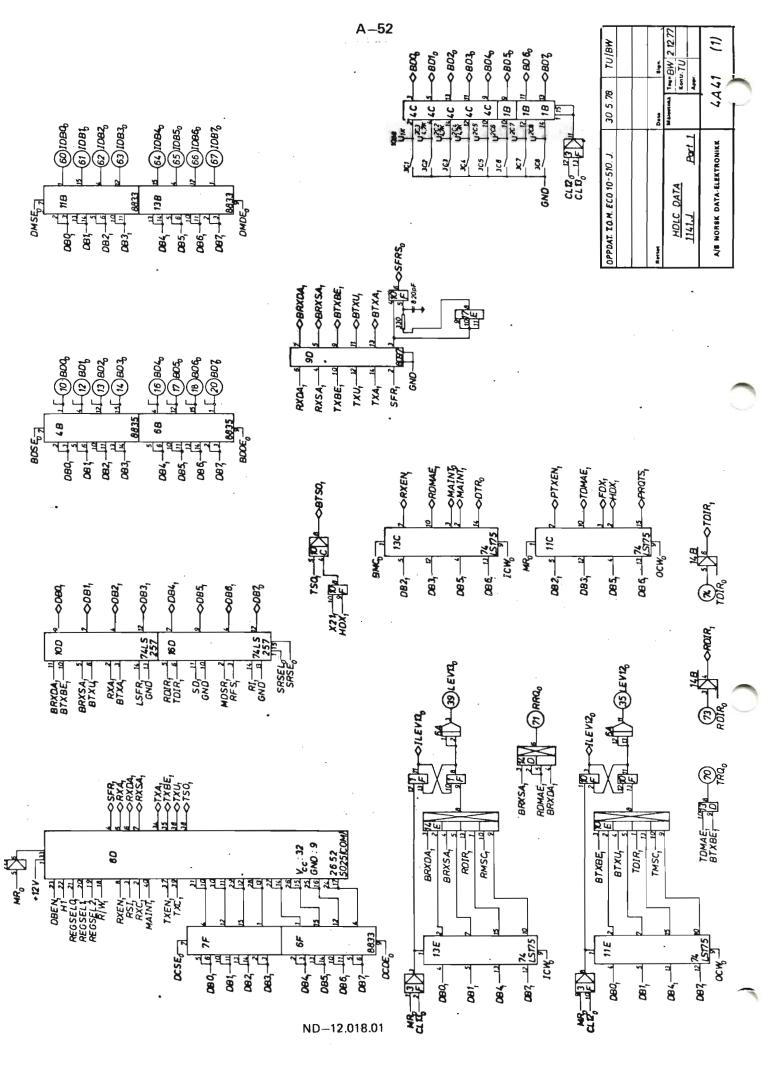

## I.2 HDLC CONFIGURATION, ND No.720 AND ND No.723

1 - 2 - 1

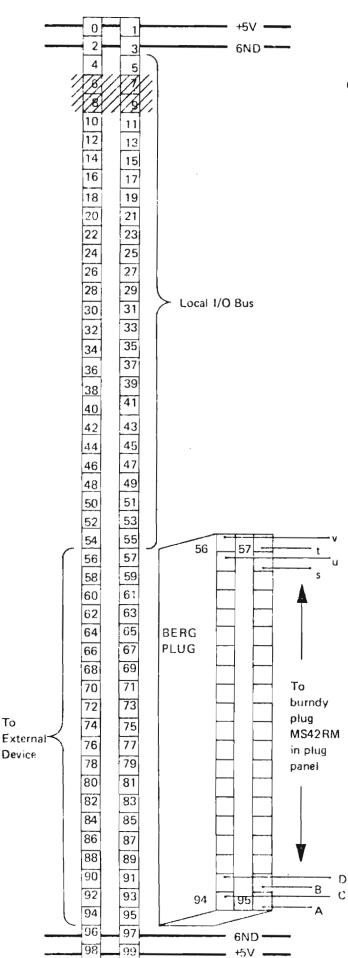

HDLC may consist of two modules both located in the I/O rack.

– 1181 HDLC DATA (ND No. 723)

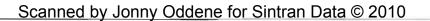

1151 HDLC DMA CONTROL

ND No. 720

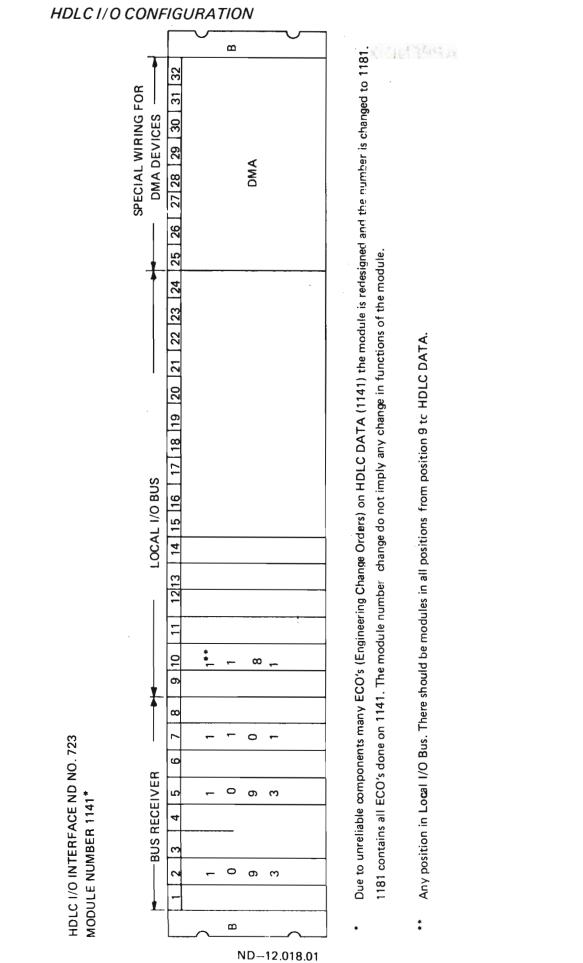

Physical configuration in I/O-rack given in Appendix A1.

## I.2.1 HDLC I/O INTERFACE ND No. 723 MODULE 1181

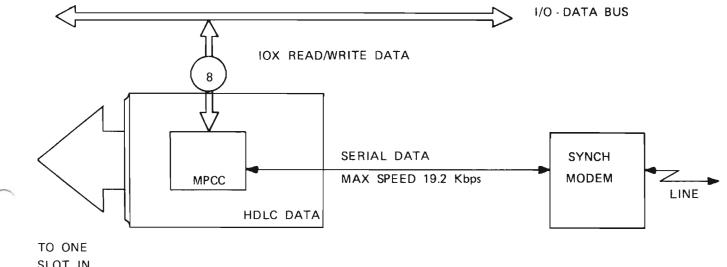

The DATA module may be used as an ordinary Programmed Input/Output (PIO) interface.

The data flow will be as indicated in Figure I.2.1.

SLOT IN I/O - SYSTEM

Figure I.2.1: ND No. 723 DATA FLOW

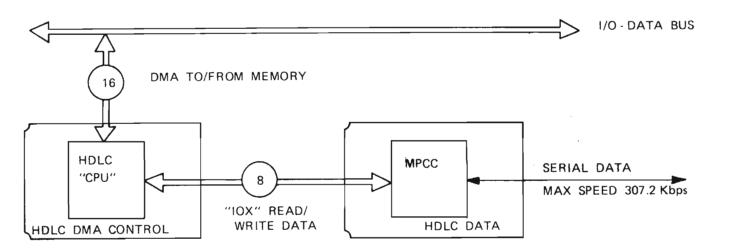

## 1.2.2 HDLC INTERFACE (DMA) ND No. 720 MODULES 1181 AND 1151

As indicated in Figure I.2.1, the maximum speed when using HDLC DATA alone is 19.2 kbps due to heavy CPU load on programmed input/output transfers. In order to increase speed and reduce CPU load to a minimum, the HDLC DMA CONTROL module (1151) could be used together with the DATA module.

The two modules are connected with special wiring in the plug field in the I/O-rack and occupy two slots in the I/O system.

HDLC DMA CONTROL and HDLC DATA working together allows DMA transfer of data from computer memory to the line and vice versa at a maximum speed of 307.2 kbps.

The data flow is shown in Figure 1.2.2.

ND No. 720 occupies two slots in I/O - System

Figure I.2.2: ND No. 720 DATA FLOW

## I.3 HDLC INTERFACE VERSUS COMMUNICATION STANDARDS

## I.3.1 INTRODUCTION

As a communication adaptor HDLC contains more communication standards implemented in hardware than any other designed at NORSK DATA. This is a consequence of advances in integrated circuit technology and international standardization work.

All hardware related to communication standards is designed on HDLC DATA. That means that there is no difference between ND No. 720 (DMA version) and ND No. 723 (PIO version) observed from the network. The difference is seen on the CPU load. (See Functional Description Part II).

## I.3.2 STANDARDS

The involvement of two or more users and equipment from more than one manufacturer in data communication systems gives an increased need of a compatible method for connecting all of it together, an interface protocol.

These protocols may be divided into levels (See Figure 1.3.1.)

Figure I.3.1: INTERFACE STANDARDS

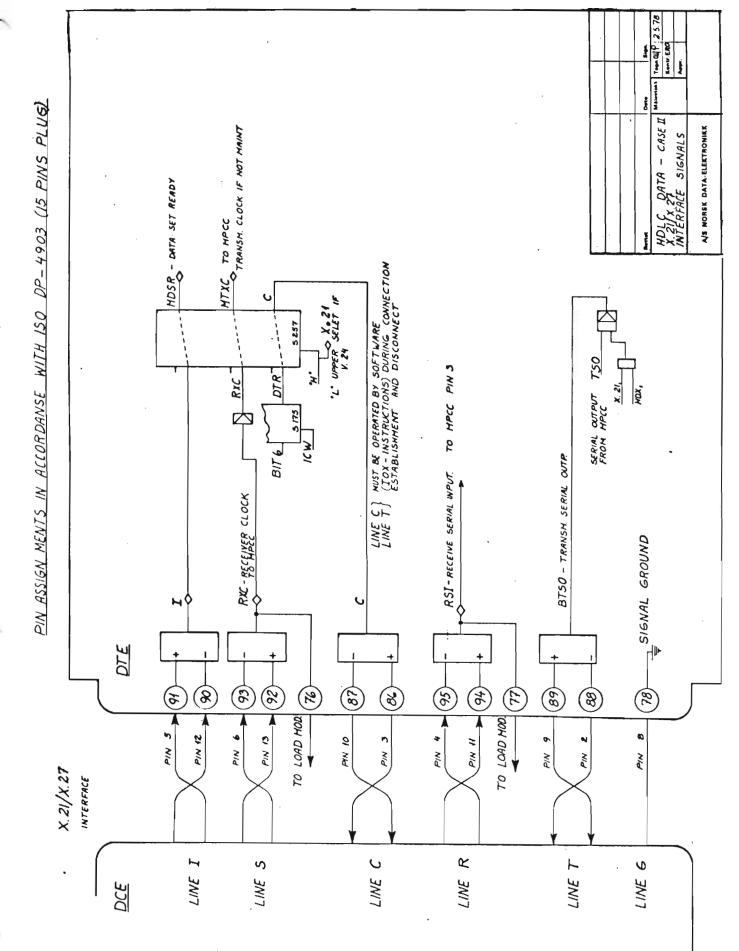

### 1.3.2.1 Hardware Protocols (Electrical and Mechanical Standards)

These interfaces apply to the physical connection between user equipment (DTE) and data communication equipment (DCE, modem).

Possible interface standards are as follows:

- a) CCITT V.24/V.28 and EIA RS-232c

- V.35 (wide band transmission)

For connection to the telephone network

- b) CCITT X.21 bis (V.28 signal levels)

- X.21 (X.27 signal levels)

For connection to the public data network

## 1.3.2.2 Data Link Control Procedures (Link Access Procedures, LAP)

These protocols which have the purpose of controlling the exchange of data are again divided up into the following levels:

- Frame format standards

- Communication procedures

## I.3.2.2.1 Frame Format Standards

Most existing communication procedures transport data in blocks. However, each communication procedure (Byte Control Procedures - BCP) has its own block format, i.e., its own way of signaling "start of block", "end of block", checksum, etc.

One of the first steps in communication standardization is the definition of a uniform transmission format to be used for data and control information.

A transmission block is called a *frame* and a frame contains beginning and ending markers, control information, optional data and a checksum.

The internationally accepted HDLC frame format is fully defined in ISO IS3309.2 standard. This procedure allows full bit sequency transparent data transmission and is referred to as a Bit Oriented Procedure (BOP) (See Section 3.3).

At frame level HDLC (High Level Data Link Control) is fully compatible with SDLC (Synchronous Data Link Control) and with ADCCP (Advanced Data Communication Control Procedure).

## **I.3.2.2.2** Communication Procedures

The standardization of communication procedures is not as easy as the standardization of a frame format. However, new standard procedures are emerging. SDLC procedures have existed for some time, HDLC procedures are being defined by CCITT and the X25 recommendation describes a procedure to be used in public packet switching networks.

All the new procedures will, however, use the HDLC frame format.

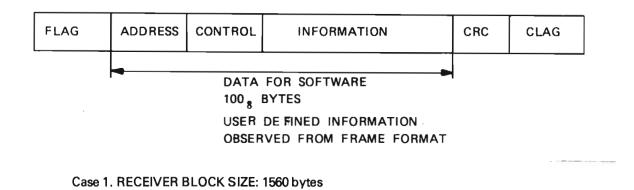

## I.3.3 HDLC FRAME FORMAT

The HDLC frame format is depicted below.

| FLAG     |   |   |   |     | FLAG     |

|----------|---|---|---|-----|----------|

| 01111110 | А | С | - | FCS | 01111110 |

The frame consists of:

1. A special bit sequence call, "flag", that marks the beginning of the frame. The end of the frame is also marked by such a flag.

The flag sequence consists of one zero bit, six one-bits and a zero bit.

The contents of the frame between the opening and the closing flag shall not contain a flag sequence. To guarantee this, the transmitter inserts an extra zero-bit following five consecutive one-bits. These inserted zero-bits are removed by the receiver. These extra bits are called "transparency bits".

2. An 8-bit byte called Address-Byte

This field is meant as a station address, but the contents or use are not prescribed in the frame standard.

3. An 8-bit byte called Control-Byte

This field is intended for link management information, but the frame standard does not describe its use or contents.

4. An Information field

The information field may be any length, and may also be absent. The contents of the information field are not prescribed.

5. A 16-bit Frame Check Sequence (FCS)

This field contains a 16-bit Cyclic Redundancy Check computed over the bits between the last bit of the opening flag and the first bit of FCS.

Transparency bits are removed before the FCS is computed.

6. The closing flag that signals frame end

The closing flag of one frame may be identical to the opening flag of the next frame.

#### Frame Size:

A valid frame shall contain at least 48 bits (Flag A, C, FCS).

There is no prescribed upper limit to the frame size. However, frame size is limited by the properties of transmission channels and the 16-bit FCS computation.

## 1.3.4 STANDARDS IMPLEMENTED ON HDLC INTERFACE

On HDLC DATA the following communication standards are hardware implemented.

1.3.4.1 Electrical and Mechanical

Strap selectable:

- V.24/V.28,RS-232C

V.35

Telephone Network (V.series modem)

X.21-bis (V.28-signal levels) or

- X.21 (X.27 signal levels)

public data network

## 1.3.4.2 Communication Protocols

## Selectable From Program:

- Byte Oriented Procedures

Including automatic SYN character detection/generation

- Bit Oriented Procedures (BOP); HDLC (ISO-IS 3309), SDLC (IBM), ADCCP (ANSI) including:

- automatic bit stuffing/stripping

- automatic frame character detection/generation

- valid frame protection

- residue handling

- selectable:

- byte length 1-8 bits

- error checking CRC (CRC-16, CCITT-0, CCITT-1) NONE

- primary/secondary address mode

- idle mode

- point to point, multi-drop, loop configuration

## 1.3.4.3 Transmitting and Receiving Frames in Accordance With HDLC Frame Format Using HDLC Interface

The reason for calling the interface HDLC is related to the fact that frames in accordance with HDLC frame format are generated automatically in hardware when activated from driver software.

#### TRANSMISSION

When transmitting, software only has to know what should be in the address, control and information field. Observed from the frame format, these fields could contain any user defined information.

In order to pack the information into HDLC frame format before transmitting it on the line, HDLC DATA (which handles the procedure) must be activated by some control signals.

The control function is to first give the command Transmit Start Of Message (TSOM, i.e. send opening flag) and when all information in the frame is transmitted give the command Transmit End Of Message (TEOM, i.e. send closing flag).

The Cyclic Redundancy Checksum (CRC) is generated automatically and put into the frame when command TEOM is given.

#### RECEIVING

When receiving HDLC DATA will give status on Received Start Of Message (RSOM, i.e. opening flag received) and Received End Of Message (REOM, i.e. end marker of the frame is received).

Then software knows that all information received between RSOM and REOM has the sequence; address, control, information and CRC; that means, in accordance with HDLC frame format.

Therefore, successful communication against the line is related to successful control of HDLC DATA.

In the data phase, that is:

- Load X bits bytes (1≤X≤8) on output

- Read X bits bytes ( $1 \le X \le 8$ ) on input

- Control of frame formatting functions (TSOM, TEOM and RSOM, REOM)

This could be done by NORD 10/S (HDLC in PIO version ND No. 723) introducing some overhead or by the DMA module (HDLC DMA, ND No. 720) reducing overhead to a minimum (See Part II).

Scanned by Jonny Oddene for Sintran Data © 2010

PART II FUNCTIONAL DESCRIPTION

#### DETAILED CONTENTS

+ + +

|                                                              |                                                                                                                                  | Ū                                                      |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| II.1                                                         | INTRODUCTION                                                                                                                     | II-1-1                                                 |

| II.2                                                         | HDLC DATA                                                                                                                        | II-2-1                                                 |

| II.2.1<br>II.2.1.1                                           | Control of HDLC Data<br>Intialization of HDLC DATA, i.e. Loading of Mode Selection                                               | II-2-4                                                 |

|                                                              | Registers                                                                                                                        | 11-2-6                                                 |

| II.2.1.2<br>II.2.1.2.1<br>II.2.1.2.2                         | HDLC DATA in the Data Phase<br>Receive (Input) Channel<br>Transmit (Output) Channel                                              | -2-9<br>  -2-10<br>  -2-15                             |

| II.3                                                         | HDLC DMA CONTROL                                                                                                                 | ∥_3_1                                                  |

| .3.1<br>  .3.2<br>  .3.2.1<br>  .3.2.2<br>  .3.2.3<br>  .3.3 | Introducton<br>Control of the DMA Processor (The Commands)<br>Initializaton<br>Data Transfer<br>Maintenace<br>HDLC DMA Structure | -3-1<br>  -3-2<br>  -3-3<br>  -3-5<br>  -3-6<br>  -3-7 |

| II.3.3.1<br>II.3.3.1.1                                       | The List Structure<br>Receiver List                                                                                              | -3-7                                                   |

| II.3.3.1.2                                                   | Transmitter List                                                                                                                 | Ⅱ_3_8<br>Ⅱ_3_14                                        |

## Section:

ND-12.018.01

Page:

11-1-1

## II.1 INTRODUCTION

As mentioned HDLC INTERFACE may consist of the following two modules:

- HDLC DATA (PIO Version)

DMA Version

--- HDLC DMA CONTROL

HDLC DATA may be used alone as a Programmed Input/Output interface. HDLC DMA CONTROL can *only* operate together with HDLC DATA.

## II.2 HDLC DATA

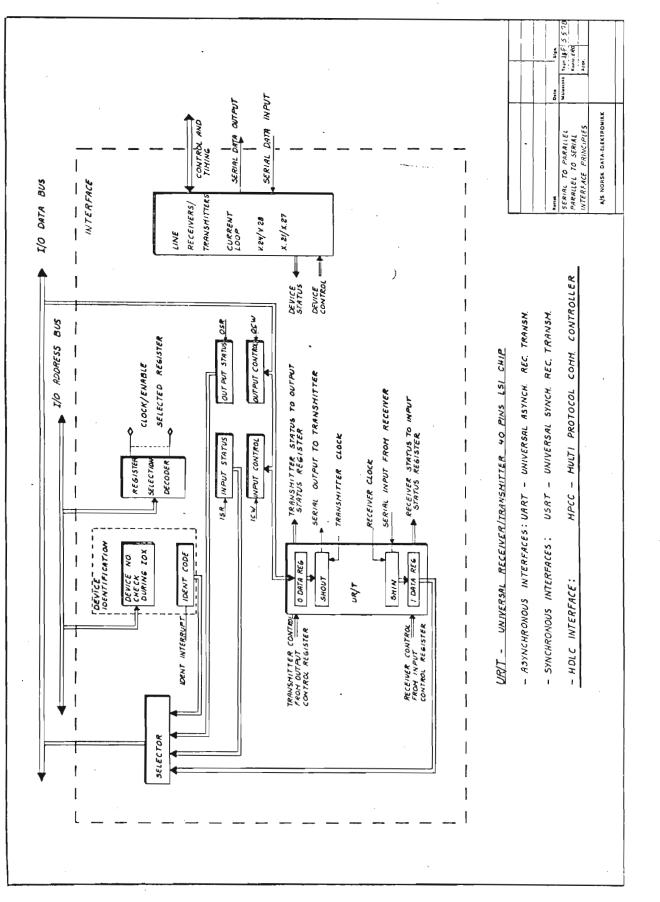

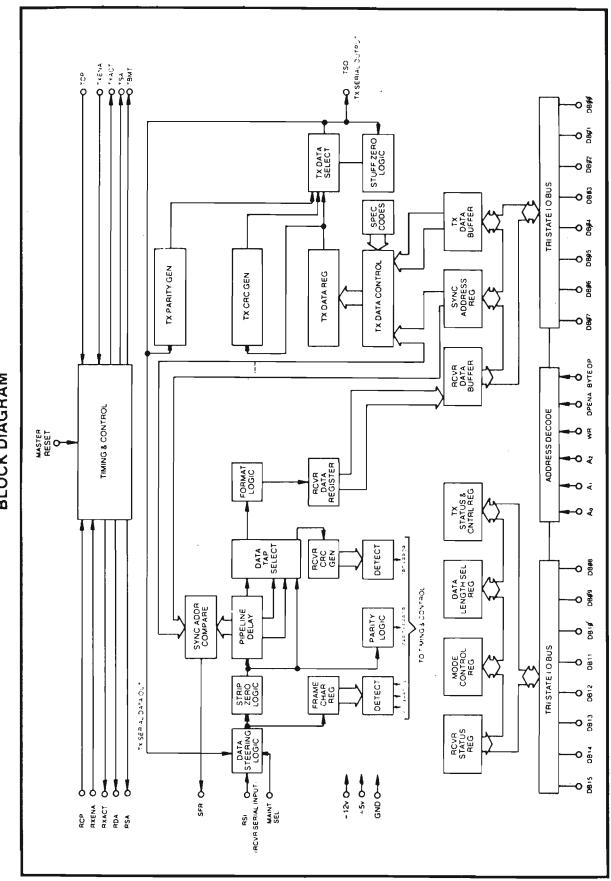

The HDLC DATA module is designed after the same basic principles as other parallel to serial (output to line), serial to parallel (input from line) interfaces designed at NORSK DATA (See Figure II.2.1).

The module contains the following:

- a device identification part including switches for setting of DEVICE NO. and IDENT CODE

- receivers for local I/O-address bus and receivers/transmitters for local I/O-data bus

- a 40 pins LSI chip, the MultiProtocol Communication Controller MPCC, which performs:

- parallel to serial convertion on output data

- serial to parallel convertion on input data

- -- selectable protocol

- byte oriented (BCP) including automatic generation/detection of SYN character. (Block formatting must be done by driver software)

or

- bit protocols (BOP): HDLC,SDLC,ADCCP including automatic frame format generation

- automatic bit stuffing/stripping

- automatic frame character detection/generation

- valid frame protection

- residue handling

- selectable:

- byte length 1-8 bits

- error checking CRC (CRC-16,CCITT-0,CCITT-1) NONE

- primary/secondary address mode

- idle mode

- point to point, multi-drop, loop configuration

For detailed description of the MPCC see Appendix A2.

- line adapter for connection to Data Communication Equipment (DCE, Modem) in accordance to standards

- V.24/V.28, RS 232c

telephone network

OR

– V.35

- X.21 bis (V.28 signal levels) public data

- X.21 (X.27 signal levels) network

For detailed description of line connection, pin configurations etc., see Appendix A3.

special timing circuitry for inter-computer link connection, see also Appendix A3.

In addition HDLC DATA contains circuitry for connection to the DMA CONTROL module.

Figure II.2.1:SERIAL TO PARALLEL, PARALLEL TO SERIAL INTERFACE PRINCIPLES

ND-12.018.01

11-2-3

11-2-4

The DMA module contains a microprocessor to control the data transfer to/from computer memory and HDLC DATA.

Therefore, HDLC DATA, in fact is designed to interface two processors:

- The NORD 10/S CPU (through standard I/O-system)

- The processor on the DMA module (through special inter-module connection; see Appendix A4)

Observed from the DATA module it makes no difference what processor is active.

That means that the control of HDLC DATA could be done either by NORD 10/S or the DMA processor.

The most effective solution of course is to leave the input/output handling to the DMA processor. Then NORD 10/S CPU will have more time for data processing which is the computers purpose.

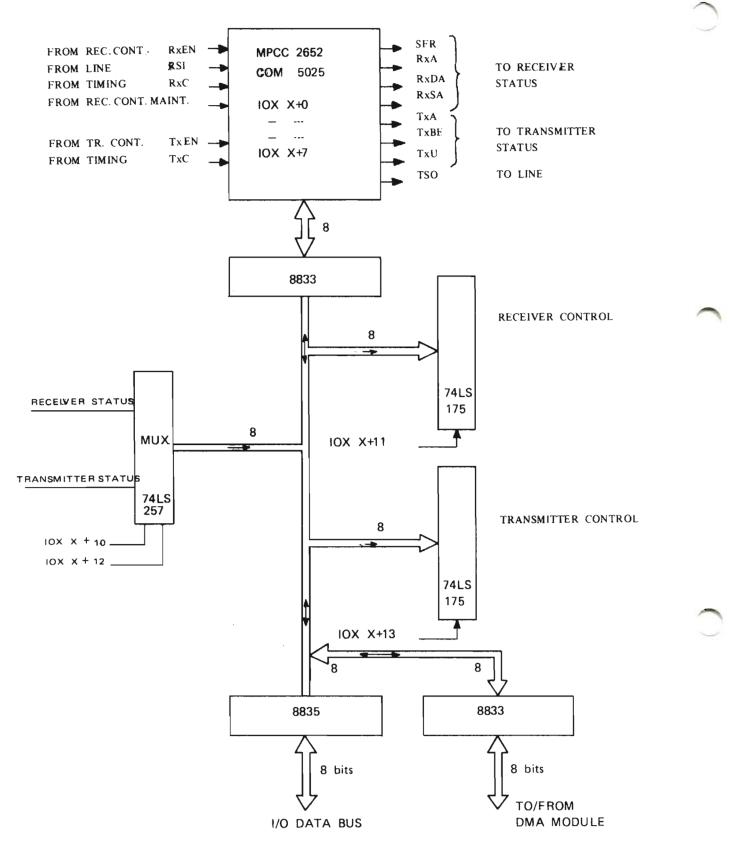

## II.2.1 CONTROL OF HDLC DATA

As mentioned in PART I, Section 3.4.3, successful communication between line and computer is related to successful control of HDLC DATA.

Including input and output data register there are 12 eight bits registers to control the DATA module. All registers could be accessed by IOX instructions (IOX < device no.>  $+ 0-13_8$ ).

Instructions 0-7<sub>8</sub> operate directly on 8 eight bits registers internally in the MPCC.

The instructions  $10_8$ - $13_8$  operate on single line indicators to/from the MPCC, interrupt enabling and modem status information. See Figure II.2.2 and the following description.

11--2--5

Figure II.2.2: HDLC DATA -- BLOCK DIAGRAM

There are five registers related to the output channel, four registers related to the input channel and three registers common for operation mode control.

## **II.2.1.1** Initialization of HDLC DATA, i.e. Loading of Mode Selection Registers

Before enabling input/output transfers to HDLC DATA the module has to be initialized. That means after a MASTER CLEAR or DEVICE CLEAR, to load the mode selection registers.

The mode selection register is held internally in the MPCC to control the operation mode of the chip.

Remember that the MPCC performs the necessary frame formatting functions. Therefore, both a local and remote HDLC interface should be put in the same mode of operation given in the mode registers.

Loading of the mode registers is performed by IOX < device no.> + 1,3,4.

The format and function of the registers is given below:

IOX < DEVICE NO.> + 1

WRITE PARAMETER CONTROL REGISTER (PCR)

FORMAT:

| 15  | 8 | 7   | 6    | 5     | 4    | 3            | 2   | 1 | 0   |

|-----|---|-----|------|-------|------|--------------|-----|---|-----|

| N/A |   | ΑΡΑ | PROT | STRIP | SEL  | IDLE<br>MODE | CRC |   | SEL |

| L   |   |     | SEL  | GA    | AWUL | NODE         | 2   | Ĭ | ^   |

#### BIT 0-2 ERROR CHECK SELECTION

| 0-2 | CRC<br>SEL | BOP<br>BCP | Error Control Mode       | 2 | 1 | 0 | Mode | Char.Length |

|-----|------------|------------|--------------------------|---|---|---|------|-------------|

|     |            |            | CRC-CCITT present to 1's | 0 | 0 | 0 | BOP  | 1-8         |

|     |            |            | CRC-CCITT present to 0's | 0 | 0 | 1 | BOP  | 1-8         |

|     |            |            | Not used                 | 0 | 1 | 0 |      |             |

|     |            |            | CRC-16 present to 0's    | 0 | 1 | 1 | BCP  | 8           |

|     |            |            | VRC odd                  | 1 | 0 | 0 | BCP  | 5-7         |

|     |            |            | VRC even                 | 1 | 0 | 1 | BCP  | 5-7         |

|     |            |            | Notused                  | 1 | 1 | 0 |      |             |

|     |            |            | No error control         | 1 | 1 | 1 | BCP  | 5-8         |

|     |            |            |                          |   |   |   |      |             |

ECM should be loaded by the processor during initialization or when both data paths are idle.

#### BIT 3 IDLE MODE SELECTION

3 IDLE

Determines line fill character to be used if transmitter underrun occurs (TxU asserted and TERR set) and transmission of special characters for BOP/BCP.

BOP IDLE=0, transmit ABORT characters during underrun and when TABORT = 1.

IDLE=1, transmit FLAG characters during underrun and when TABORT=1.

BCP IDLE = 0 transmit initial SYNC characters and underrun line fill characters from the S/AR. IDLE = 1 transmit initial SYNC characters from TxDR (transmitter Data Register) and marks TxSO (transmitter serial output) during underrun.

#### BIT 4 SELECT SECONDARY ADDRESS MODE

Used in ring networks to select secondary station (remote site) dependent of received address compared with sync/address register (See IOX <device no.> 3).

4 SAM BOP Secondary Address Mode = 1 if the MPCC is a secondary station. This facilitates automatic recognition of the received secondary station address. When transmitting, the processor must load the secondary address into TxDR (Output Data Register). SAM = 0 inhibits the received secondary address comparison which serves to activate the receiver after the first non-FLAG character has been received.

#### BIT 5 STRIP GO AHEAD/SYNC

Used in ring networks (BOP) to terminate message (frame).

- 5 SS/GA BOP Strip SYNC/Go Ahead. Operation depends on mode. For loop mode only. SS/GA = 1 permits GA character to terminate a received message. When a GA is detected REOM and RAB/GA will be set and the processor should terminate the repeater function. SS/GA=0 permits only a FLAG or ABORT character to terminate a message.

- BCP SS/GA=1, causes the receiver to strip SYNC's immediately following the first two SYNC's detected. SYNC's in the middle of a message will not be stripped. SS/GA=0, presents any SYNC's after the initial two SYNC's to the processor.

#### BIT 6 PROTOCOL SELECTION

| 6 | PROTO |     | Determines MPCC Protocol mode |

|---|-------|-----|-------------------------------|

|   |       | BOP | PROTO = 0 BOP                 |

|   |       | BCP | PROTO = 1 BCP                 |

#### **BIT 7 ALL PARTIES ADDRESS**

Used in ring networks to enable all connected computers as receivers, i.e. a broadcast function.

7 APA BOP All Parties Address. If this bit is set, the receiver data path is enabled by an address field of '11111111' as well as the normal secondary station address.

IOX < DEVICE NO.> + 3

WRITE SYNC/ADDRESS REGISTER (SAR)

FORMAT:

| 15  |      |     | 8 | 7 | 6      | 5     | 4      | 3      | 4  | 2 | 1 | 0 |

|-----|------|-----|---|---|--------|-------|--------|--------|----|---|---|---|

|     | N/A  |     |   | 8 | bits S | YNCH/ | SEC. A |        | SS |   |   |   |

| BIT | NAME | MOD | E |   |        |       | FU     | INCTIC | N  |   |   |   |

| 00-07 | S/AR | BOP . | SYNC/ADDRESS Register. Contains the secondary station<br>address if the MPCC is a secondary station. The contents of<br>this register are compared with the first received non-FLAG<br>character to determine if the message is meant for this<br>station. |

|-------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      | вср   | SYNC character is loaded into this register by the processor.                                                                                                                                                                                              |

|       |      |       | It is used for receive and transmit bit synchronization with bit length specified by RxCL and TxCL.                                                                                                                                                        |

#### IOX < DEVICE NO.> + 4

WRITE CHARACTER LENGTH (CL)

FORMAT:

| 15    | N/A   | 8           | 76543210TRANSM.00REC.CHAR.LENGTHCHAR.LENGTH                                                                                                                                                                                                                                                                                                  |

|-------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT   | NAME  | MODE        | FUNCTION                                                                                                                                                                                                                                                                                                                                     |

| 08-10 | RxCL  | BOP/<br>BCP |                                                                                                                                                                                                                                                                                                                                              |

| 0-2   | T. CI | POP/        | 2       1       0       Char.length (bits)         0       0       8         0       0       1       1         0       1       1       2         0       1       1       3         1       0       0       4         1       0       1       5         1       1       0       6         1       1       7       Character bit length (bits) |

| 5-7   | TxCL  | BOP/<br>BCP | Character bit length specification format is identical to RxCL.                                                                                                                                                                                                                                                                              |

#### ND-12.018.01

Scanned by Jonny Oddene for Sintran Data © 2010.

## II.2.1.2 HDLC Data in the Data Phase

After the initialization (See Section II.2.1.1), the DATA module is ready to be turned into the data phase.

As mentioned in Section II.2.1 there are five registers to control the transmitted (output) channel and four to control the receive (input) channel.

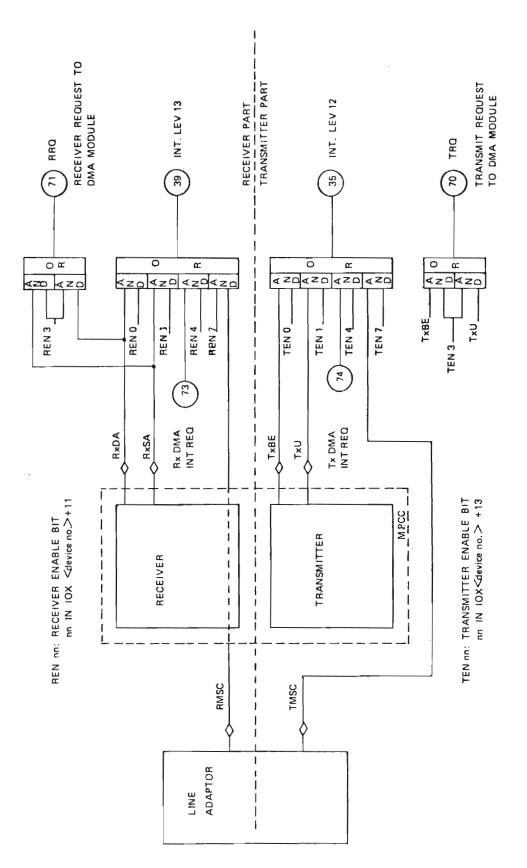

## II.2.1.2.1 Receive (Input) Channel

The control of the input channel is used to:

- write receiver control word to enable the input transfer (interrupt enable, etc.)

- read receiver status register to check the transfer quality (valid data available, error, etc.)

- read x bit bytes ( $1 \le x \le 8$ ) from input data register (see the following details)

The input channel on HDLC DATA is connected to interrupt level 13 (normally input is connected to level 12).

This is done in order to reduce possibility of receiver overrun at high transfer rates.

#### RECEIVER TRANSFER CONTROL REGISTER

Receiver control word is loaded by IOX < device no.> + 11.

Format and description of the bits are given in the programming specifications (See Appendix A5).

Special attention is drawn to control word bits 0, 1, 3, 4 and 7. Remember that HDLC DATA is designed to meet two processors.

The above mentioned bits decide what processor should be active controlling the input channel.

#### CASE 1 DMA Module Not Installed

Bit 3 and 4 in input control word should be "0" disabling the connection to the DMA module.

Bit 0, 1 and 7 should be "1" enabling changes on the input channel to be reported to NORD 10/S through interrupt on level 13.

The three following different "changes" can appear at the input channel:

- Receiver Data Available (RxDA) signifies that input data register contains a valid data byte to be read

- Receiver Status Available (RxSA) coming from MPCC indicating a change in status has occured. Further information is found by reading MPCC status register (See IOX <device no. > + 2)

- Modem Status Change (RMSC) signifies status change on the line

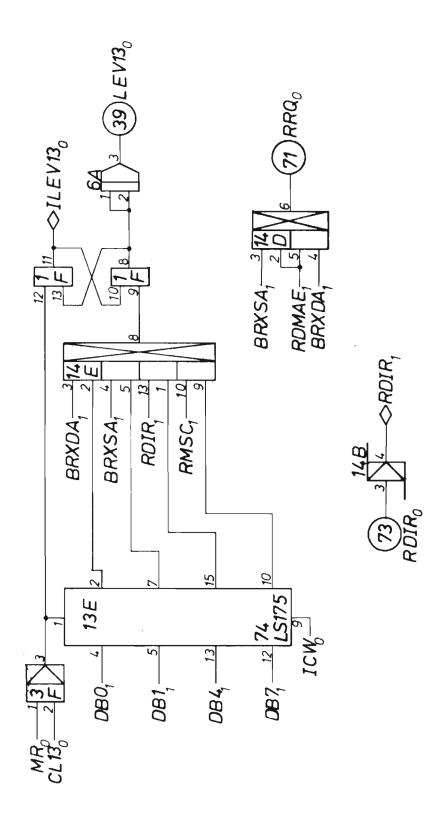

All "changes" mentioned will interrupt NORD 10/S to level 13. See Figure II.2.3 for illustration and Figure II.2.4 for details from HDLC DATA.

Figure II.2.3: HDLC DATA RECEIVER/TRANSMITTER CONTROL SIGNALS

ND-12.018.01

11-2-11

Figure II.2.4: HDLC DATA. DETAILS FROM MODULE

#### CASE 2 DMA Module Installed

Refer to Figure II.2.3. The idea is that NORD-10/S should not be disturbed by RxDA and RxSA, thus being interrupted for every received character/status. (This effect is illustrated in the following example).

This is done by disabling interrupt generation on RxDA and RxSA. That means, setting bit 0-1 in input control word to zero. Instead RxDA and RxSA is routed to the DMA processor as a Receiver Request (RRQ). That is accomplished by turning bit 3 on.

Then the DMA processor will read input status and data. The DMA module may have information to NORD 10/S (driver-software) related to the input transfer.

The DMA processor then generates a Receiver DMA Interrupt Request (RDIR) which gives interrupt on level 13 (enabled for in ICW bit 4).

Status change on the line (RMSC) is always reported directly to NORD 10/S.

#### EXAMPLE:

- Transfer RATE 19200 bits per second

- 8 bits per character

- Characters per second: 19200/8 = 2400 <sup>ch</sup>/s

That means 2400 interrupts to handle every second just to the input channel.

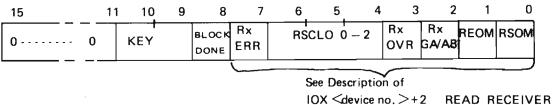

RECEIVE STATUS REGISTERS

It should be noted that HDLC contains two status registers for the input channel.

One of the registers is held internally in the MPCC. This register is accessed by IOX <device no.> + 2 and contains information about the frame formatting functions (See description below).

The other status register (Receiver Transfer Status) holds information about line status, feedback from the control register and single line status from the MPCC. This register is accessed by IOX <device no.> + 10 and is described in the programming specifications (See Appendix A5).

IOX < DEVICE NO.> + 2

READ RECEIVER STATUS - RxSR (FRAME INFORMATION)

This register is dynamically set and located internally in the MPCC. A change in the register will activate RxSA which is reset when the status is read.

The format of the register and description of the bits is given below.

FORMAT:

| 15  | 8 | 7    | 6        | 5             | 4   | 3    | 2   | 1    | 0    |

|-----|---|------|----------|---------------|-----|------|-----|------|------|

| N/A |   | RERR | RSC<br>C | LO – 2<br>B A | N N | ROUF | RAB | REOM | RSOM |

| Bit                                                               | Name     | Mode        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                                 | RSOM     | вор         | Receiver Start of Message = 1 when a FLAG followed by a non-FLAG has been received and the latter character matches the secondary station address if SAM = 1.<br>RxA will be asserted when RSOM = 1. RSOM resets itself after one character time and has no effect on RxSA.                                                                                                                                                                                                           |

| 1                                                                 | REOM     | ВОР         | Receiver End of Message = 1 when the closing FLAG is detected and the last data character is loaded into $RxDB$ or when an ABORT/GA character is received. REOM is cleared on reading RSR (Receive Status Register) reset operation, or dropping of $RxE$ .                                                                                                                                                                                                                           |

| 2                                                                 | RAB/G/   | А ВОР       | Received ABORT or GA character = 1 when the receiver<br>senses an ABORT character if $SS/GA = 0$ or a GA character<br>if $SS/GA = 1$ . RAB/GA is cleared on reading RxSR<br>operation or dropping of RxE. A received ABORT inhibits<br>RxDA.                                                                                                                                                                                                                                          |

| 3                                                                 | ROR      | BOP/<br>BCP | Receiver Overrun = 1 indicates the processor has not read<br>the last character in the RxDR (Receiver Data Register) within<br>one character time. Subsequent characters will be lost. ROR<br>is cleared on reading RSR, reset operation, or dropping or<br>RxE (receiver enable).                                                                                                                                                                                                    |

| 4-6                                                               | ABC      | BOP         | Assembled Bit Count. Specifies the number of bits in the last received data character of a message and should be examined by the processor when REOM = 1 (RxDA and RxSA asserted). ABC = 0 indicates the message was terminated (by a FLAG or GA) on a character boundary as specified by WCLR (write character length register bit 0-2). Otherwise ABC = number of bits in the last data character. ABC is cleared when RDSR <sub>h</sub> is read, reset operation, or dropping RxE. |

| 7                                                                 | RERR     |             | Receiver Error indicator should be examined by the processor<br>when REOM = 1 in BOP, or when the processor determines<br>the last data character of the message in BCP with CRC or<br>when RxSA is set in BCP with VRC.                                                                                                                                                                                                                                                              |

|                                                                   |          | BOP         | CRC-CCITT preset to 1's should be specified by $PCSAR_{8-10}$ :<br>RERR = 1 indicates FCS error (CRC $\neq$ FOB8)<br>RERR = 0 indicates FCS received correctly (CRC = FOB8)                                                                                                                                                                                                                                                                                                           |

|                                                                   |          | BCP         | CRC-16 preset 0's on 8-bit data characters specified by<br>PCSAR <sub>8-10</sub> :<br>RERR = 1 indicates CRC-16 received correctly (CRC-0)<br>RERR = 0 indicates CRC-16 error (CRC $\neq$ 0)<br>VRC specified by PCSAR <sub>8-10</sub> :<br>RERR = 1 indicates VRC error<br>RERR = 0 indicates VRC is correct                                                                                                                                                                         |

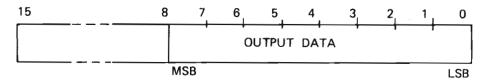

| 10X <i< td=""><td>DEVICE N</td><td>IO.&gt; + 0</td><td></td></i<> | DEVICE N | IO.> + 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| READ                                                              | RECEIVE  | R DATA      | REGISTER (RxDR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FORM                                                              | AT:      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                   |          |             | 3 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                   | N/A      |             | RECEIVED DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                   |          |             | MSB LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                   |          |             | ND-12.018.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Scanned by Jonny Oddene for Sintran Data © 2010

# II.2.1.2.2 Transmit (Output) Channel

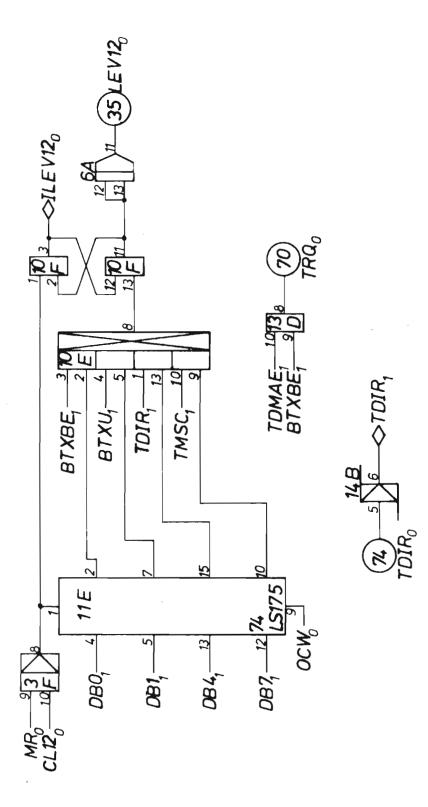

The control of the output channel is to:

- write x bits bytes (1≤X≤8) to output data register

- load transmitter control registers to control the frame formatting functions (MPCC) and activate the output transfer

- read transmitter status registers to check end of transfer and error indicators (transmitter underrun)

Details follows.

The output channel on HDLC DATA is connected to interrupt level 12 (normally output is connected to level 10). This is done to reduce the possibility of transmitter underrun at high transfer rates.

TRANSMITTER DATA REGISTER (TxDR)

IOX < DEVICE NO.> + 5

This register is held internally in the transmitter part of the MPCC and loaded by IOX < device no. > + 5.

#### FORMAT:

#### TRANSMITTER CONTROL REGISTERS

There are two registers to control the transmit channel. One of the registers is loaded directly into the MPCC to control the frame formatting functions (See below).

The other control register (Transmitter Transfer Control Register - IOX <device no.> + 13) is used on the module and serves the same function for the output channel as the receiver control register for the input channel.

That is, to connect or disconnect NORD 10/S CPU or the DMA processor to the output channel of the DATA module.

The format and bit definitions are given in the programming specifications.

For a better understanding, refer to Figure II.2.3 and Figure II.2.5 for details from HDLC DATA.

Figure II.2.5: HDLC Data, Details from Module

11-2-17

#### IOX < DEVICE NO.> + 7.

# WRITE TRANSMITTER CONTROL REGISTER (TxCW)

In this register the frame formatting function on output data is controlled. By loading the MPCC with one of the four least significant bits set to one in this register, either an opening flag (TSOM), closing flag (TEOM), go-ahead, or abort character automatically will be transmitted on the line (See details below).

FORMAT:

| 15  | 8 | 7 | 6 | 5 | 4 | 3        | 2        | 1    | 0    |  |

|-----|---|---|---|---|---|----------|----------|------|------|--|

| N/A |   | 0 | 0 | 0 | 0 | Tx<br>GA | Tx<br>AB | TEOM | TSOM |  |

| Bit | Name  | Mode       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | TSOM  | BOP<br>BCP | Transmitter Start of Message. Set by the processor to initiate message transmission provided $TxE = 1$ .<br>TSOM = 1 generates FLAGs. When TSOM = 0 transmission is from TxDB and FCS generation begins. FCS, as specified by PCR <sub>0-2</sub> , should be CRC-CCITT preset to 1's.<br>TSOM = 1 generates SYNCs from PCSAR <sub>L</sub> or transmits from TxDB for IDLE = 0 or 1 respectively. When TSOM = 0 transmission is from TxDB and CRC generation (if specified) begins.                                                                                                                                                                                                                    |

| 1   | TEOM  | BOP        | Transmit End of Message. Used to terminate a transmitted message when CRC error checking is used.<br>TEOM = 1 causes the FCS and the closing FLAG to be transmitted following the transmission of the data character in TxSR. FLAGs are transmitted until TEOM = 0. ABORT or GA are transmitted if TABORT or TGA are set when TEOM = 1.<br>TEOM = 1 causes CRC-16 to be transmitted (if selected) followed by SYNCs from SAR <sub>L</sub> or TxDB (IDLE = 0 or 1).<br>Clearing TEOM prior to the end of CRC-16 transmission (when TxBE = 1) causes TxSO to be marked following the CRC-16. TxE must be dropped before a new message can be initiated. If CRC is not selected, TEOM should not be set. |

| 3   | TABOR | Т ВОР      | Transmitter Abort = 1 will cause ABORT or FLAG to be sent (IDLE = 0 or 1) after the current character is transmitted. (ABORT = $1111111$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | TGA   | ВОР        | Transmit Go Ahead (GA) instead of FLAG when TEOM = 1.<br>This facilitates repeater termination in loop mode.<br>(GA = 01111111)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Bit 5-7: Not Used.

11-2-18

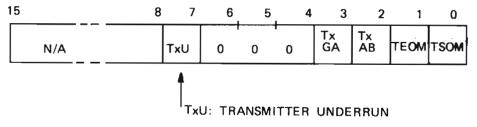

#### TRANSMITTER STATUS REGISTERS (TxSR)

Feedback from the output channel is carried through two status-registers.

One of the registers is held internally in the MPCC and reached by:

IOX < device no. > + 6.

This register holds the copy of transmitter control register (IOX <device no.> + 7) except from bit 7 which signifies transmitter underrun. Transmitter underrun TxU will generate interrupt if enabled for.

The other status register for the output channel contains information about line status and enabling done in output control register. The register (RECEIVER TRANSFER STATUS) is accessed by (IOX < device no.> + 12).

The format and bit definitions are given in the programming specifications.

Scanned by Jonny Oddene for Sintran Data © 2010

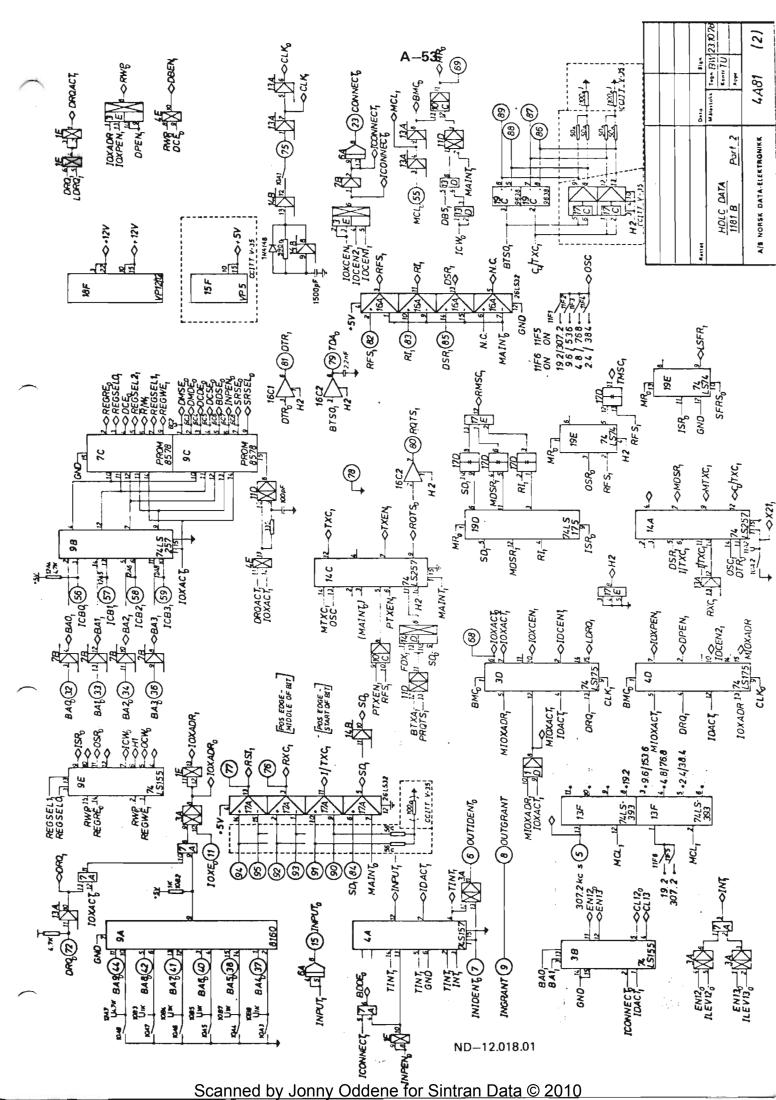

# II.3 HDLC DMA CONTROL

# II.3.1 INTRODUCTION

In this chapter we will look at how the DMA module functions together with the DATA module and NORD 10/S.

We assume that the DATA module and DMA module are enabled to work together (See input/output transfer control words).

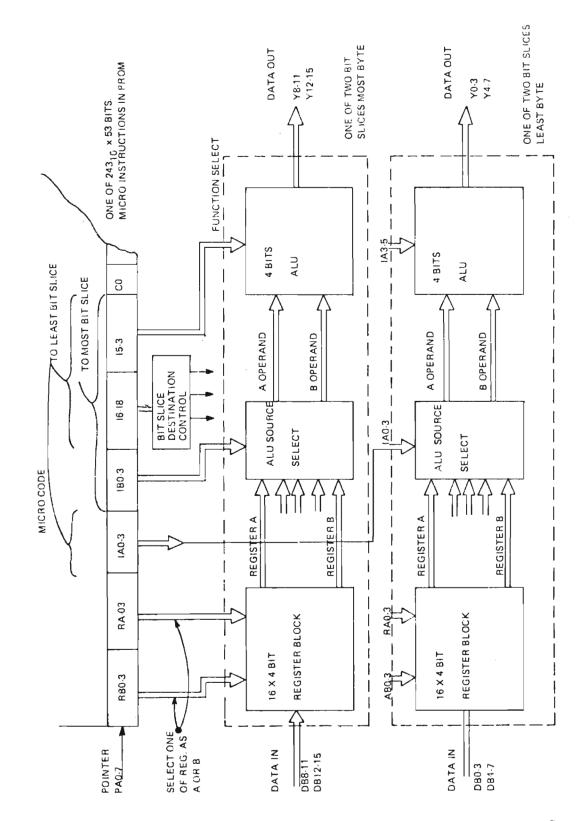

The DMA control is controlled by a microprocessor located on the module. The main functions of the processor are to:

ON INPUT

- read characters from HDLC DATA, group them into 16 bits words and place them in computer memory through Direct Memory Access (DMA)

- take care of status change in input channel

ON OUTPUT

- "DMA read" 16 bits words in computer memory, split them up into bytes transferred to output data register on the DATA module

- take care of status change in output channel

To do this the DMA processor has all IOX-instructions operating on the DATA module implemented in its microprogram.

NORD 10/S and the DMA processor communicates through a common memory area (the list structure).

NORD 10/S controls the DMA processor by means of commands given in IOXinstructions. The manner in which this is accomplished will be described in the following sections.

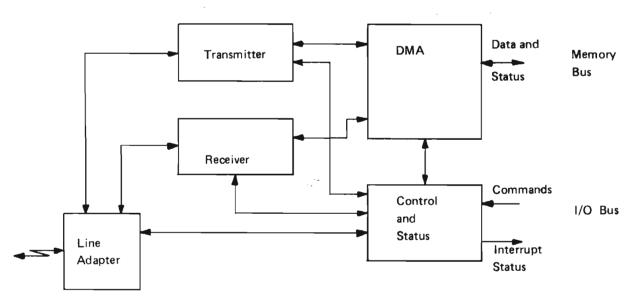

Figure II.3.1: BLOCK DIAGRAM OVER HDLC INTERFACE (DMA) ND-12.018.01

Scanned by Jonny Oddene for Sintran Data © 2010

# **II.3.2** CONTROL OF THE DMA PROCESSOR (THE COMMANDS)

Driver software controls the HDLC INTERFACE by means of 8 different commands given in IOX-instructions. All commands (with the exception of DEVICE CLEAR) need an 18 bits physical memory address due to reasons explained in the following sections.

The 16 least significant bits of the address are transferred to the interface by IOX <device no.> + 15.

The most significant address bits (Bank bits) are given in IOX < device no.> + 17.

In the format of IOX < device no.> + 17, three bits are left to specify command no. (See format).

FORMAT:

| 15 | 11 | 10 | 9    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | . 1,         | 0           | 1 |

|----|----|----|------|---|---|---|---|---|---|---|--------------|-------------|---|

| 0  | 0  |    | MAND |   | Ö | 0 | 0 | 0 | 0 | 0 | BANK<br>BITS |             |   |

|    |    |    |      |   |   |   |   |   |   |   | <u> </u>     | $ \supset $ |   |

#### IOX < DEVICE NO.> + 17

The commands may be divided up into the three following groups:

| a) | INITIALIZATION<br>DEVICE CLEAR<br>INITIALIZE                                    | (Ŏ)<br>(Ť)        | 000040<br>00040B           |

|----|---------------------------------------------------------------------------------|-------------------|----------------------------|

| b) | DATA TRANSFER<br>— RECEIVER START<br>— RECEIVER CONTINUE<br>— TRANSMITTER STÄRT | (2)<br>(3)<br>(4) | 00100B<br>00140B<br>00200B |

| c) | MAINTENANCE<br>— DUMP DATA MODULE<br>— DUMP REGISTERS<br>— LOAD REGISTERS       | (5)<br>(6)<br>(7) | 00240B<br>00300B<br>00340B |

#### 11.3.2.1 Initialization

#### DEVICE CLEAR (Command 0)

Before operating HDLC INTERFACE (DMA), a DEVICE CLEAR should be performed to ensure safe operation.

Recommended program for Device Clear is:

| SAA0                | % A reg. = 0                      |

|---------------------|-----------------------------------|

| IOX GP + 11 (octal) | % Write Receiver Transfer Control |

| BSET ONE 50 DA      | % A reg. = 40 (octal)             |

| IOX GP + 11 (octal) | % Device Clear to Data Module     |

| IOX GP + 17 (octal) | % Device Clear to DMA Module      |

The Device Clear sequence as described above will stop all data transfers to and from the interface, and it can be used anytime. Device Clear will clear all interrupts from the interface, and a dialed up modem connection will be broken.

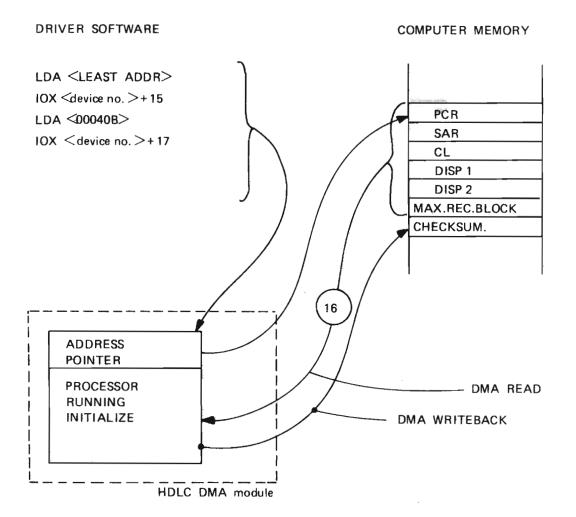

#### INITIALIZE (Command 1)

The command INITIALIZE should be used after a Device Clear.

The command will initialize the DATA module (See Section II.2.1.1) and load the DMA module with necessary parameters related to the DMA structure (see Section II.3.3).

To obtain the necessary information to perform the initialization; the command requires 7 locations in memory (parameter buffer).

These locations should be set by driver software prior to execution of the command.

The contents of the parameter buffer are:

- Parameter Control Register

- 2 Sync/Address Register

- 3 Character Length

- 4 Displacement 1

- 5 Displacement 2

- 6 Max.Receiver Block Length

- 7 Checksum

The contents of the three first locations are written into the DATA module. The bit mapping of locations is described in Section II.2.1.1.

Displacement 1 is the number of free bytes reserved at the beginning of each buffer containing the start of a message (Frame). *Displacement 2* is the number of free bytes reserved at the beginning of each buffer which do not contain the start of a message (Frame). Max. Receiver Block Length is the total number of bytes in a receiver buffer, including displacement. Long frames may be divided into blocks and stored in two or more buffers.

The use of these parameters will be illustrated in the next section, i.e. data transfer.

The checksum is set to 0 by driver software and set to 102164 by the DMA processor when INITIALIZE is finished. The interface should not be used in DMA mode if this checksum is wrong.

ND-12.018.01

(IOX < device no.> + 1) (IOX < device no.> + 3) ್ರಾ

(1OX < device no.> + 4)

Scanned by Jonny Oddene for Sintran Data © 2010

When started the DMA processor with Direct Memory Access will read the parameter buffer. To accomplish this an address pointer to the parameter buffer is needed. The address is given in the start INITIALIZE sequence which consists of the following:

LDA <least address>

% write DMA address

IOX < device no.> + 15

Write least address to HDLC INTERFACE

– LDA 00040B

% write DMA command register

IOX <device no.> + 17

Write most address and start INITIALIZE

Refer to Figure II.3.2 for illustration.

### II.3.2.2 Data Transfer

After initialization (See Section II.3.2.1) the commands:

RECEIVER START RECEIVER CONTINUE TRANSMITTER START

may be used.

Under this label only a description of how to use the command will be given. To understand how they operate, the reader is advised to study Section II.3.3 (HDLC DMA STRUCTURE).

RECEIVER START (Command 2)

The RECEIVER START command will as the name suggests, start the microprogrammed receiver on HDLC INTERFACE.

Three IOX-instructions are used to activate RECEIVER START.

| LDA <least address=""><br/>IOX <device no.=""> + 15<br/>LDA 00100B<br/>IOX <device no.=""> + 17</device></device></least> | Write 18 bits DMA<br>address to interface<br>and start Receiver                                 |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| LDA (3334<br>IOX <device no.=""> + 11</device>                                                                            | Enable receive channel<br>to DMA module. (See Appendix A5<br>IOX <device no.=""> + 11)</device> |

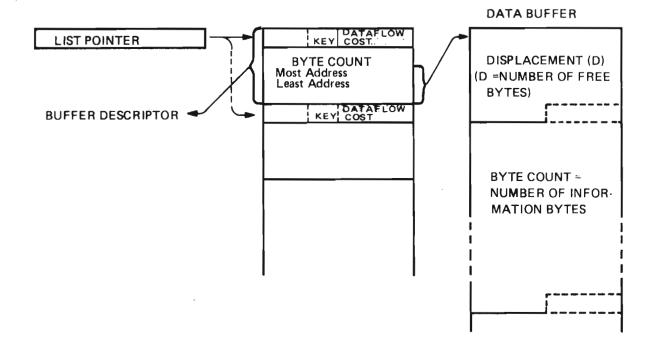

The address written to the interface in a Receiver Start sequence is denoted a "List Pointer". This address is the first address of a list containing "Buffer Descriptors" (See HDLC DMA Structure). This command also selects Displacement 1 for the first buffer, and should therefore be used the first time the receiver is started after a power up or receiver disable.

The receiver should normally run. A Receiver Request from the DATA module will then automatically be handled.

RECEIVER CONTINUE (Command 3)

This command is used to write a new List Pointer to an enabled and working interface. It should only be used as a response to a "List Empty" interrupt.

TRANSMITTER START (Command 4)

This command is always used to start transmission of data. As for RECEIVER START, an address is written to the interface when the transmitter is started. To enable the transfer, the Transmitter Control register (IOX <device no.> +13) has to be loaded.

#### 11,3.2.3 MAINTENANCE

5.

#### DUMP DATA MODULE (Command 5)

This command is mainly for maintenance purpose. It requires 5 locations in memory, where the contents of the following registers are stored:

- 1. Parameter Control Register (8 least sign. bits)

- Sync/Address Register 2.

- 3. Character Length 4. **Receiver Status Register**

(8 least sign. bits) (8 least sign. bits) (8 least sign. bits, not accumulated)

(8 least sign. bits, not accumulated)

The contents of the registers in the Multi Protocol Communication Controller (MPCC) are transferred to memory. The Receiver Status Register is also OR-ed into the Receiver Dataflow Status Register to prevent loss of information.

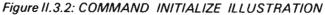

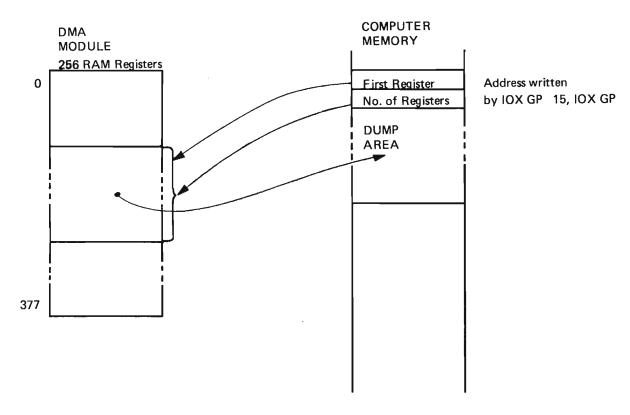

#### DUMP REGISTER (Command 6)

Transmitter Status Register

This command can be used to dump the contents of any number of the 256 random access memory registers in the DMA module. Required space in memory is 2 locations plus one location for each register to be dumped. The contents of the two locations are:

- 1. First Register Address

- 2. Number of Registers

If both values are zero, the contents of the 16 registers in the Bit Slice are written into memory.

The meaning of the different values is illustrated by the figure below.

ADDRESS WRITTEN BY IOX GP+15, IOX GP+17

#### LOAD REGISTER (Command 7)

This command can be used to load any number of the 256 random access memory registers in the DMA module. Required space in memory is 2 locations plus one location for each register to be loaded. The contents of the two locations are:

- 1. First register address

- 2. Number of Registers

The Load Register command is simular to Dump Register, except that data is moved in the opposite direction. It is not possible to load the registers in the Bit Slice by this command.

The commands, how to activate them and use them in some simple debugging programs are given in Appendix A5.

# II.3.3 HDLC DMA STRUCTURE

The DMA structure is organized around lists which contain the necessary control and status information to connect "driver" software and DMA processor together.

The lists which reside in the computer memory could be accessed directly from driver software and through DMA requests to/ from HDLC interface.

The receiver and the transmitter works from separate lists, with the same structure and format. The information exchange between driver software and DMA processor through the list structure provides dynamic allocation and linking of data buffers.

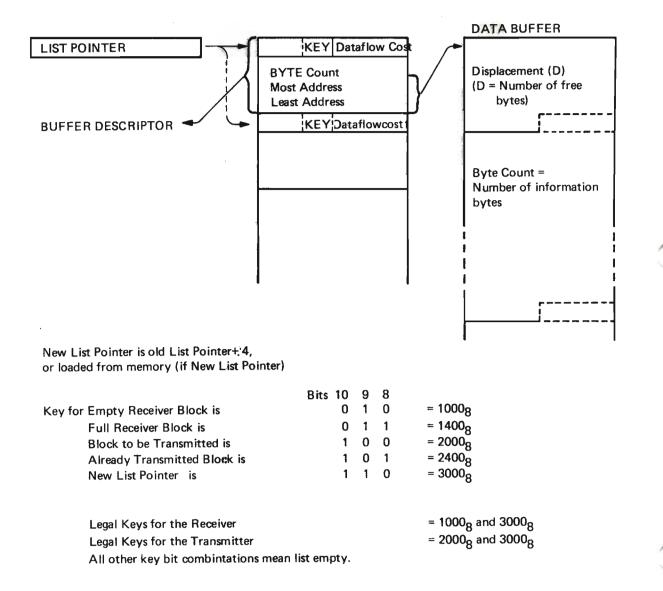

# II.3.3.1 The List Structure

The list contains a number of entries of four words each. Each list entry describes a data block. In the receiver lists, each entry describes a receive data buffer where the received data is to be stored.

In the transmitter list, each entry describes a block of data that is to be transmitted.

The four words of each entry contain the following information:

| WORD 1 E | Block status and key |

|----------|----------------------|

|----------|----------------------|

- WORD 2 Amount of information in the data block (Byte Count)

- WORD 3–4 18 bits physical memory address of data block

More detailed description is given below.

# II.3.3.1.1 Receiver List

In this section the operation of the receiver list is described.

After proper initialization (See Section II.3.2.1), the DMA processor is given a list pointer and the "RECEIVER START" command.

The liste pointer points to one of the entries in the receiver list (See Figure II.3.4).

#### Figure II.3.4: LIST STRUCTURE

.: . .

The DMA processor will now generate a DMA request using the list pointer as address and fetch the first entry from the list beginning with the status word.

11-3-9

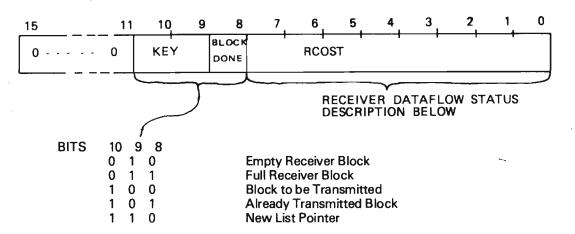

#### FORMAT OF THE STATUS WORD

The status word should be all zero except for the key.

The BLOCK DONE bit signifies used block. That is, to prevent overwriting on input or duplicated transmission on output.

Legal keys for the receiver are 1000<sub>8</sub> (Bit 9 set) or 3000<sub>8</sub> (Bit 9 and 10 set).

#### CASE 1. Key is 1000<sub>8</sub>

The key is legal saying empty receiver block. The DMA processor will now read the block address (word 3&4), add Displacement 1 and incoming data will be stored in the block.

When the block is filled (MAX.RECEIVER BLOCK) or the interface recognizes "frame end" (REOM), the DMA processor updates the list entry.

Updating the list entry includes updating the status word and writing the number of bytes received into the byte count.

#### Updating Status Word.

Updating the status word is to change the key and update RCOST.

The key is changed by setting the BLOCK DONE bit signifying Full Receiver Block.

Updating RCOST, let us first see what RCOST contains.

e no. >+2 READ RECEIVI STATUS

RCOST is identical to Receiver Status Register in the MPCC.

Suppose both bit 0 and 1 are set, that means the status word is updated to  $1403_8$ . Then the list entry describes a Full Receiver Block which contains a whole frame because both RSOM and REOM are received within the block.

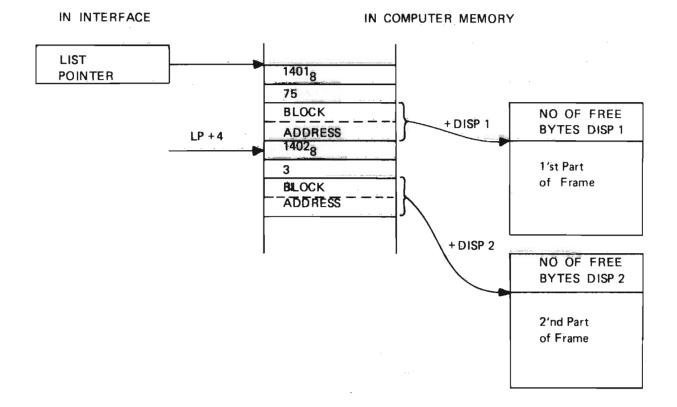

If only bit 0 is set (1401<sub>8</sub> in status word) the list entry describes a full receiver block which only contains the first part of a frame. That means that "MAX. RECEIVER BLOCK" was recognized before frame end (REOM). In other words, the frame contains more information than the receive block could store. In this case the DMA processor automatically will increment its list pointer by four and read next list entry describing next data buffer.

Suppose now that the new data block could store the last part of the frame. Than the status word of this list entry will be updated to 1402<sub>8</sub> signifying full receive block and only closing flag received. This block change is accomplished fast enough to maintain continuous handling of incoming data. It is assumed possible to give BLOCK END interrupt (See Receive Transfer Control Register).

That means, when "driver" software should take care of the incoming information it looks at the status word of the list entries.

If status is  $1403_8$ , it knows there are no errors and a whole frame of valid data is in the data block.

If status is  $1401_8$ , it knows that the block contains the first part of a frame and the next list entry with status  $1402_8$  contains the last part.

This is illustrated in the receiver list illustrations (See Figures II.3.5, II.3.6, and II.3.7).

CASE 2. KEY is 3000<sub>8</sub>

The key is legal, however it does not define a data block. Instead the list entry in word 3 and 4 contains the address to a new list.

That means, word 3 and 4 are taken as a new list pointer and the receive procedure continues as in Case 1.

NOTE:

If this list change occurs during input data, it takes too much time to maintain continuously input handling. Therefore, this situation will give List End interrupt (See Receiver Transfer Control/Status registers).

## RECEIVER LIST ILLUSTRATIONS.

Example: Frame Size.

## LIST STRUCTURE

IN INTERFACE IN COMPUTER MEMORY

LIST

DATA BLOCK

POINTER

14038

100

BLOCK

ADDRESS

NØ OF FREE

BYTES DISP

1

Figure 3.5: CASE 1 ILLUSTRATION

### Case 1. RECEIVER BLOCK SIZE: 75 bytes

### LIST STRUCTURE

Figure 3.6: CASE 1 ILLUSTRATION

NOTE:

If a frame is stored in more than two data blocks "*middle*" blocks are marked by "not start of frame" and "not end of frame" (i.e.  $1400_8$ ).

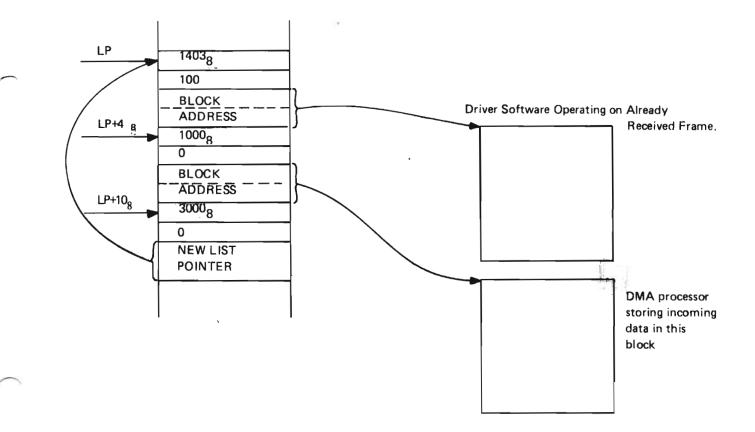

The data stored in a receiver block is now "taken care of" by driver software which also resets the list entry of the block.

The resetting is to change the status word to "Empty Receiver Block", i.e. 1000<sub>8</sub> or 3000<sub>8</sub>.

Typical use of data blocks and list entries is illustrated below.

Figure II.3.7: TYPICAL LIST OPERATION

This looping in receiver list requires that driver software is fast enough to reset the list entries. If the DMA processor reaches the NEW LIST POINTER and than Full Receiver Block, a LIST EMPTY interrupt is generated. (See Receiver Transfer Status Register).

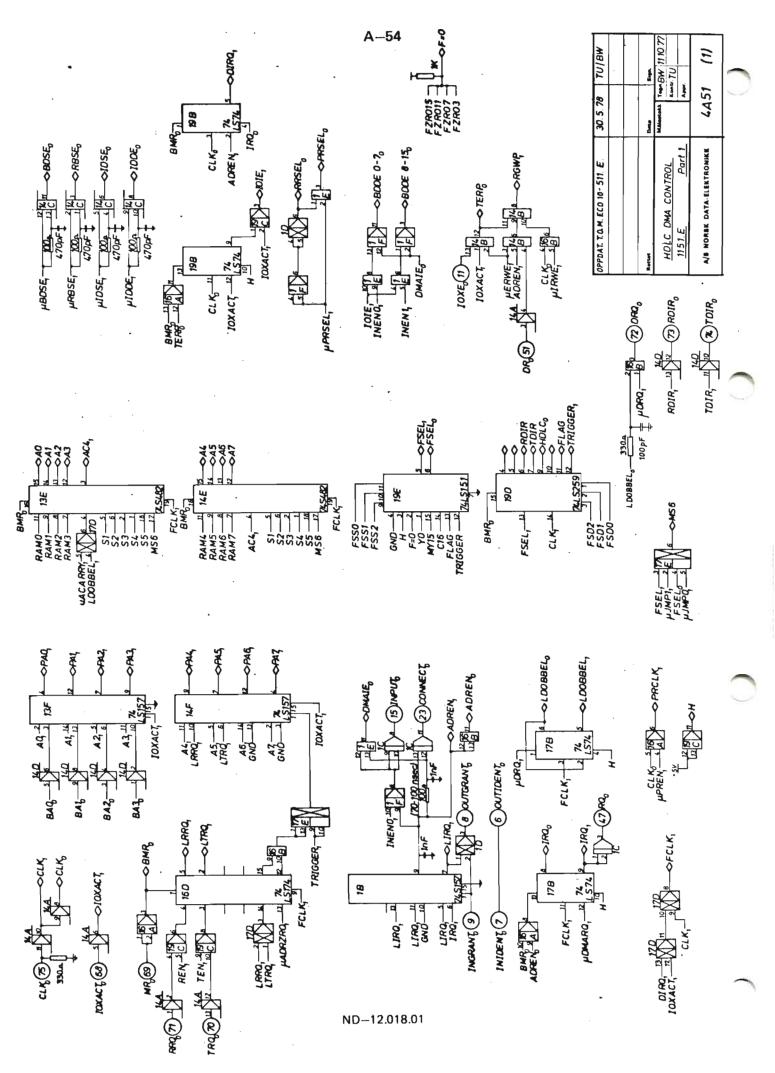

# II.3.3.1.2 Transmitter List

The transmitter list is identical in structure to the receive list.

After initialization, the DMA processor is given a list pointer and the "TRANSMITTER START" command. The DMA processor will than process the transmitter list entries as described in Section II.3.3.1.1.

Note the following differences:

The transmitter list is updated by driver software and describes blocks of data to be transmitted.

The DMA processor outputs data and sets the Block Done bit in the list entry signifying Already transmitted block.

As for the receiver list there are special cases also for the tramsmitter list.

The key could be either  $2000_8$  or  $3000_8$ . This situation is treated identically as for the receiver list and will not be discussed again.

Data belonging to one frame could be placed in one, two or more data blocks. The case is set by driver software in the status word of the list entry.

FORMAT OF THE STATUS WORD

| <br>10                     | 98            | 7 | 6 | 5             | 4 | 3        | 2        | ! 1  | 0    |                         |

|----------------------------|---------------|---|---|---------------|---|----------|----------|------|------|-------------------------|

| KEY                        | BLOCK<br>DONE |   |   | OF BIT        | - | Tx<br>GA | Tx<br>AB | TEOM | тѕом |                         |

| SEE EARLIER<br>DESCRIPTION |               |   |   | DMA<br>SOR WI |   |          |          | SOFT |      | VER<br>PRIOR<br>MISSION |

11-3-15

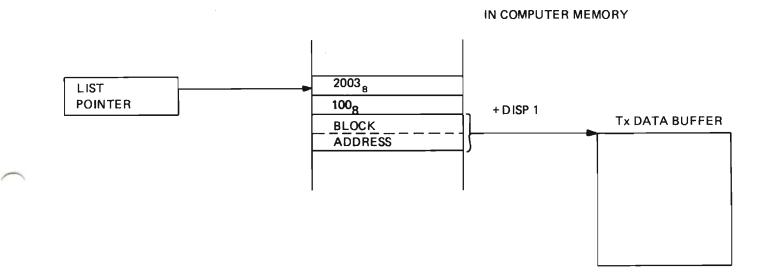

### CASE 1. A Hole Frame In One Block

Suppose the frame contains 100 bytes. Then the list entry set by driver software will be as shown below.

The DMA processor will read the status word of the list entry. The status word contains legal key (Bit 10 set). Both TEOM and TSOM are set to 1.

That means for the DMA processor:

- first transmit TSOM (opening flag)

- when 100<sub>8</sub> bytes are transmitted, send TEOM (closing flag)

- update the list entry by setting the Block Done bit (in special cases also one of the bits 2-7)

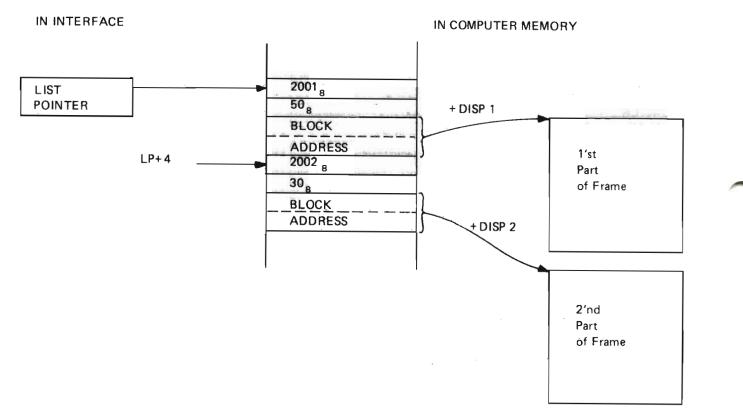

# CASE 2. A Hole Frame In Two Blocks

The list entries will now be as indicated below.

The first list entry, which contains the first part of the frame, contains legal key and *only* TSOM set.

The second list entry has also legal key and only TEOM set.

#### NOTE:

If a frame is held in more than two data blocks, the middle "blocks are marked by not start of frame" and "not end of frame" (i.e.  $2000_8$ ).

Use of data blocks and transmitter list is typically organized as for receiver list.

APPENDIX A

A-2

A.1

HDLC INTERFACE (DMA) ND NO. 720 DATA TO MEMORY VIA CPU MODULE NUMBERS 1141 (1181), 1151, 1932\*

Scanned by Jonny Oddene for Sintran Data © 2010

Scanned by Jonny Oddene for Sintran Data © 2010

A-4

A.2 DETAILED DESCRIPTION OF THE MULTIPROTOCOL COMMUN-ICATION CONTROLLER

.

Multi-Protocol Universal Synchronous Receiver/Transmitter

# **FEATURES**

- Selectable Protocol—Bit or Byte oriented

- □ Direct TTL Compatibility

- □ Tri-state Input/Output Bus

- Processor Compatible—8 or 16 bit

- □ High Speed Operation—2.0M Baud—typical

- □ Fully Double Buffered—Data, Status, and Control Registers

- □ Full or Half Duplex Operation—independent Transmitter and

**Receiver Clocks**

individually selectable data length for Receiver and Transmitter

□ Master Reset—resets all Data, Status, and Control Registers □ Maintenance Select—built-in self checking

#### BIT ORIENTED PROTOCOLS-SDLC, HDLC, ADCCP

- C Automatic bit stuffing and stripping

- Automatic frame character detection and generation

Valid message protection—a valid received message is protected from overrun

Residue Handling—for messages which terminate with a partial data byte, the number of valid data bits is available

### SELECTABLE OPTIONS:

- Variable Length Data—1 to 8 bit bytes

Error Checking—CRC (CRC16, CCITT-0, or CCITT-1)

- -None

- Primary or Secondary Station Address Mode

- All Parties Address—APA

- Extendable Address Field—to any number of bytes

Extendable Constant Field—to any number of bytes

- Extendable Control Field—to 2 bytes

- □ Idle Mode---idle FLAG characters or MARK the line

- □ Point to Point, Multi-drop, or Loop Configuration

# BYTE ORIENTED PROTOCOLS—BiSync, DDCMP

L) Automatic detection and generation of SYNC characters

### SELECTABLE OPTIONS:

- LI Variable Length Data—1 to 8 bit bytes

- □ Variable SYNC character—5, 6, 7, or 8 bits

- LI Error Checking—CRC (CRC16, CCITT-0, or CCITT-1) —VRC (odd/even parity)

- -None

- Strip Sync—deletion of leading SYNC characters after synchronization

□ Idle Mode—idle SYNC characters or MARK the line

# APPLICATIONS

- □ Computer to Modem Interface

- □ Modem to Computer Interface

- Terminal to Modem Interface

- □ Modem to Terminal Interface

- Peripheral to Modem Interface

- □ Modem to Peripheral Interface

- Serial Data Bus

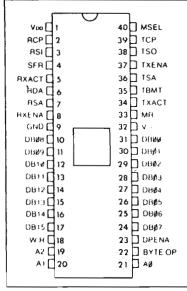

PIN CONFIGURATION

COM 5025 µPC FAMILY Preliminary Specifications

# **General Description**

The COM 5025 is a COPLAMOS\* n channel silicon gate MOS/LSI device that meets the majority of synchronous communications requirements, by interfacing parallel digital systems to synchronous serial data communication channels while requiring a minimum of controller overhead.

The COM 5025 is well suited for applications such as computer to modem interfaces, computer to computer serial links and in terminal applications. Since higher level decisions and responses are made or initiated by the controller, some degree of intelligence in each controller of the device is necessary.

Newly emerging protocols such as SDLC, HDLC, and ADCCP will be able to utilize the COM 5025 with a high degree of efficiency as zero insertion for transmission and zero deletion for reception are done automatically. These protocols will be referred to as Bit Oriented Protocols (BOP). Any differences between them will be discussed in their respective sections. Conventional synchronous protocols that are control character oriented such as BISYNC can also utilize this device. Control Character oriented protocols will be referred to as CCP protocols. Other types of protocols that operate on a byte or character count basis can also utilize the COM 5025 with a high degree of efficiency in most cases. These protocols, such as DDCMP will also be referred to as CCP protocols.

The COM 5025 is designed to operate in a synchronous communications system where some external source is expected to provide the necessary received serial data, and all clock signals properly synchronized according to EIA standard RS334. The external controller of the chip will provide the necessary control signals, intelligence in interpreting control signals from the device and data to be transmitted in accord with RS334.

The receiver and transmitter are as symmetrical as possible without loss of efficiency. The controller of the device will be responsible for all higher level decisions and interpretation of some fields within message frames. The degree to which this occurs is dependent on the protocol being implemented. The receiver and transmitter logic operate as two totally independent sections with a minimum of common logic.

### **References:**

- 1. ANSI—American National Standards Institute X353, XS34/589 202-466-2299

- 2. CCITT—Consultative Committee for International Telephone and Telegraph X.25 202-632-1007

- 3. EIA—Electronic Industries Association TR30, RS334 202-659-2200

- 4. IBM General Information Brochure, GA27-3093 Loop Interface—OEM Information, GA27-3098 System Journal—Vol. 15, No. 1, 1976; G321-0044

# MAXIMUM GUARANTEED RATINGS\*

| Operating Temperature Range                                                                                                                                                                                                                                                 | ; |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|