# ND-110 Instruction Set

ND-06.029.1 EN

# ND-110 Instruction Set ND-06.029.1 EN

The product

The ND-110 Instruction Set Manual describes the data, address and instruction format of the ND-110 CPU (Central Processing Unit) - product number ND 110110.

The reader

This manual is intended for all personnel who require information about the ND-110 assembly language.

Assumed background

The reader is assumed to have a general knowledge of programming techniques and computers.

The manual

This manual is a reference guide to the low-level programming language of the ND-110 CPU. Each chapter can be read individually and outlines the different aspects of the low-level programming as follows:

- Chapter 1. Instruction and data format.

- Chapter 2. Memory addressing.

- Chapter 3. Alphabetic index of the instruction mnemonics described and detailed description of the instructions.

The Appendices give a glossary of terms, PLANC listings of the new SINTRAN instructions, an alphabetic list of the instruction mnemonics with their octal codes and the TRR and TRA instructions for internal registers.

Related manuals

The following manuals may be useful:

ND-110 Functional Description (ND-06.026) - a detailed description of the hardware and software features, in particular microinstructions, program levels and ND-110 enhancements.

ND-100 Reference Manual (ND-06.014) - a general outline of the ND-100 computer.

MAC Interactive Assembly and Debugging System User's Guide (ND-60.096) - information on the ND-100 instruction set and assembler disassembler operation.

| 1                                                         | INSTRUCTION AND DATA FORMAT 1     |

|-----------------------------------------------------------|-----------------------------------|

|                                                           | Data and instruction types        |

| 2                                                         | MEMORY ADDRESSING — 11            |

| 2.1                                                       | Address structure                 |

| 2.2                                                       | Addressing modes                  |

| 3                                                         | THE INSTRUCTION SET               |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6 | Instructions                      |

| 3.2                                                       | The instructions                  |

|                                                           | point)                            |

|                                                           | Jump instructions                 |

|                                                           | Argument instructions             |

|                                                           | Byte block instructions           |

|                                                           | Decimal instructions              |

|                                                           | Inter-level register instructions |

|                                                           | Input/Cutput instructions         |

| Physical memory control instructions .   |   | • | • | • | • |   | • | • | • | • | • | 130 |

|------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|-----|

| Writable control store instruction       | • |   | ٠ | • |   | • |   |   | • |   |   | 131 |

| OPCOM mode instruction                   | • |   |   | • |   |   |   |   |   |   |   | 132 |

| SINTRAN III memory transfer instructions |   |   |   |   |   |   |   |   |   |   |   | 133 |

| SINTRAN III control instructions         |   | • | ٠ |   |   |   |   |   |   |   |   | 137 |

## Table of appendices

| Appendix A: GLOSSARY                                                       | - 149         |

|----------------------------------------------------------------------------|---------------|

| Appendix B: PLANC LISTINGS OF THE NEW SINTRAN INSTRUCTIONS                 | - 153         |

| Appendix C: ALPHABETIC LIST OF INSTRUCTION MNEMONICS AND THEIR OCTAL CODES | 159           |

| Appendix D: THE TRR AND TRA INSTRUCTIONS FOR INTERNAL REGISTERS            | - 165         |

| Index                                                                      | <b>– 18</b> 1 |

## List of figures

| 1. | Byte addressing                      |  |  |  |  |   |  |  |  |  | 1  |

|----|--------------------------------------|--|--|--|--|---|--|--|--|--|----|

| 2. | Double word structure                |  |  |  |  | • |  |  |  |  | L  |

| 3. | 32-bit floating point word structure |  |  |  |  |   |  |  |  |  |    |

| 4. | 48-bit floating point word structure |  |  |  |  |   |  |  |  |  | (  |

| 5. | ASCII byte structure                 |  |  |  |  |   |  |  |  |  | 8  |

| 6. | Memory reference instruction format  |  |  |  |  |   |  |  |  |  | 1/ |

#### List of tables

|    | Examples of 32-bit floating point numbers |  |   |   |  |   |   |  |   |   |

|----|-------------------------------------------|--|---|---|--|---|---|--|---|---|

| 2. | Examples of 48-bit floating point numbers |  |   | • |  | • | • |  | • | 6 |

| 3. | BCD notation                              |  |   |   |  |   |   |  |   | 7 |

| 4. | ASCII notation                            |  | • |   |  |   |   |  |   | 8 |

| 5. | ASCII embedded notation                   |  |   |   |  |   |   |  |   | C |

# CHAPTER 1 INSTRUCTION AND DATA FORMAT

| 1 | INSTRUCTION AND DATA FORMAT |  |  |  | - |   | H |   |  |  |  |  |

|---|-----------------------------|--|--|--|---|---|---|---|--|--|--|--|

|   | Data and instruction types  |  |  |  |   |   |   |   |  |  |  |  |

|   | Decimal notation            |  |  |  |   |   |   |   |  |  |  |  |

|   | BCD - Binary Coded Decimal  |  |  |  | ٠ | ٠ |   | * |  |  |  |  |

#### CHAPTER 1 INSTRUCTION AND DATA FORMAT

The ND-110 has a 16-bit word format. The bits are numbered 0 to 15, where bit 15 is the most significant and bit 0 the least significant.

octal format

The ND-110 16-bit word is represented by a 6 digit octal code. The use of octal is related to the architecture of the ND-100 family, so instructions and registers are quoted as:

SWAP octal instruction code 144000 STS octal status register code  $000001_8^8$

binary format

Often when analysing what happens to a register or what certain parts of an instruction do, it is easier to look at the word in its binary format, where the value of a bit as 1 or 0 is an important feature, for example, in the status register, bit 7 is the carry flag (C).

#### Data and instruction types

The ND-110 instruction set handles the following data and instruction types:

- bit

- byte (8 bits)

- word (16 bits)

- double word (32 bits)

- floating point words (32 and/or 48 bit) t

- † depends upon CPU version (see page 72)

bit

Bit instructions specify operations on any bit in any of the general (A,B,D,L,P,STS,T,X) registers.

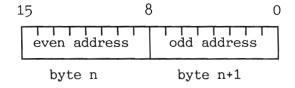

byte (8 bits)

Bytes (occasionally described in other manuals as half words) are used for byte operations. If two bytes are packed into a word for byte addressing, the even byte address points to the most significant half of the word.

Numeric range: 0 to 255

Figure 1. Byte addressing

word (16-bits) The ND-110 uses 16-bit addresses and data words. Data words can represent negative numbers, by using 2's complement notation.

Numeric range:

$$-32768_{10}$$

to  $32767_{10}$  (signed) or  $0_{10}$  to  $65535_{10}$  (unsigned)

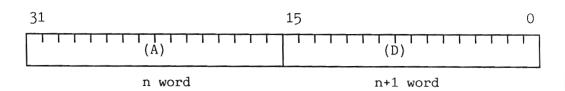

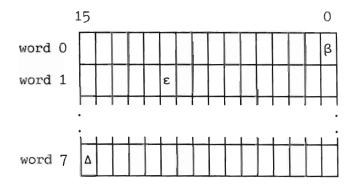

double word (32 bits)

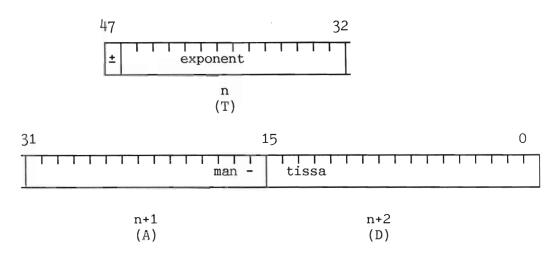

Figure 2. Double word structure

A double word is a 32-bit number occupying two consecutive memory locations (n and n+1). A double word is always referred to by the address of its most significant part; the most significant word being transferred to the A register when used and the least significant to the D register.

Numeric range:  $-2147483648_{10}$  to  $2147483647_{10}$

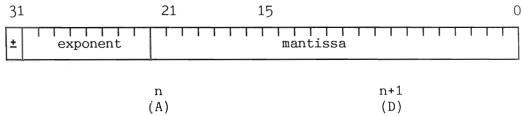

floating point words (32-bits)

The 32-bit floating word has the following format:

Figure 3. 32-bit floating point word structure

The 32-bit word occupies two consecutive 16-bit memory locations, such that address n provides the sign, exponent and 6 most significant bits of the mantissa while address n+1 provides the lower 16 bits of the mantissa. The two words are operated on in the floating bit accumulator (A and D registers).

The exponent consists of 9 bits: the most significant bit is the complement of the sign and the remaining 8 bits the exponent value (-256 to 256).

The mantissa is normalised to lie from 0.5 to approximately 1; the decimal point is one place to the left of the mantissa. The exponent is biassed with 2.

mantissa:

$0.5 \equiv m < 1$

range:

$10^{-76} < x < 10^{76}$

accuracy:

23 bits (approximately 7 decimal places)

floating zero: 0 in all 32 bits

Examples:

Table 1. Examples of 32-bit floating point numbers

| integer             | oct                                                                         | tal                                     |

|---------------------|-----------------------------------------------------------------------------|-----------------------------------------|

|                     | A word                                                                      | D word                                  |

| 0<br>+1<br>-1<br>+3 | 000000<br>040100 <sup>8</sup><br>140100 <sup>8</sup><br>040240 <sup>8</sup> | 000000<br>0000008<br>0000008<br>0000008 |

48-bit floating point

The 48-bit floating point word has the following format:

Figure 4. 48-bit floating point word structure

Here the floating point data word occupies three consecutive locations in memory. Address n holds the single bit sign and the 15-bit exponent value, address n+1 the most significant part of the mantissa and address n+2 the least significant. For operations, the three words become the A,D and T registers respectively and are defined as the floating point accumulator.

Range:  $10^{-4920} < x < 10^{4920}$

Accuracy: 32 bits (approximately 10 decimal digits)

Floating Zero: 0 in all bits

Examples:

Table 2. Examples of 48-bit floating point numbers

| integer             | T word                                    | octal<br>A word                             | D word                                  |

|---------------------|-------------------------------------------|---------------------------------------------|-----------------------------------------|

| 0<br>+1<br>-1<br>+3 | 000000<br>040001<br>140001<br>040240<br>8 | $000000 \\ 100000 \\ 100000 \\ 100000 \\ 8$ | 000000<br>0000008<br>0000008<br>0000008 |

#### Decimal notation

#### BCD - Binary Coded Decimal

Decimal digits are represented in binary-coded decimal (BCD), sometimes known as packed decimal.

Four bits are used to represent a decimal digit:

Table 3. BCD notation

| bin                                                                | ary                                                                          | nota                                                                         | tion                                                     |                                                                                 |

|--------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|

| msb                                                                | )                                                                            |                                                                              | lsb                                                      | decimal<br>equivalent                                                           |

| 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>+<br>-<br>+<br>†<br>+<br>(+) |

<sup>(+)</sup> represents unsigned, it is treated as a plus.

The maximum length of an operand is 31 decimal digits plus a sign nibble (4 bits), this occupies eight consecutive memory locations (eight 16-bit words).

<sup>†</sup> The ND-110 instruction set uses only the codes 1100 for plus and 1101 for minus.

#### ASCII coded decimal

ASCII-coded decimal notation uses eight bits to represent a decimal digit.

The format of an ASCII code decimal is:

| zone | digit |

|------|-------|

|------|-------|

Figure 5. ASCII byte structure

Table 4. ASCII notation

| AS( | CII<br>b | Co | de |   |   |   | lsb | Decimal<br>Equivalent |

|-----|----------|----|----|---|---|---|-----|-----------------------|

| 0   | 0        | 1  | 1  | 0 | 0 | 0 | 0   | 0                     |

| 0   | 0        | 1  | 1  | 0 | 0 | 0 | 1   | 1                     |

| 0   | 0        | 1  | 1  | 0 | 0 | 1 | 0   | 2                     |

| 0   | 0        | 1  | 1  | 0 | 0 | 1 | 1   | 3                     |

| 0   | 0        | 1  | 1  | 0 | 1 | 0 | 0   | 4                     |

| 0   | 0        | 1  | 1  | 0 | 1 | 0 | 1   | 5                     |

| 0   | 0        | 1  | 1  | 0 | 1 | 1 | 0   | 6                     |

| 0   | 0        | 1  | 1  | 0 | 1 | 1 | 1   | 7                     |

| 0   | 0        | 1  | 1  | 1 | 0 | 0 | 0   | 8                     |

| 0   | 0        | 1  | 1  | 1 | 0 | 0 | 1   | 9                     |

Bit 7 (msb) is the parity bit and is always zero in ASCII code.

sign representation:

The ASCII notation for sign is as follows:

+ 00101011 53<sub>8</sub> - 00101101 55<sub>8</sub> There are four ways of representing the sign in a decimal operand:

separate trailing The byte following the last significant digit contains

the sign.

sign.

embedded trailing The byte representing the least significant decimal

digit also contains the sign.

contains the sign.

embedded sign coding The embedded codes are represented by ASCII notation as

follows:

Table 5. ASCII embedded notation

| decimal operand                           | -                                                           | ive sign<br>I value                                                                                    |                                                             | ive sign<br>I value                                                                                      |

|-------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                           | octal                                                       | binary                                                                                                 | octal                                                       | binary                                                                                                   |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | 173<br>101<br>102<br>103<br>104<br>105<br>106<br>107<br>110 | 01111011<br>01000001<br>01000010<br>01000011<br>01000100<br>01000101<br>01000110<br>01000111<br>010010 | 175<br>112<br>113<br>114<br>115<br>116<br>117<br>120<br>121 | 01111101<br>01001010<br>01001011<br>01001100<br>01001101<br>01001110<br>01001111<br>01010000<br>01010001 |

| 9                                         | 111                                                         | 01001001                                                                                               | 122                                                         | 01010010                                                                                                 |

# CHAPTER 2 MEMORY ADDRESSING

| 2   | MEMORY ADDRESSING -      |  | - | Ŧ | - | 7 | - |  | - | H | - | - | - | - |  | - | 11 |

|-----|--------------------------|--|---|---|---|---|---|--|---|---|---|---|---|---|--|---|----|

| 2.1 | Address structure        |  |   |   |   |   |   |  |   |   |   |   |   |   |  |   | 14 |

|     | Execution times          |  |   |   |   |   |   |  |   |   |   |   |   |   |  |   | 15 |

|     | Memory management        |  |   |   |   |   |   |  |   |   |   |   |   |   |  |   |    |

| 2.2 | Addressing modes         |  |   |   |   |   | ě |  |   |   |   |   |   |   |  |   | 17 |

|     | Addressing mode notation |  |   |   |   |   |   |  |   |   |   |   |   |   |  |   | 17 |

|     | Addressing modes         |  |   |   |   |   |   |  |   |   |   |   |   |   |  |   | 18 |

CHAPTER 2 MEMORY ADDRESSING

ND-06.029.1 EN

The ND-110 accesses memory as 16-bit words. There are four different types of memory access.

- 1. **Instruction fetch**. The word being fetched will be interpreted as an instruction.

- 2. Operand read. The word being fetched will be used as data.

- 3. Operand write. The word being written is data.

- 4. Indirect address fetch. The word being fetched will be treated as an address for the current operation.

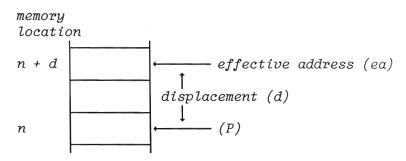

The ND-110 uses relative addressing. This means that the address is specified relative to the contents of the program counter (P register), or relative to the contents of the B and/or X registers.

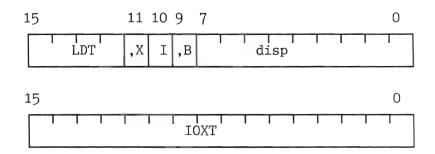

The following pages detail the various addressing modes available on the ND-110 (including byte addressing and direct physical memory addressing). Each addressing mode is given its own page and headed by its title and bit format. These pages are preceded by a general description of the instruction format and the terminology used.

#### 2.1 Address structure

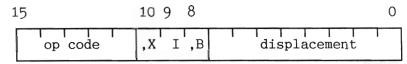

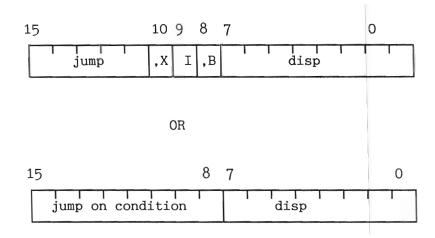

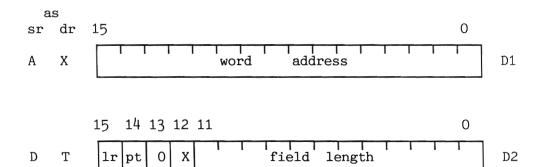

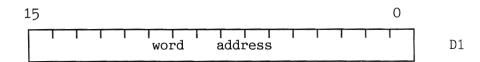

A large group of memory reference instructions share the same format:

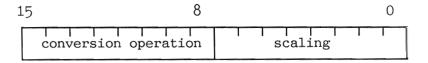

Figure 6. Memory reference instruction format

Bits 8 to 10 define the addressing mode and bits 0 to 7 the displacement. Together these two fields define the memory address.

The 8-bit displacement field is a 2's complement signed number (giving a displacement range of +127 to -128).

The five most significant bits, the op code, define the type of operation executed.

The eight possible combinations of ",X", "I" and ",B" give the following address modes:

- P relative addressing

- B relative addressing

- P indirect addressing

- B indirect addressing

- X relative addressing

- B indexed addressing

- P indirect indexed addressing

- B indirect indexed addressing

Byte addressing

This is a special type of address mode used to manipulate character strings within memory. It is described after the relative addressing modes.

Physical memory addressing

This address mode is used to address a memory location within the physical memory without using the memory management system (for memory addresses  $> 2000000_8$ ). Its description follows byte addressing.

#### Execution times

When indirect addressing is used, the execution time of a memory reference instruction increases. One extra microcycle is needed if the indirect address is found in cache; if not, the extra time is the length of a memory access.

When B relative indexed addressing (,X,B) is used the instruction execution time is increased by one microcycle. However, this does NOT apply to B indirect indexed addressing (,X I,B).

#### Memory management

Addressing modes are described in this manual in reference to their 16-bit virtual address, this is normally translated to a 24-bit physical address by the memory management system (extended mode). Older programs may use a 19-bit physical address (normal mode).

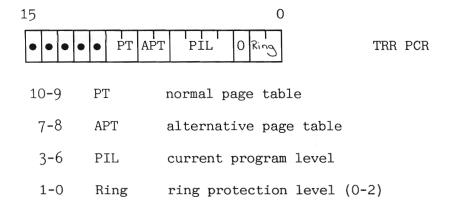

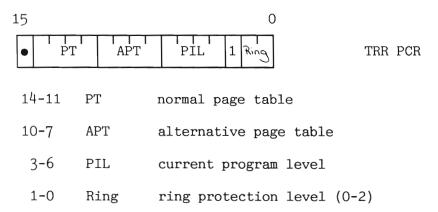

When memory management is ON, the translation of a 16-bit address to a 24-bit physical address is done with the help of the normal page table (PT) or alternate page table (APT). The rule is: P relative addressing uses PT and B relative or indexed (X) addressing use APT addressing modes.

Indirect(I) addressing results in two memory accesses. One for the indirect address and the second for the instruction operand itself. The memory management system regards these two accesses as separate operations and chooses PT or APT modes, according to the above rule, for each memory access.

#### 2.2 Addressing modes

#### Addressing mode notation

The following symbols are used in the description of the ND-110 addressing modes:

- ,X address relative to X register (post-indexed)

- I indirect address

- ,B address relative to B register (pre-indexed)

- d displacement (bits 0-7 of instruction) as a 2's complement value

- () contents of

- ea effective address

- n arbitrary address of a word in memory

- K memory-block base-address pointer

- \* current value of the program counter

- ← points to

- > loaded into

- PT normal page table

- APT alternate page table

Note: The effective address is the term given to the memory location which is finally accessed after all address modification (pre- and post- indexing) has taken place.

#### Addressing modes

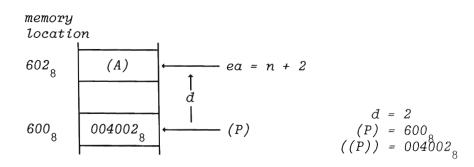

Effective address:

ea = (P) + displacement

Description:

The effective memory address is calculated by adding the value of the displacement to the contents of the P register (program counter). If memory management is being used, the normal page table (PT) will be used.

Note: d may have any value in the range -128 to 127.

Example:

STA \*2 (instruction code  $004002_8$ )

Store contents of A register in the memory location two words ahead of this instruction.

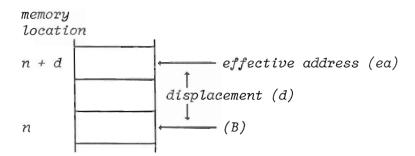

B relative addressing

,X=0

I=0 ,B=1

Effective address:

ea = (B) + displacement

Description:

The effective address is calculated by adding the value of the displacement vector to the contents of the  ${\tt B}$  register.

If memory management is ON, the alternate page table (APT) converts the effective address to a physical address.

Note: d may have any value in the range -128 to 127.

Example:

LDA -4,B (instruction code 044774,)

Load the contents of a memory location into the A register. The effective address location is the contents of the B register minus the displacement value (= 4).

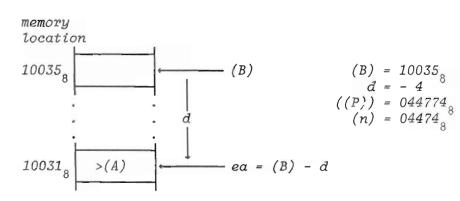

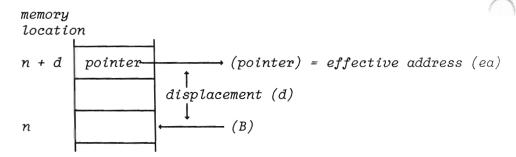

P indirect addressing ,X=0 I=1 ,B=0

Effective address:

ea = ((P) + displacement)

Description:

The contents of the P register (program counter) are added to the value of the displacement to find the indirect address (pointer). If memory management is ON, the standard page table (PT) converts the indirect address to a physical address.

The 16-bit word pointed to by the indirect address is the effective address for the operation. If memory management is ON, the alternate page table (APT) converts the effective address to a physical address.

Note: d may have any value in the range -128 to 127.

LDA I \*2 (instruction  $045002_8$ )

Load the contents of the effective address into the A register. The effective address is the contents of the memory location two words (d = 2) ahead of the current instruction.

Example:

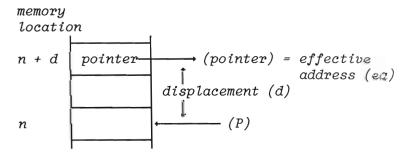

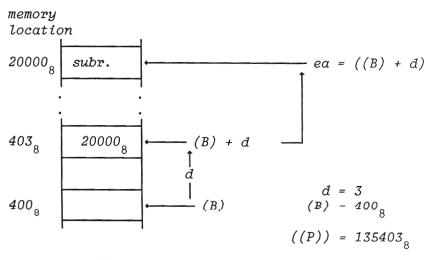

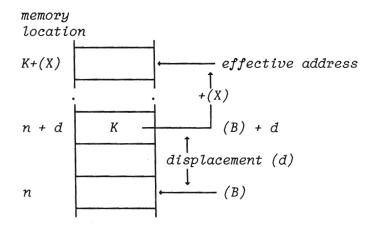

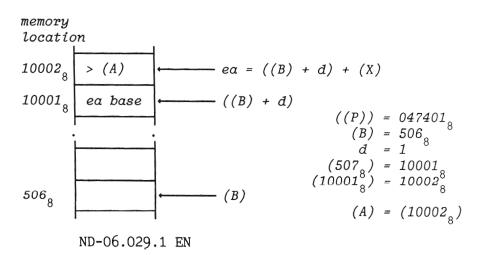

B indirect addressing

,X=0

I=1 ,B=1

Effective address:

ea = ((B) + displacement)

Description:

The contents of the B register are added to the displacement value. The resulting 16-bit value is the indirect address.

The 16-bit word fetched from this location is the effective address for the operation. If memory management is ON, the alternate page table (APT) will be used to convert both the indirect and effective addresses to physical addresses.

NOTE:

Indirect addressing adds one extra memory access to the execution time of the instruction.

Note: d may have any value in the range -128 to 127.

Example:

JPL I 3,B (octal code for instruction  $135403_8$ )

The contents of the B register plus the value of the displacement point to the memory location which contains the effective address.

The instruction saves the contents of the P register (program counter) in the L register and loads the P register with the effective address. This results in the next instruction (marked subr. in the diagram below) being fetched from the effective address.

ND-06.029.1 EN

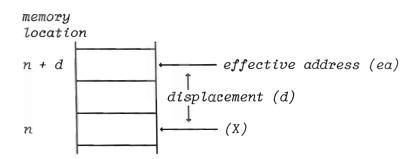

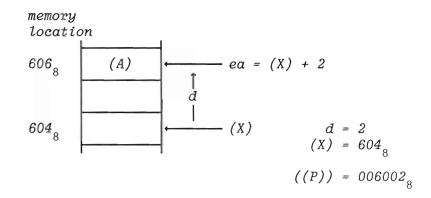

X relative addressing ,X=1 I=0

,B=0

Effective address:

ea = (X) + displacement

Description:

The effective address is calculated by adding the value of the displacement to the contents of the X register.

If memory management is being used, the alternate page table (APT) is used to convert the effective address to a physical address.

Note: d may have any value in the range -128 to 127.

Example:

STA 2,X (instruction code 006002<sub>8</sub>)

Store contents of X register in the memory location two words ahead of this instruction.

B indexed addressing

, X=1

I=0 .B=1

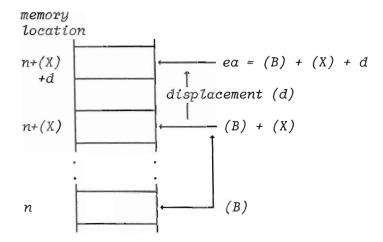

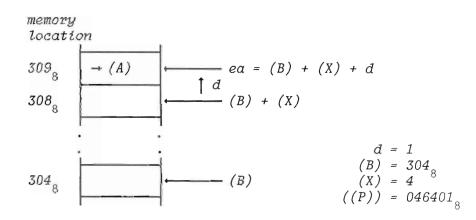

Effective address:

$$ea = (B) + (X) + displacement$$

Description:

The effective address is calculated by adding the contents of the B register to the contents of the X register, and then adding the result to the value of the displacement.

If memory management is being used, the alternate page table (APT) will be used to convert the effective address to a physical addresses.

NOTE:

This addressing mode adds one extra microcycle to the execution time of the instruction.

Note: d may have any value in the range -128 to 127.

Example:

LDA 1,B ,X (instruction code  $046401_8$ )

Load the contents of the memory location into the A register. The effective address is the contents of the B and X registers added together plus the displacement (= 1).

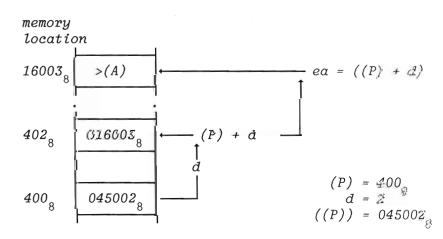

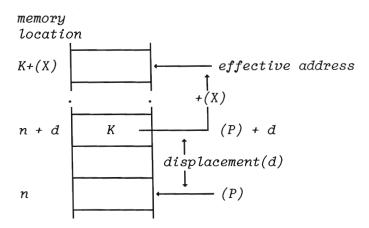

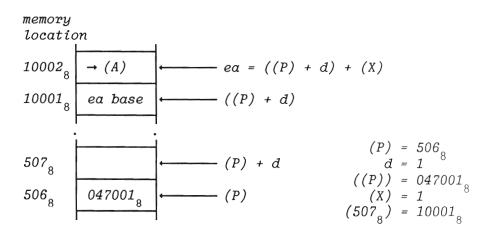

P indirect indexed addressing

I=1

,B=0

Effective address:

$$ea = ((P) + displacement) + (X)$$

Description:

The displacement value is added to the contents of the P register to determine an indirect address. The 16-bit word at this location is added to the contents of X (index) register to find the effective address. The indirect address can be used as a base pointer to a block of memory with (X) the index.

If memory management is being used, the alternate page table (APT) will be used to convert the effective address to a physical addresses.

NOTE:

Indirect addressing adds one extra memory access to the execution time of the instruction.

Note: d may have any value in the range -128 to 127.

Example:

LDA ,X I \*1 (instruction code  $047001_8$ )

The contents of the P register (program counter) are added to the value of the displacement (= 2) and the value fetched is used as the effective address. The contents of the effective address are loaded into the A register.

B indirect indexed addressing

.X=1

I=1,B=1

Effective address:

ea = ((B) + displacement) + (X)

Description:

The displacement value is added to the contents of the B register to determine an indirect address. The 16-bit word at this location is added to the contents of X (index) register to find the effective address. The indirect address can be used as a base pointer to a block of memory with (X) the index.

If memory management is being used, the alternate page table (APT) will be used to convert the effective address to a physical address.

NOTE:

Indirect addressing adds one extra memory access to the execution time of the instruction.

Note: d may have any value in the range -128 to 127.

Example:

LDA ,X I ,B \*1 (instruction code  $047401_8$ )

Load the contents of the memory location into the A register. The memory location pointed to by the contents of the B register (program counter) plus a displacement of two gives an intermediate memory location containing the base effective address of a block of data each word located by the index (X register) contents.

Byte addressing

Effective address:

$$ea = (T) + (X) \div 2$$

Description:

Byte instructions use bytes within memory, these are addressed by the T and X registers.

The T register contents point to the start of a character string in memory and the contents of the X register point to a byte within the string.

memory location

$$n+2$$

$X=4$   $X=5$   $\leftarrow$   $(ea) = effective address  $n+1$   $X=2$   $X=3$   $\leftarrow$   $(T)$$

Example:

LBYT (instruction code  $142200_8$ )

Load the byte addressed by the contents of the T and X register into the lower byte of the A register; set the higher byte to zero.

memory

| locatio           | on<br>1 1 |   | 1              |       |                                         |

|-------------------|-----------|---|----------------|-------|-----------------------------------------|

| 4602 <sub>8</sub> | е         | f | ← (ea) = (T) + | (X)/2 |                                         |

| 46018             | c         | đ |                | (T)   | = 4600 <sub>8</sub><br>= 4 <sub>8</sub> |

| 4600 <sub>8</sub> | а         | b | (T)            |       | = 377 <sub>8</sub>                      |

|                   | I         |   |                |       | $= 000377_{8}$                          |

|                   |           |   |                |       | = 142200 <sub>8</sub>                   |

|                   |           |   |                | ((-)) | 8                                       |

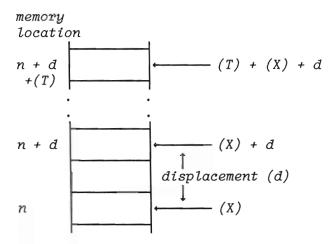

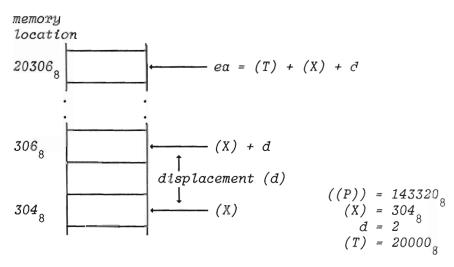

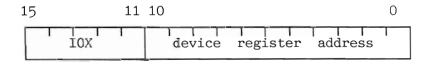

Physical memory addressing

Effective address:

ea = (T) + (X) + displacement

Description:

There are seven privileged instructions (see pages 133-136) which read/write to any physical memory location whether the memory management system is enabled or not (paging on/off). However, they will affect the page tables if the address is within page-table range.

The effective address is calculated by adding a 3-bit displacement value to the T and X register contents.

The displacement is added to the X register first. If this results in a carry, the carry is dropped and NOT added to the T register. Hence, the T register always determines which  $64~\rm K$  memory area to address.

Note: d may have any value in the range 0 to 7.

Example:

LDATX (instruction code 143320<sub>8</sub>)

## CHAPTER 3 THE INSTRUCTION SET

| 3                                                  | THE INSTRUCTION SET                                                                                                                                                                                                                                        | 29                                                                                          |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6 | Instructions Using privileged instructions How an instruction is executed How to change the microprogram Instruction timing Alphabetic index of the instruction set Instruction set notation                                                               | 31<br>31<br>32<br>32<br>33<br>35<br>37                                                      |

| 3.2                                                | The instructions                                                                                                                                                                                                                                           | 38<br>39                                                                                    |

|                                                    | point) Floating point conversion instructions Shift instructions Jump instructions Monitor instruction Skip instruction Argument instructions Bit instructions Single byte instructions Byte block instructions Word block instruction Version instruction | 95<br>97<br>98<br>108<br>112<br>113<br>115<br>117<br>121<br>124<br>128<br>130<br>131<br>132 |

#### CHAPTER 3 THE INSTRUCTION SET

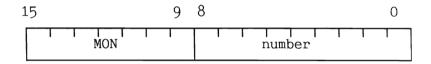

The range of instructions that can be executed by the ND-110 is the instruction set. It includes operations on data, varying from bits to triple words; BCD, floating point, arithmetical and logical operations and system-control functions.

This chapter gives a brief explanation of instruction execution and timing, followed by a detailed description of the instruction set. Addressing modes are described in the previous chapter.

Instructions are listed in alphabetical groups according to the type of operation. Each instruction mnemonic is highlighted on the relevant page edge to help you scan through the chapter for a specific instruction. Each page has a general heading to the type of operation.

The instruction set is preceded by an alphabetical index of mnemonics and a key to the notation used.

#### 3.1 Instructions

#### 3.1.1 Using privileged instructions

The instruction set can be subdivided into two instruction types:

- privileged

- user

The privileged instructions are used by the operating system and RT programs only.

Privileged instructions execute all I/O transfers, control memory management and interrupt systems, and enable inter-program level communication.

A user executes the instruction-set subset which excludes privileged instructions; the instruction MON providing the only source of user-operating system communication.

#### 3.1.2 How an instruction is executed

Each instruction in the ND-110 has a corresponding microprogram sequence (a set of micro-instructions) in the microprogram control store. The instruction code is decoded in RMIC gate array to find which microprogram is to be run. Instructions are loaded into cache memory improving execution time of repetitive instructions, as they can be fetched from the local cache each time instead of memory.

The next instruction is fetched during the last microcycle of the current instruction. This differs from the procedure followed in the ND-100 where the next instruction was prefetched during the current instruction. The ND-110 does not lose speed by fetching instructions in the last microcycle, as they are normally fetched from cache memory where they have been partly decoded.

The program counter (P register) points to the instruction address, if the instruction is fetched from memory and the memory management system (MMS) is on, the 16-bit virtual address will be converted to a 24-bit physical address and a 16-bit instruction fetched from the address. If MMS is off, the 16-bit program counter is the address of the instruction.

Detailed information on how the microprogram is decoded is described in the ND-110 Functional Description (ND-06.026).

#### 3.1.3 How to change the microprogram

The microprogram control store is writable and can be set dynamically using two instructions TRR CS and TRA CS (new to the ND-110 instruction set).

#### 3.1.4 Instruction timing

The shortest instructions are executed from cache and use 1 microcycle (compared to the 4 cycles needed in the ND-100).

## 3.1.5 Alphabetic index of the instruction set

| AAA85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | JMP78      | REMPL142 * |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|

| AAB85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | JNC80      | REPT143 *  |

| AAT85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JPC80      | REX129 *   |

| AAX85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | JPL78      | REXO53     |

| ADD65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | JXN80      | RGLOB143 * |

| ADDD101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | JXZ80      |            |

| 10 20 20 20 20 20 20 20 20 20 20 20 20 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | RINC54     |

| AND67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | LACB140 *  | RMPY55     |

| BANC87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LASB140 *  | RORA56     |

| BAND87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LBIT140 *  | RSUB57     |

| BFILL93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LBITP141 * | SAA85      |

| BLDA87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LBYT91     | SAB85      |

| BLDC87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LBYTP141   | SACB143 *  |

| BORA87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LDA60      |            |

| BORC87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | SAD75      |

| The state of the s | LDATX134 * | SASB143 *  |

| BSET87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LDBTX134 * | SAT85      |

| BSKP87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LDD60      | SAX85      |