| ND PRINTING HISTORY |      |                                     |

|---------------------|------|-------------------------------------|

| Issue               | Date | Notes                               |

| 1                   | 7/86 | Preliminary issue                   |

| 2,                  | 9/86 | Pilot issue                         |

| 3                   | 4/87 | Revised. Title now "Butterfly-110 " |

| Disclaimer       | Norsk Data A.S. assumes no responsibility for any errors or<br>omissions in this manual. The information in this manual is<br>subject to change without notice. Norsk Data A.S. assumes no<br>responsibility for the use or reliability of its software on<br>equipment that is not supplied or supported by Norsk Data<br>A.S. Norsk Data A.S. assumes no responsibility for the use<br>or reliability of its equipment using software that is not<br>supplied or supported by Norsk Data A.S. |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copyright        | Copyright $^{	extsf{G}}$ 1987 by Norsk Data A.S.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | The information in this document is protected by copyright.<br>It may not be photocopied, reproduced, or translated without<br>the prior consent of Norsk Data A.S.                                                                                                                                                                                                                                                                                                                             |

| Acknowledgements | IBM is a registered trademark of International Business<br>Machines Corporation USA.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  | MS-DOS and MS-Windows are trademarks of Microsoft Corporation USA.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  | EIS is a trademark of Ericsson Information Systems AB Sweden.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Butterfly-110 Technical Reference Manual

# ORDER INFORMATION

This manual is in loose leaf form for ease of handling and of updating. It is designed to be placed in a standard 4-ring binder, which provides greater protection and convenience of use for a manual of this size. The capacity of the binder required is 40mm.

A special Butterfly-110 ring binder, with pre-printed titles, is available for this manual.

Additional copies of this manual and its Butterfly-110 ring binder may be ordered.

Please send your order to your local ND office,

| or in Norway to | Documentation Department<br>Norsk Data A.S<br>Olaf Helsets Vei 5<br>Post Box 25<br>Bogerud<br>O621 Oslo 6 |

|-----------------|-----------------------------------------------------------------------------------------------------------|

| or in UK to     | Documentation Department                                                                                  |

or in UK to Documentation Department Norsk Data Ltd Benham Valence Newbury Berkshire RG16 8LU

quoting your name, company and address, and specifying the ND part number for this manual.

## UPDATES

Manuals can be updated in two ways:

- complete new issues

- revised pages.

New issues consist of a complete new manual which replaces the earlier issue of the manual. A new issue incorporates all the revisions since the previous issue.

Revisions consist of one or more pages which replace pages in the existing issue of the manual. Each revised page is listed on the new Printing Record which accompanies the revision pages. The previous Printing Record should be replaced by the new one.

New issues and revisions are announced in the ND Bulletin, and can be ordered through the normal ND channels.

The Reader's Comments form at the back of this manual can be used both to report errors in the manual and to give an evaluation of it. All comments are welcome, both detailed and general.

PREFACE

| THE | PRODUCT | ${\sf BUTTERFLY-110}$ is a complete system, comprising a version of the ND-110CX computer (called the ND-110PCX), fitted into the enclosure of an IBM-compatible PC-AT computer.                                                                                                                                                                                                                                                                                          |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |         | The Butterfly-110 product offers in one machine the<br>functionality of an IBM PC-AT with all its currently<br>available software running under MS-DOS, coupled with the<br>extensive range of ND NOTIS software which runs under ND's<br>SINTRAN III operating system. Information in Butterfly-110<br>is freely interchangeable between the PC and ND operating<br>systems, i.e. data created under the PC system may then be<br>used by the ND system, and vice versa. |

|     |         | A centronics parallel printer port is available as standard.<br>Options include a 4-port serial communications controller,<br>which may be used to connect ND-compatible terminals to the<br>ND-110PCX part of the workstation, making a Butterfly<br>Teamstation environment.                                                                                                                                                                                            |

| THE | READER  | <ul> <li>Technical managers and system personnel requiring a<br/>functional appreciation of the Butterfly-110 product.</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

|     |         | <ul> <li>Hardware engineers requiring a detailed description of<br/>the ND-110PCX and its microprogram.</li> </ul>                                                                                                                                                                                                                                                                                                                                                        |

|     |         | <ul> <li>Software engineers requiring detailed information about<br/>the programming changes and additions to the ND software<br/>(including the ND-PC communication system), and to the<br/>MS-DOS environment.</li> </ul>                                                                                                                                                                                                                                               |

|     |         | <ul> <li>Maintenance personnel requiring information about<br/>preventive and corrective maintenance for Butterfly-110,<br/>including diagnostic test programs and parts data.</li> </ul>                                                                                                                                                                                                                                                                                 |

| THE | MANUAL  | This manual provides technical information for the<br>Butterfly-110, cross-referencing other manuals where<br>appropriate. It includes a detailed description of the                                                                                                                                                                                                                                                                                                      |

ND-110PCX part of the system, its interface with the PC-AT,

plus maintenence and parts information.

v

| RELATED MANUALS | The other manuals in the suite of Butterfly-11 manuals are:                                                                            | 10 product                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|                 | Butterfly Teamstation Installation Guide<br>Butterfly Teamstation Supervisor Guide<br>Butterfly Teamstation User Guide                 | ND-30.056<br>ND-30.057<br>ND-60.242 |

|                 | Detailed information on ND-110, which is also<br>the ND-110PCX, can be found in the following m                                        | applicable to<br>manuals:           |

|                 | ND-110 Functional Description                                                                                                          | ND-06.026                           |

|                 | ND-110 Instruction Set                                                                                                                 | ND-06.029                           |

|                 | Rask Gate Arrays Technical Description                                                                                                 | ND-05.016                           |

|                 | ND-100 Test Program Description                                                                                                        | ND-30.005                           |

|                 | Information on the PC and its MS-DOS operating given in:                                                                               | g system is                         |

|                 | PC Technical Reference Manual                                                                                                          | ND-06.028                           |

|                 | MS-DOS Reference Manual                                                                                                                | ND-60.271                           |

|                 | The ND operating system SINTRAN, and all ND ap<br>covered in associated ND user guides. In part<br>reference is made to the following: | oplications, are<br>ticular,        |

|                 | SINTRAN III System Supervisor Guide<br>SINTRAN III System Documentation,                                                               | ND-30.003                           |

|                 |                                                                                                                                        |                                     |

Appendix A - Data Fields ND-60.112

$\mathbf{x}$

# TABLE OF CHAPTERS

\_\_\_\_\_

| CHAPTER 1  | OVERVIEW AND DATA SUMMARY                    |

|------------|----------------------------------------------|

| chapter 2  | FUNCTIONAL DESCRIPTION - SYSTEM AND HARDWARE |

| CHAPTER 3  | FUNCTIONAL DESCRIPTION - SOFTWARE            |

| CHAPTER 4  | HARDWARE DESCRIPTION                         |

| CHAPTER 5  | MICROPROGRAM DESCRIPTION                     |

| CHAPTER 6  | SOFTWARE DESCRIPTION                         |

| CHAPTER 7  | MAINTENANCE                                  |

| CHAPTER 8  | Parts data                                   |

| APPENDIX A | LOGIC DIAGRAMS                               |

| APPENDIX B | Signals list                                 |

| APPENDIX C | PC Expansion Bus                             |

| appendix D | PAL SPECIFICATIONS                           |

| APPENDIX E | BUTTERFLY-110 LINK SETTINGS                  |

| appendix F | BUTTERFLY KEYBOARD SPECIFICATION             |

| GLOSSARY   |                                              |

| INDEX      |                                              |

# DETAILED TABLE OF CONTENTS

## Chapter

## Page

# 1 OVERVIEW AND DATA SUMMARY

| 1.1                                     | INTRODUCTION                                                                                                                       | 1-5                              |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4 | SYSTEM CONFIGURATION<br>Basic hardware<br>Cluster configuration plus options<br>Communications Controller<br>Summary of components | 1-7<br>1-7<br>1-8<br>1-9<br>1-10 |

| 1.3<br>1.3.1<br>1.3.2                   | BUTTERFLY-110 SYSTEM UNIT<br>PC features<br>ND-110PCX                                                                              | 1-12<br>1-12<br>1-12             |

| 1.4                                     | BUTTERFLY DISPLAY UNIT                                                                                                             | 1-13                             |

| 1.5<br>1.5.1<br>1.5.2                   | BUTTERFLY KEYBOARD /MOUSE /BAR CODE READER                                                                                         | 1-13<br>1-13<br>1-14             |

| 1.6                                     | CENTRONICS PRINTER PARALLEL INTERFACE                                                                                              | 1-14                             |

| 1.7                                     | SERIAL INTERFACE                                                                                                                   | 1-14                             |

| 1.8<br>1.8.1<br>1.8.2<br>1.8.3          | DATA SUMMARY<br>Mechanical<br>Electrical<br>Environmental                                                                          | 1-15<br>1-15<br>1-15<br>1-16     |

# 2 FUNCTIONAL DESCRIPTION - SYSTEM AND HARDWARE

| 2.1     | OVERVIEW             | 2-5 |

|---------|----------------------|-----|

| 2.1.1   | Butterfly Main Units | 2-5 |

| 2.1.1.1 | System Unit          | 2-6 |

| 2.1.1.2 | Keyboard             | 2-7 |

| 2.1.1.3 | Display              | 2-7 |

| 2.1.1.4 | Mouse                | 2-7 |

| 2.1.1.5 | Hardware options     | 2-8 |

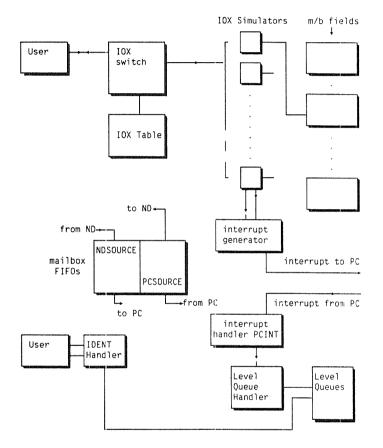

| 2.1.2<br>2.1.2.1<br>2.1.2.2<br>2.1.2.3<br>2.1.2.4                                                        | System Control<br>Functional elements<br>System start-up<br>I/O control<br>ND-PC communication                                                                                                                                                                  | 2-9<br>2-10                                                                          |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

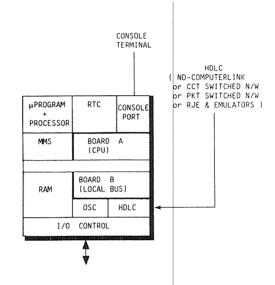

| 2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.2.9<br>2.2.10<br>2.2.11 | ND-110PCX FUNCTIONAL BLOCKS<br>Microprogram and processor (CPU)<br>Register File<br>Interrupt System<br>Memory Management System (MMS)<br>Test (console) port<br>Print Status<br>Installation Number<br>Memory (RAM)<br>I/O Control<br>Oscillator<br>Power Fail | 2-12<br>2-13<br>2-13<br>2-14<br>2-15<br>2-15<br>2-15<br>2-15<br>2-16<br>2-18<br>2-18 |

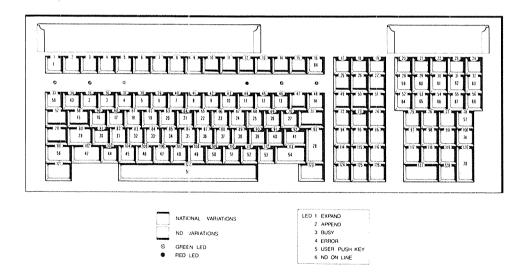

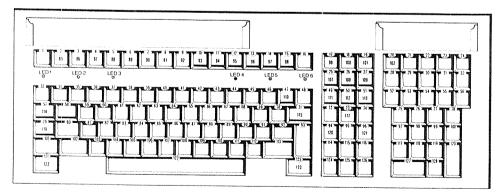

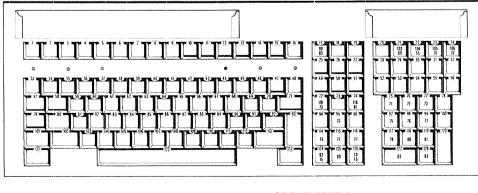

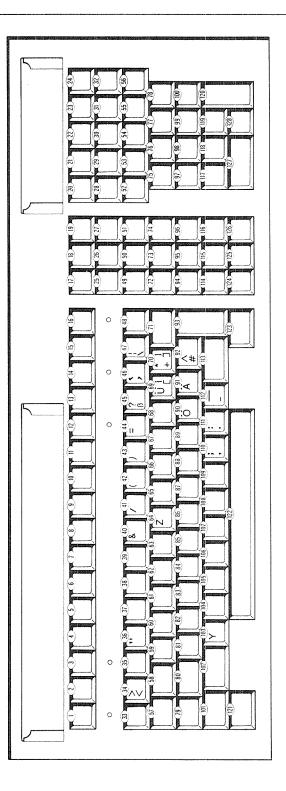

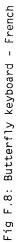

| 2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.4.1<br>2.3.4.1<br>2.3.4.2<br>2.3.4.3<br>2.3.4.4           | THE KEYBOARD<br>Summary of Features<br>IBM Compatibility<br>ND-NOTIS Compatibility<br>Added Features<br>Mouse<br>Bar Code Reader port<br>Function Keypad option<br>Template cards                                                                               | 2-19<br>2-23<br>2-23<br>2-24<br>2-24<br>2-25<br>2-25<br>2-25<br>2-26                 |

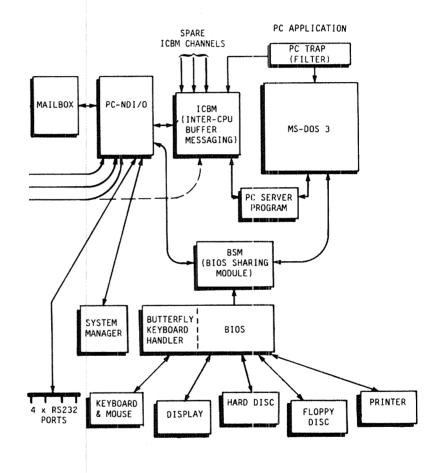

# 3 FUNCTIONAL DESCRIPTION - SOFTWARE

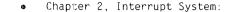

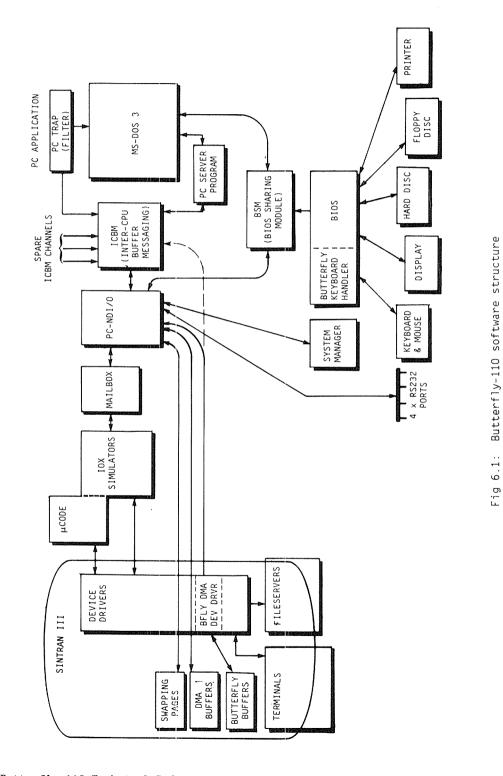

| 3.1    | INTRODUCTION        | 3-5  |

|--------|---------------------|------|

| 3.2    | INSTRUCTION SET     | 3-7  |

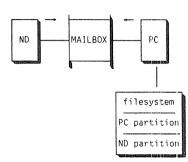

| 3.3    | SOFTWARE OVERVIEW   | 3-8  |

| 3.3.1  | General             | 3-8  |

| 3.3.2  | Signal box          | 3-8  |

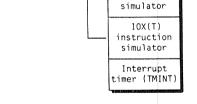

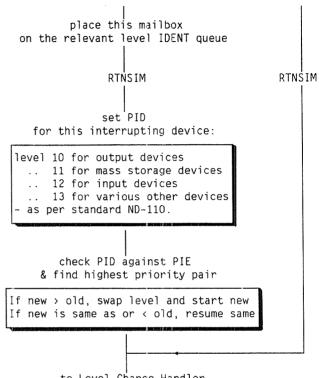

| 3.3.3  | Interrupts          | 3-10 |

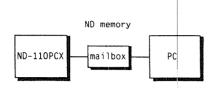

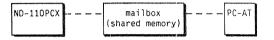

| 3.3.4  | Mailbox             | 3-11 |

| 3.3.5  | IOX simulators      | 3-13 |

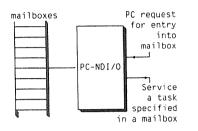

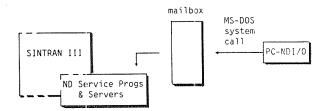

| 3.3.6  | PC-NDI/O            | 3-14 |

| 3.3.7  | System manager      | 3-14 |

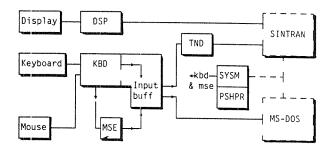

| 3.3.8  | Keyboard handler    | 3-15 |

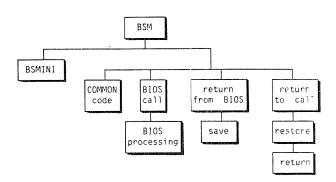

| 3.3.9  | BIOS sharing module | 3-15 |

| 3.3.10 | File access         | 3-16 |

| 3.3.11 | Print spooler       | 3-19 |

| 3.3.12 | PC server           | 3-19 |

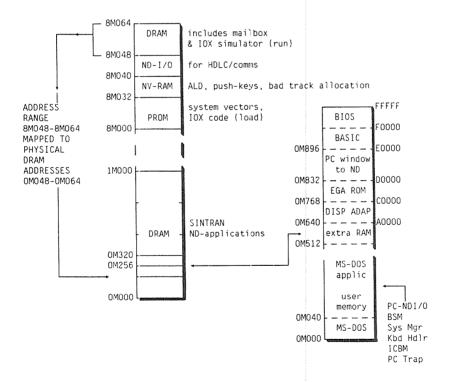

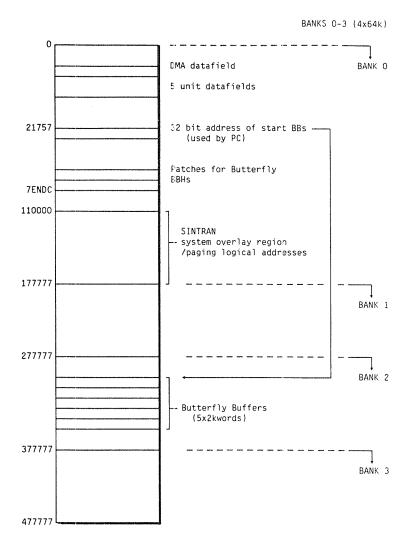

| 3.3.13 | Software memory map | 3-20 |

|        |                     |      |

| 4     | HARDWARE DESCRIPTION                |      |

|-------|-------------------------------------|------|

| 3.10  | SYSTEM MANAGER AND KEYBOARD HANDLER | 3-38 |

| 3.9   | FILE ACCESS                         | 3-36 |

| 3.9.1 | PC trap (filter)                    | 3-36 |

| 3.9.2 | Inter-CPU buffer messaging          | 3-36 |

| 3.9.3 | Fileserver (PCFSERV)                | 3-37 |

| 3.9.4 | Butterfly device drivers / buffers  | 3-37 |

| 3.8   | PC SIDE OF THE MAILBOX              | 3-32 |

| 3.8.1 | Interrupt handling                  | 3-32 |

| 3.8.2 | Disk handling                       | 3-34 |

| 3.8.3 | Asynchronous (serial port) handling | 3-34 |

| 3.8.4 | DMA device handling                 | 3-35 |

| 3.7   | ND SIDE OF THE MAILBOX              | 3-26 |

| 3.7.1 | Butterfly interrupt handling        | 3-26 |

| 3.7.2 | IDENT handling                      | 3-30 |

| 3.7.3 | IOX(T) handling                     | 3-31 |

| 3.6   | SENDING A MAILBOX                   | 3-24 |

| 3.6.1 | Mailbox queues                      | 3-24 |

| 3.6.1 | Send mailbox to PC (NDSOURCE)       | 3-24 |

| 3.6.2 | Send mailbox to ND (PCSOURCE)       | 3-25 |

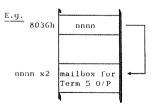

| 3.5   | MAILBOXES                           | 3-22 |

| 3.5.1 | Mailbox format                      | 3-22 |

| 3.5.2 | Disk mailbox data buffer            | 3-22 |

| 3.5.3 | Async mailbox data buffer           | 3-22 |

| 3.5.4 | Butterfly DMA data buffer           | 3-23 |

| 3.4   | DATA HANDLING                       | 3-21 |

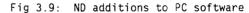

| 4.1   | HARDWARE MODULES       | 4-5  |

|-------|------------------------|------|

| 4.2   | THE PC                 | 4-7  |

| 4.2.1 | References             | 4-7  |

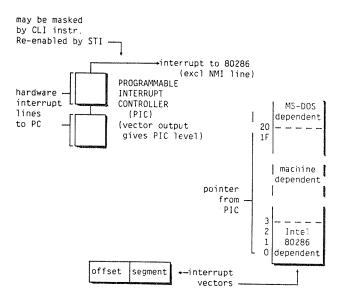

| 4.2.2 | PC interrupt system    | 4-7  |

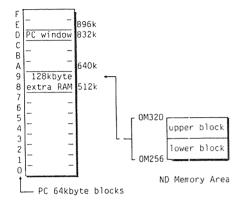

| 4.2.3 | PC memory assignments  | 4-7  |

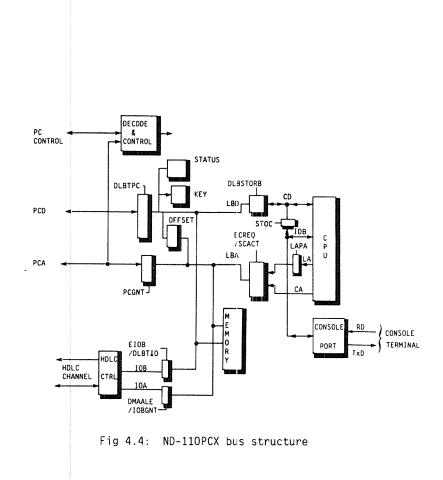

| 4.3   | THE ND-110PCX COMPUTER | 4-8  |

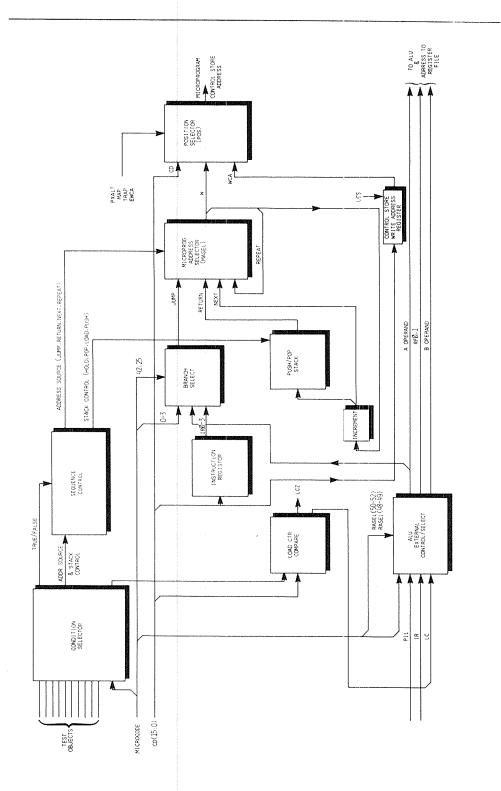

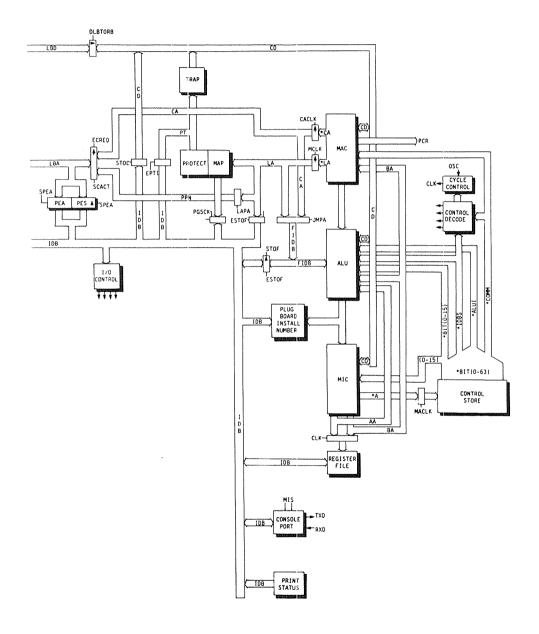

| 4.3.1 | Block diagram          | 4-8  |

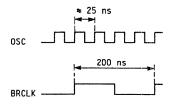

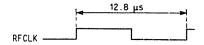

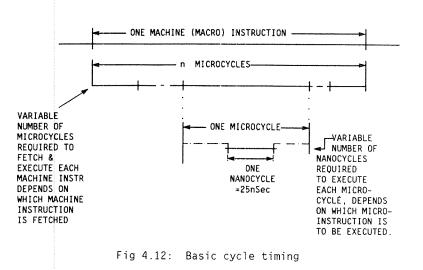

| 4.3.2 | Basic clocks           | 4-10 |

| 4.3.3 | Internal bus system    | 4-10 |

|       |                        |      |

| 4.3.4    | Processor                                      | 4-12 |

|----------|------------------------------------------------|------|

| 4.3.4.1  | General                                        | 4-12 |

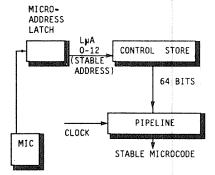

| 4.3.4.2  | Control Store and pipeline                     | 4-13 |

| 4.3.4.3  | The MIC                                        | 4-14 |

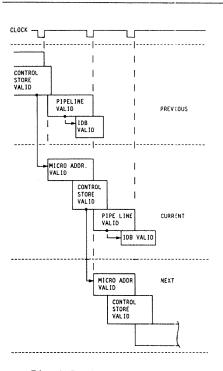

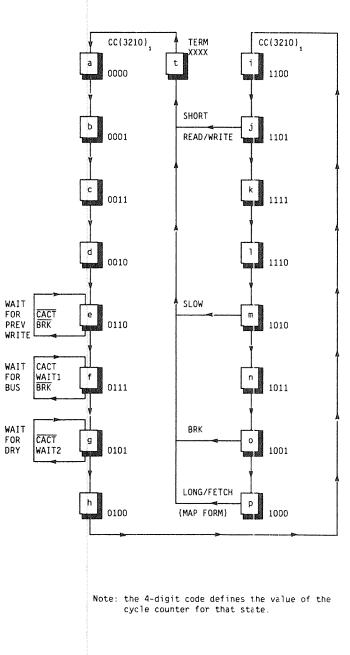

| 4.3.4.4  | Cycle timing and control                       | 4-19 |

| 4.3.4.5  | Register File                                  | 4-26 |

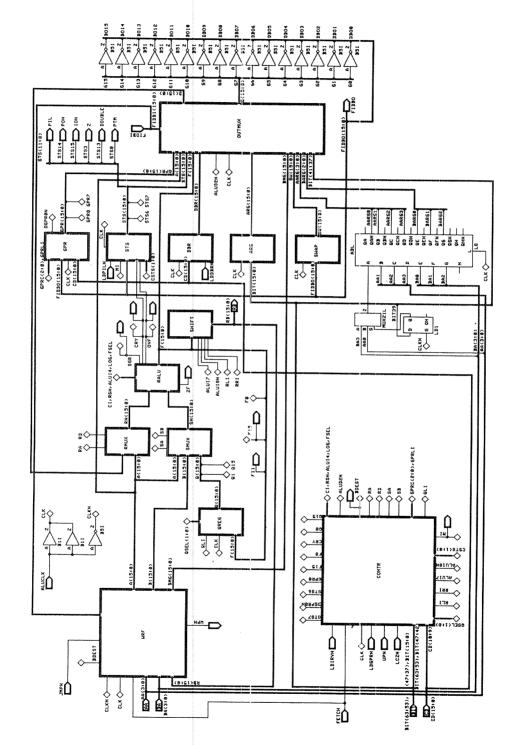

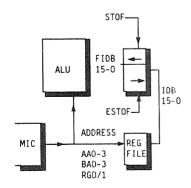

| 4.3.4.6  | The ALU                                        | 4-26 |

| 4.3.4.7  | The MAC                                        | 4-32 |

| 4.3.4.8  | Control signal decodes/functions               | 4-34 |

| 4.3.4.9  | CPU I/O registers                              | 4-34 |

| 4.3.4.10 |                                                | 4-35 |

| 4.3.4.10 | •                                              |      |

|          | Print status/installation number               | 4-37 |

| 4.3.5    | Memory                                         | 4-38 |

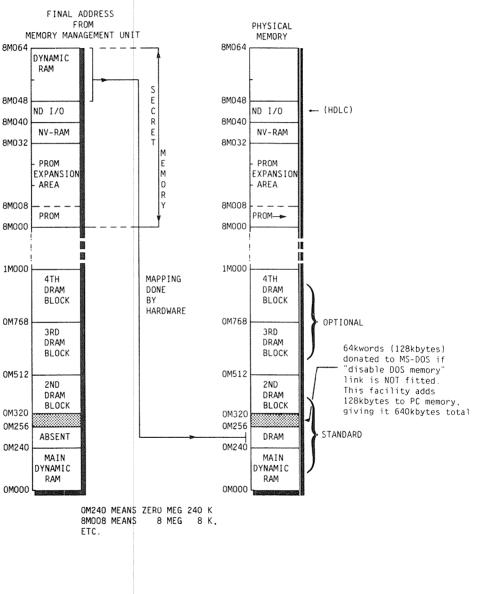

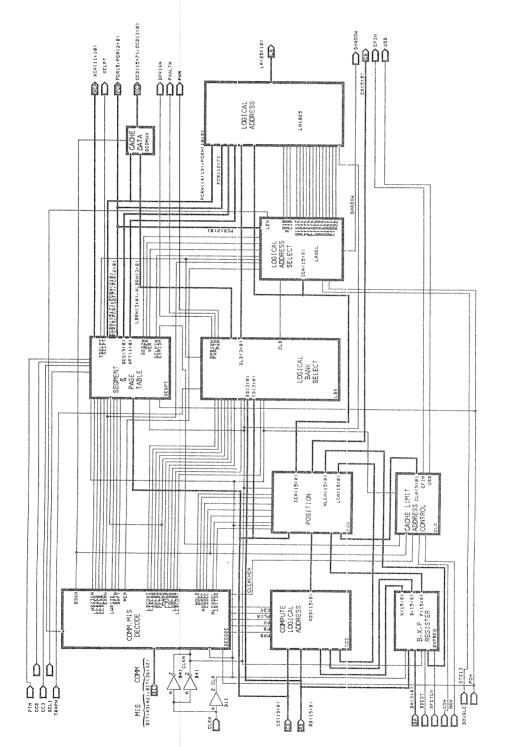

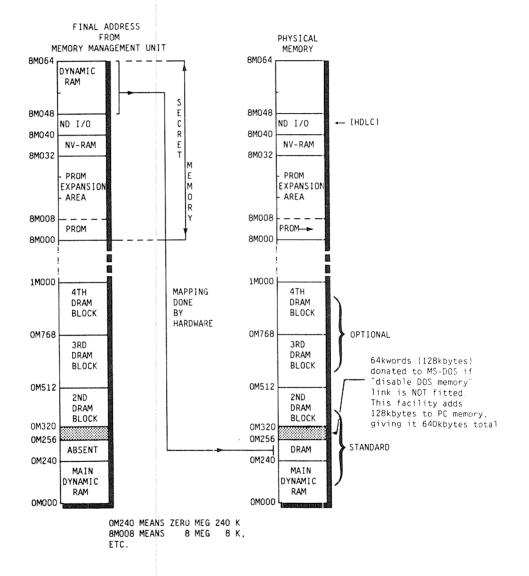

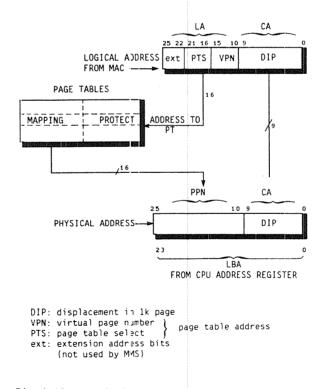

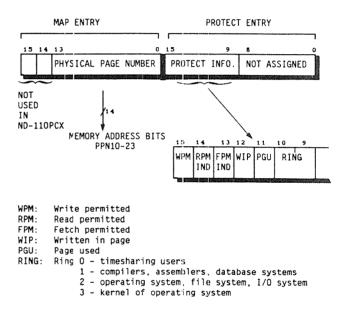

| 4.3.5.1  | Memory management principles                   | 4-38 |

| 4.3.5.2  | Memory map                                     | 4-38 |

| 4.3.5.3  | Memory addressing                              | 4-42 |

| 4.3.5.4  | Read/write/refresh cycles                      | 4-48 |

| 4.3.5.5  | Parity and error checking                      | 4-54 |

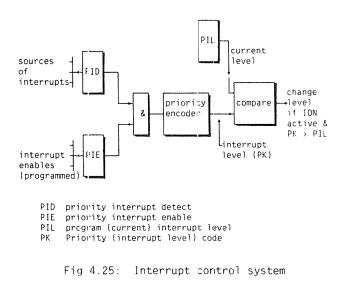

| 4.3.6    | Interrupt system                               | 4-56 |

| 4.3.6.1  | Interrupt mechanism                            | 4-56 |

| 4.3.6.2  | Interrupt controller                           | 4-58 |

| 4.3.6.3  | Signal box interrupts                          | 4.59 |

| 4.3.6.4  | Internal interrupts                            | 4-60 |

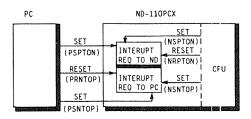

| 4.3.7    | PC-NDI/O system                                | 4~64 |

| 4.3.7.1  | PC expansion bus                               | 4-64 |

| 4.3.7.2  |                                                |      |

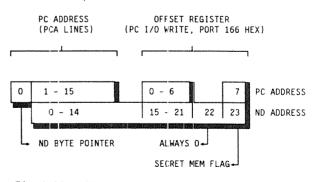

|          | PC access to ND memory                         | 4-64 |

| 4.3.7.3  | PC program I/O                                 | 4-64 |

| 4.3.7.4  | PC-ND status and control registers             | 4-66 |

| 4.3.8    | ND-I/O system                                  | 4-67 |

| 4.3.8.1  | HDLC & DMA                                     | 4-68 |

| 4.3.8.2  | Console port                                   | 4-70 |

| 4.3.8.3  | Panel processor                                | 4-70 |

| 4.3.9    | Real-time clock                                | 4-71 |

| 4.3.10   | Power fail and stop                            | 4-71 |

| 4.3.11   | Clear                                          | 4-71 |

|          |                                                |      |

| 4.4      | HARDWARE OPTIONS                               | 4-72 |

| 4.4.1    | Serial Communications Board plus Connector Box | 4-72 |

| 4.4.2    | Tape streamer                                  | 4-72 |

| 4.4.3    | Additional 1Mbyte RAM                          | 4-72 |

| 4.4.4    |                                                |      |

| 4.4.5    | HDLC communications                            | 4-73 |

|          | Plug-in modem                                  | 4-73 |

| 4.4.6    | External Winchester disk                       | 4-73 |

| 4.5      | ND 110DOV TEOMINAL DICOLAV HUTC                |      |

| 4.5      | ND-110PCX TERMINAL DISPLAY UNITS               | 4-74 |

| 4.6      | ND-110PCX TERMINAL KEYBOARD                    | 4-74 |

|          |                                                |      |

| 4.7      | MOUSE                                          | 4-74 |

| 4.8      | BAR CODE READER                                | 4-74 |

|          | en ood henden                                  |      |

| 5                                       | MICROROGRAM DESCRIPTION                                                                                                                                                    |                                      |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 5.1                                     | INTRODUCTION                                                                                                                                                               | 5-5                                  |

| 5.2                                     | HARDWARE ON THE MICROCODE BUS                                                                                                                                              | 5-5                                  |

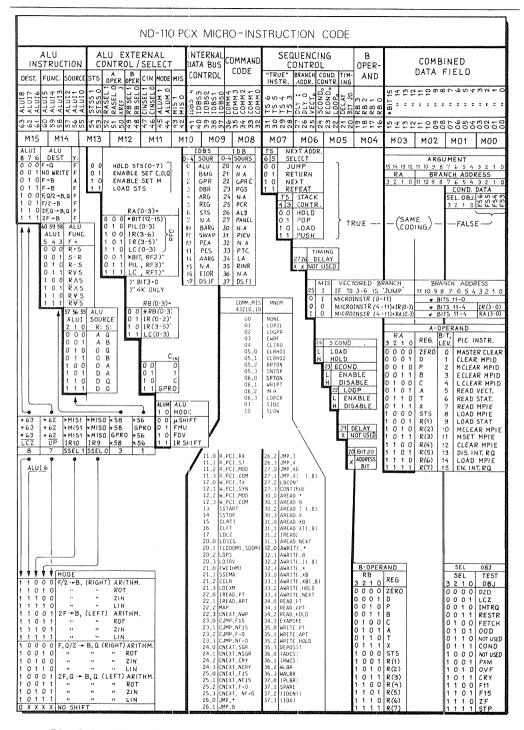

| 5.3<br>5.3.1<br>5.3.2                   | ND-110PCX MICROPROGRAM WORD FORMAT<br>Summary of changes from ND-100<br>Microinstruction word: field definitions                                                           | 5-9<br>5-9<br>5-10                   |

| 5.4<br>5.4.1<br>5.4.2<br>5.4.3          | RETURN FROM SIMULATION INSTRUCTION: RTNSIM<br>Interface to the simulation routines<br>Entry point interface (UPSIM routine)<br>Return from simulation (RTNSIM instruction) | 5-21<br>5-21<br>5-21<br>5-22         |

| 5.5<br>5.5.1<br>5.5.2<br>5.5.3<br>5.5.4 | WRITING MICROPROGRAM<br>Summary<br>Design of microcode<br>Assembly language considerations<br>Generating control store PROM                                                | 5-23<br>5-23<br>5-24<br>5-24<br>5-26 |

| 5.6                                     | MNEMONICS LIST                                                                                                                                                             | 5-27                                 |

| 6                                       | SOFTWARE DESCRIPTION                                                                                                                                                       |                                      |

| 6.1                                     | INTRODUCTION                                                                                                                                                               | 6-7                                  |

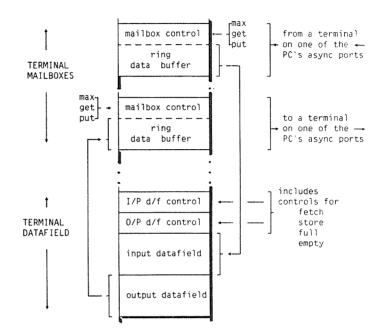

| 6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.3.1<br>6.2.3.2<br>6.2.4<br>6.2.5 | MAILBOX<br>Mailbox devices<br>Standard mailbox locations<br>Disk mailboxes<br>Floppy disk mailbox format<br>Hard disk mailbox format<br>Asynchronous (serial port) mailbox format<br>Butterfly DMA devices mailbox format | 6-10<br>6-12<br>6-12<br>6-13<br>6-13<br>6-14<br>6-15<br>6-17 |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

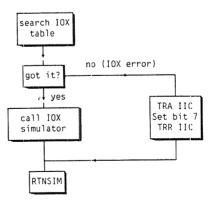

| 6.3                                                                    | IOX SIMULATION                                                                                                                                                                                                            | 6-19                                                         |

| 6.3.1                                                                  | Operation                                                                                                                                                                                                                 | 6-19                                                         |

| 6.3.2                                                                  | IOX simulator modules                                                                                                                                                                                                     | 6-21                                                         |

| 6.3.2.1                                                                | Tables and queues                                                                                                                                                                                                         | 6-21                                                         |

| 6.3.2.2                                                                | Signal box                                                                                                                                                                                                                | 6-23                                                         |

| 6.3.2.3                                                                | IOX simulator switch (IOXSWITCH)                                                                                                                                                                                          | 6-26                                                         |

| 6.3.2.4                                                                | IDENT handler (IDIOX)                                                                                                                                                                                                     | 6-27                                                         |

| 6.3.2.5                                                                | PC interrupt (PCINT)                                                                                                                                                                                                      | 6-27                                                         |

| 6.3.2.6                                                                | Timer (TMINT)                                                                                                                                                                                                             | 6-28                                                         |

| 6.3.3                                                                  | IOX instruction simulators                                                                                                                                                                                                | 6-29                                                         |

| 6.3.3.1                                                                | Terminal IOXs                                                                                                                                                                                                             | 6-29                                                         |

| 6.3.3.2                                                                | Hard disk IOXs                                                                                                                                                                                                            | 6-31                                                         |

| 6.3.3.3                                                                | Floppy disk IOXs                                                                                                                                                                                                          |                                                              |

| 6.3.3.4                                                                | Standard disk status and control words                                                                                                                                                                                    | 6-32                                                         |

| 6.3.4<br>6.3.5<br>6.3.6<br>6.3.7<br>6.3.8<br>6.4<br>6.4.1<br>6.4.2<br>6.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IOX 30x: the PC console as Terminal-1<br>IOX 10-13: Real time clock<br>Login display following logout<br>Other Butterfly-110 IOXs<br>Effects of no cache<br>BUTTERFLY-110 ASYNC DRIVER<br>Operation<br>MON 373: special INSTR<br>Terminal datafield extension                                                                                                                                                                                                                                                                                                                                    | 6-35<br>6-36<br>6-37<br>6-37<br>6-38<br>6-38<br>6-38<br>6-40<br>6-40                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

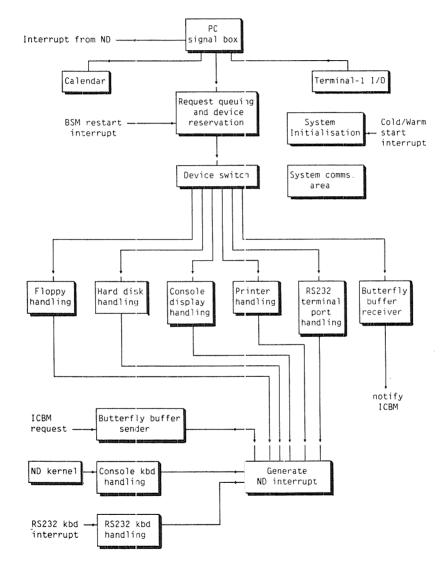

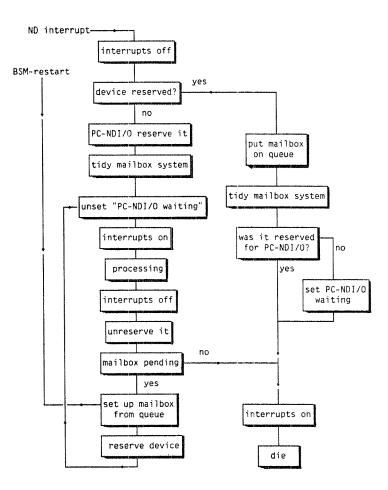

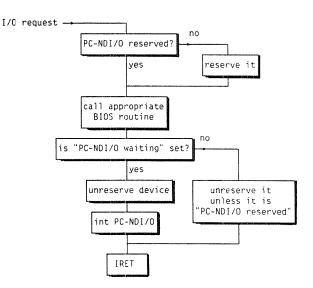

| 6.5<br>6.5.1<br>6.5.2<br>6.5.3.1<br>6.5.3.2<br>6.5.3.2<br>6.5.3.3<br>6.5.3.4<br>6.5.4.1<br>6.5.4.2<br>6.5.5.1<br>6.5.5.2<br>6.5.5.1<br>6.5.5.2<br>6.5.5.3.4<br>6.5.5.5.1<br>6.5.5.5.2<br>6.5.5.5.4<br>6.5.5.5.6<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.8<br>6.5.7<br>6.5.8<br>6.5.8<br>6.5.8<br>6.5.8<br>6.5.7<br>6.5.8<br>6.5.7<br>6.5.8<br>6.5.7<br>6.5.8<br>6.5.7<br>6.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5.7<br>6.5. | <pre>PC-NDI/O<br/>Basic structure<br/>Interrupts - PC signal box<br/>Calendar handling<br/>Get and Set commands<br/>Operation through signal box<br/>Get time<br/>Set time<br/>Terminal-1 operation<br/>Output<br/>Input<br/>PC Peripheral device handling<br/>Request queuing and device reservation<br/>Device switch<br/>Floppy disk handling<br/>Hard disk handling<br/>PC console display handling<br/>PC console keyboard handling<br/>Serial port handling<br/>Parallel port handling<br/>System initialisation<br/>ND-kernel<br/>System communications area<br/>PC interrupts used</pre> | 6-41<br>6-44<br>6-45<br>6-45<br>6-45<br>6-46<br>6-46<br>6-46<br>6-49<br>6-49<br>6-49<br>6-49<br>6-50<br>6-51<br>6-56<br>6-56<br>6-59<br>6-59<br>6-60<br>6-61 |

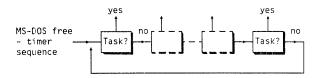

| $\begin{array}{c} 6.6\\ 6.6.1\\ 6.6.2\\ 6.6.3\\ 6.6.3.1\\ 6.6.3.2\\ 6.6.4\\ 6.6.4.1\\ 6.6.4.2\\ 6.6.4.4\\ 6.6.4.5\end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <pre>MULTITASKING PC SOFTWARE<br/>MS-DOS and BIOS<br/>Additional requirements for Butterfly-110<br/>Prerequisite MS-DOS information<br/>MS-DOS structure<br/>PC interrupt system<br/>Multitasking<br/>The sharing requirement<br/>PC-NDI/O multitasking control<br/>BSM to PC-NDI/O multitasking control<br/>Terminal manager multitasking</pre>                                                                                                                                                                                                                                                 | 6-62<br>6-62<br>6-63<br>6-64<br>6-64<br>6-66<br>6-66<br>6-66<br>6-66<br>6-68<br>6-69                                                                         |

| 6.7                                                                      | SYSTEM MANAGER                                                                                                                                                                           | 6-70                                                 |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 6.7.1                                                                    | Overview                                                                                                                                                                                 | 6-70                                                 |

| 6.7.2                                                                    | System modules                                                                                                                                                                           | 6-72                                                 |

| 6.7.3                                                                    | Keyboard compatibility                                                                                                                                                                   | 6-72                                                 |

| 6.7.3.1                                                                  | PC                                                                                                                                                                                       | 6-72                                                 |

| 6.7.3.2                                                                  | ND                                                                                                                                                                                       | 6-73                                                 |

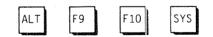

| 6.7.4                                                                    | New keyboard features                                                                                                                                                                    | 6-74                                                 |

| 6.7.5                                                                    | System manager                                                                                                                                                                           | 6-76                                                 |

| 6.7.6                                                                    | Keyboard driver                                                                                                                                                                          | 6-77                                                 |

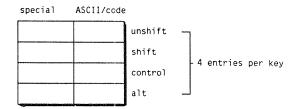

| 6.7.7                                                                    | Character format in input buffer                                                                                                                                                         | 6-80                                                 |

| 6.8                                                                      | ND SERVERS                                                                                                                                                                               | 6-81                                                 |

| 6.8.1                                                                    | ND file services available to the PC                                                                                                                                                     | 6-81                                                 |

| 6.8.2                                                                    | Communication between ND and PC                                                                                                                                                          | 6-82                                                 |

| 6.8.2.1                                                                  | Extensions to MON 144 (MAGTP)                                                                                                                                                            | 6-82                                                 |

| 6.8.2.2                                                                  | Status registers                                                                                                                                                                         | 6-85                                                 |

| 6.8.3                                                                    | File access requests from PC to ND-servers                                                                                                                                               | 6-85                                                 |

| 6.9<br>6.9.1<br>6.9.1.1<br>6.9.1.2<br>6.9.1.3<br>6.9.3<br>6.9.4<br>6.9.5 | PC SERVICE PROGRAMS<br>File access<br>Facilities<br>PC trap handler<br>Inter-CPU buffer messaging<br>File transfer program (DUPLI)<br>Print spooler service program (PSSP)<br>PC servers | 6-90<br>6-90<br>6-92<br>6-94<br>6-96<br>6-99<br>6-99 |

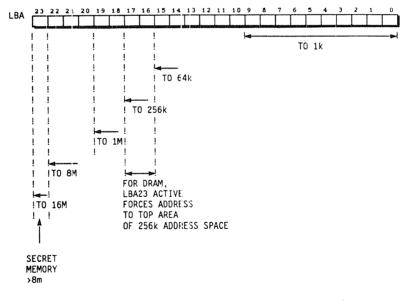

| 6.10                                                                     | SECRET MEMORY LOCATIONS                                                                                                                                                                  | 6-100                                                |

| 6.10.1                                                                   | PROM addresses                                                                                                                                                                           | 6-100                                                |

| 6.10.2                                                                   | NV-RAM addresses                                                                                                                                                                         | 6-100                                                |

| 6.10.3                                                                   | DRAM addresses                                                                                                                                                                           | 6-100                                                |

## 7 MAINTENANCE

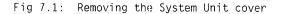

| 7.1   | SYSTEM UNIT ASSEMBLY             | 7-6  |

|-------|----------------------------------|------|

| 7.2   | PREVENTIVE MAINTENANCE           | 7-9  |

| 7.2.1 |                                  | 7-9  |

| 7.2.2 | Calendar battery                 | 7-9  |

| 7.2.3 | Floppy disk drive                | 7-9  |

| 7.2.4 | Tape streamer                    | 7-10 |

| 7.2.5 |                                  | 7-11 |

| 7.2.6 | Care of magnetic media           | 7-12 |

| 7.2.7 | Routine cable inspection         | 7-12 |

| 7.3   | SYSTEM COMPONENTS                | 7-13 |

| 7.3.1 | Butterfly terminals              | 7-13 |

| 7.3.2 | IBM-compatible PC-AT System Unit | 7-13 |

| 7.3.3 | EGA Board                        | 7-13 |

| 7.3.4 |                                  | 7-13 |

| 7.3.5 | Winchester Disk Drive            | 7-15 |

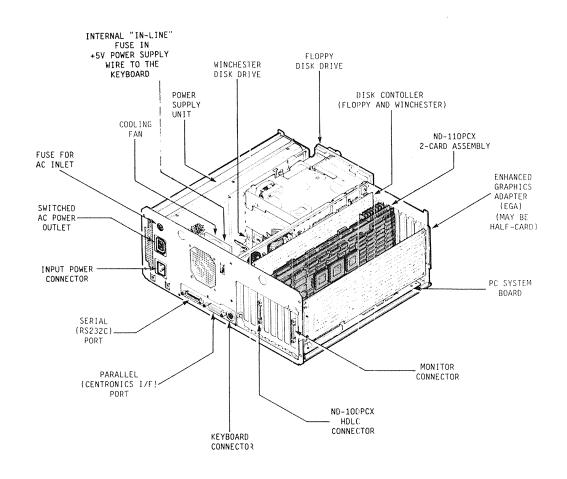

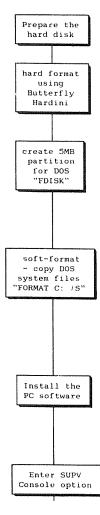

| 7.3.6<br>7.3.7<br>7.3.8<br>7.3.9<br>7.3.10<br>7.3.10.1<br>7.3.10.2<br>7.3.10.3<br>7.3.10.4<br>7.3.11<br>7.3.12                                                         | Floppy Disk Drive<br>Disk Controller Board<br>Keyboard<br>Mouse<br>ND-110PCX<br>Variants<br>Installation PROM<br>Memory upgrade<br>HDLC upgrade<br>Installing software on Winchester Disk<br>Extra RAM for MS-DOS                                                                                                                                                                                                                            | 7-15<br>7-16<br>7-16<br>7-16<br>7-16<br>7-16<br>7-17<br>7-19<br>7-19<br>7-19<br>7-20<br>7-22                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7.4<br>7.4.1<br>7.4.2<br>7.4.3                                                                                                                                         | INSTALLATION TOOLS<br>PC Setup<br>Butterfly Supervisor: System Parameter Definition<br>Butterfly Supervisor: Serial Port 1 & Modem Setup                                                                                                                                                                                                                                                                                                     | 7-23<br>7-23<br>7-31<br>7-35                                                                                                          |

| 7.5                                                                                                                                                                    | MOVING THE EQUIPMENT                                                                                                                                                                                                                                                                                                                                                                                                                         | 7-39                                                                                                                                  |

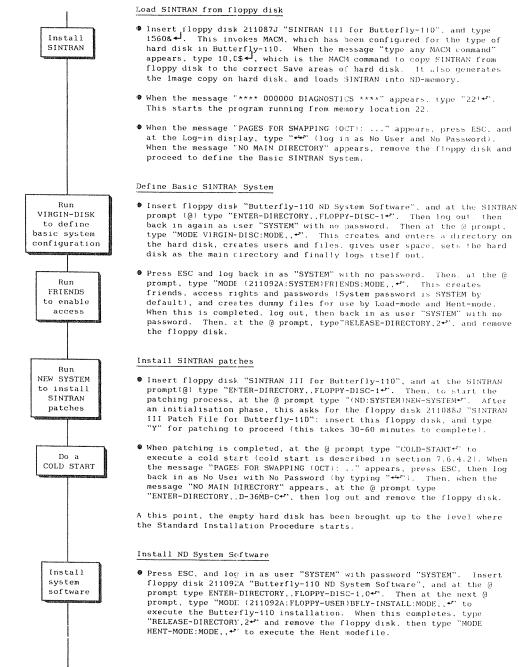

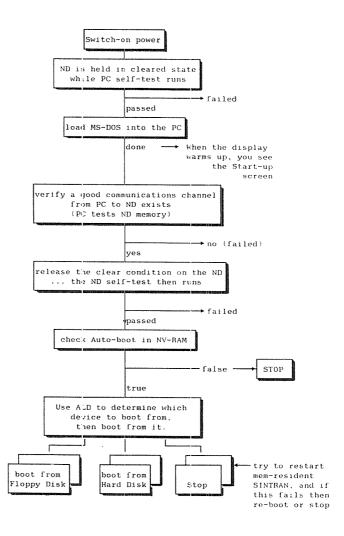

| 7.6<br>7.6.1<br>7.6.2.1<br>7.6.2.2<br>7.6.2.3<br>7.6.2.4<br>7.6.2.5<br>7.6.3.1<br>7.6.3.2<br>7.6.3.3<br>7.6.3.4<br>7.6.3.5<br>7.6.3.5<br>7.6.4.1<br>7.6.4.2<br>7.6.4.3 | CORRECTIVE MAINTENANCE<br>Basic system checks<br>Power-on self-test<br>Start-up sequence<br>Self-test operations<br>Self-test status flag (STS-FLAG)<br>Self-test error log (ERRLOG)<br>Self-test mailbox (st-mail)<br>Diagnostic programs<br>Butterfly diagnostic suite<br>Which diagnostic?<br>PC diagnostics<br>ND diagnostics<br>Butterfly Supervisor maintenance facilities<br>Console facility<br>Warm Start and Cold Start<br>Telefix | 7-41<br>7-44<br>7-44<br>7-45<br>7-46<br>7-47<br>7-50<br>7-51<br>7-51<br>7-53<br>7-55<br>7-62<br>7-68<br>7-69<br>,7-71<br>7-76<br>7-80 |

# 8 PARTS DATA

| 8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4 | SYSTEM UNIT<br>The PC<br>ND-110PCX CPU board 3401<br>ND-110PCX Local Bus board 3402<br>ND-110PCX Installation PROM board 3404 | 8-3<br>8-4<br>8-8 |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 8.2                                     | DISPLAY UNIT                                                                                                                  | 8-13              |

| 8.3                                     | KEYBOARD                                                                                                                      | 8-13              |

| 8.4                                     | MOUSE                                                                                                                         | 8-13              |

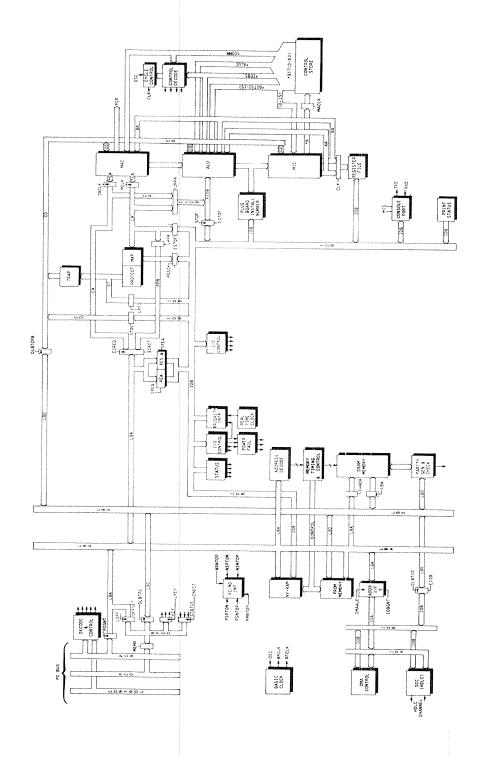

## APPENDIX A : LOGIC DIAGRAMS

Board 3401 : ND-110PCX CPU (4 sheets) Board 3402 : ND-110PCX Local Bus (4 sheets)

APPENDIX B : SIGNALS LIST

## APPENDIX C : PC EXPANSION BUS

# APPENDIX D: PAL SPECIFICATIONS

| PILOT BUTTERFLY PAL 1 : | COMMAND DECODE 1      | D-3  |

|-------------------------|-----------------------|------|

| PILOT BUTTERFLY PAL 2 : | COMMAND DECODE 2      | D-4  |

| PILOT BUTTERFLY PAL 3 : | COMMAND DECODE 3      | D-5  |

| PILOT BUTTERFLY PAL 4 : | COMMAND DECODE 4      | D-6  |

| PILOT BUTTERFLY PAL 5 : | COMMAND DECODE 5      | D-7  |

| PILOT BUTTERFLY PAL 6 : | IDB SOURCE DECODE 1   | D-8  |

| PILOT BUTTERFLY PAL 7 : | IDB SOURCE DECODE 2   | D-9  |

| PILOT BUTTERFLY PAL 8 : | BREAK DETECT          | D-10 |

| PILOT BUTTERFLY PAL 9 : | CYCLE TYPE DECODE     | D-11 |

| PILOT BUTTERFLY PAL 10: | CYCLE LENGTH DECODE   | D-12 |

| PILOT BUTTERFLY PAL 11: | CONDITION CONTROL     | D-13 |

| PILOT BUTTERFLY PAL 12: | CLOCK GENERATION      | D-14 |

| PILOT BUTTERFLY PAL 13: | MMU CONTROL           | D-15 |

| PILOT BUTTERFLY PAL 14: | TRAP 1                | D-16 |

| PILOT BUTTERFLY PAL 15: | TRAP 2                | D-17 |

| PILOT BUTTERFLY PAL 16: | TRAP 3                | D-18 |

| PILOT BUTTERFLY PAL 17: | PC I/F CONTROL        | D-19 |

| PILOT BUTTERFLY PAL 18: | PC I/O ADDRESS DECODE | D-20 |

| PILUI BUITERFLY PAL 19: | LOCAL BUS ADDRESS DECODER | D-21 |

|-------------------------|---------------------------|------|

| PILOT BUTTERFLY PAL 20: | LOCAL BUS ADDRESS ARBITER | D-23 |

| PILOT BUTTERFLY PAL 21: | LOCAL BUS CONTROL         | D-26 |

| PILOT BUTTERFLY PAL 22: | I/O BUS CONTROL           | D-27 |

| PILOT BUTTERFLY PAL 23: | MEMORY CONTROL            | D-28 |

# APPENDIX E: BUTTERFLY-110 LINK SETTINGS

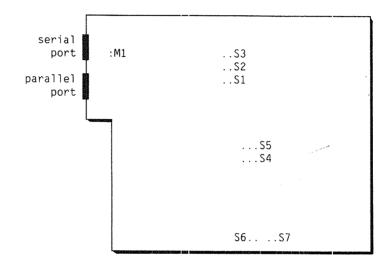

| E.1 | ND-110PCX LOCAL | BUS BOARD | (3402) |                  | <br>E-3 |

|-----|-----------------|-----------|--------|------------------|---------|

| E.2 | PC SYSTEM BOARD |           |        | •••••••••••••••• | <br>E-4 |

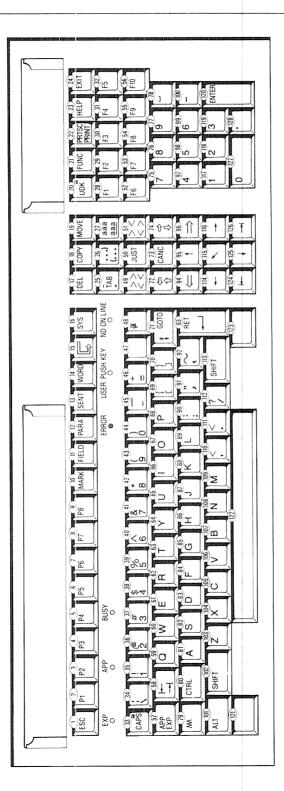

# APPENDIX F: KEYBOARD SPECIFICATION

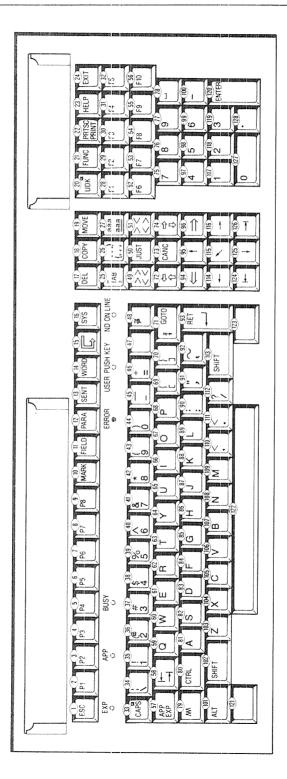

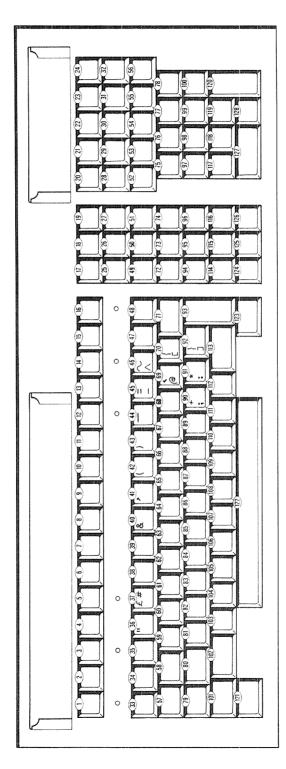

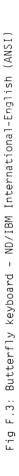

| 1     | INTRODUCTION                          | F-5  |

|-------|---------------------------------------|------|

| 1.1   | IBM compatibility                     | F-5  |

| 1.2   | NOTIS compatibility                   | F-6  |

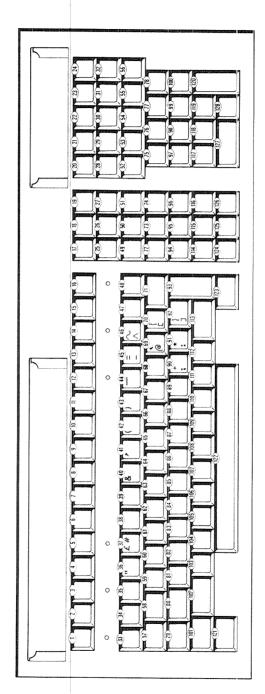

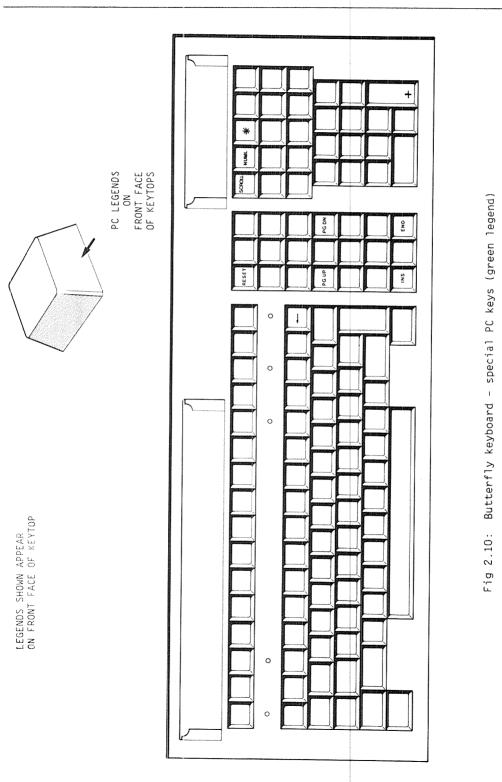

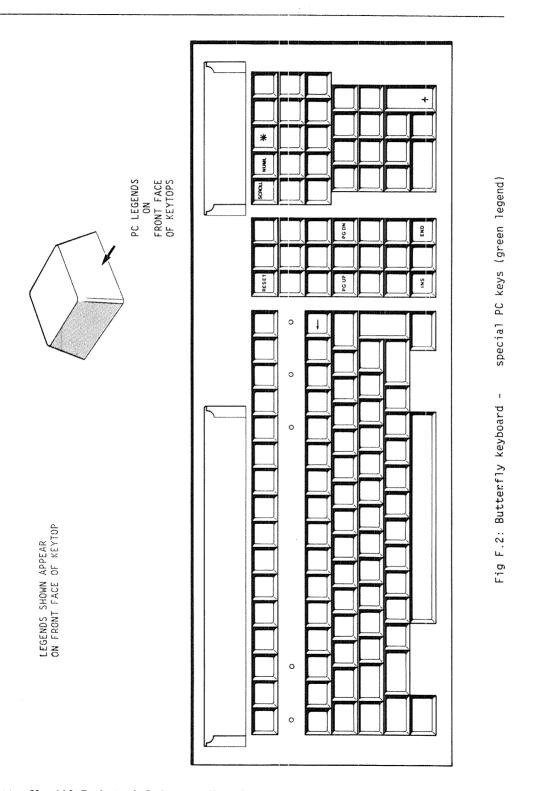

| 1.3   | Standard keyboard layout and legends  |      |

| 2     | NEW FEATURES                          | F-15 |

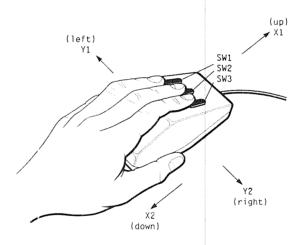

| 2.1   | Mouse                                 |      |

| 2.1.1 | Mouse position                        |      |

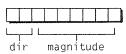

| 2.1.2 | Position coding                       | F-16 |

| 2.1.3 | Push button coding                    | F-17 |

| 2.2   | Serial port / Bar Code Reader         |      |

| 2.2.1 | Serial input                          |      |

| 2.2.2 | Serial output                         |      |

| 2.2.3 | Data format                           |      |

| 2.3   | Separate function keypad              | F-19 |

| 2.4   | Template card guides                  |      |

| 3     | SOFTWARE SPECIFICATIONS               | F-21 |

| 3.1   | Initialization                        |      |

| 3.2   | System Unit model                     |      |

| 3.3   | Interface signal standards            |      |

| 3.4   | Communication protocols               | F-22 |

| 3.5   | Self-test                             |      |

| 3.6   | Initialization acknowledge            |      |

| 3.7   | Scan codes                            |      |

| 3.8   | Special case handling                 | F-23 |

| 3.8.1 | Separation of numeric pad and cursors | F-23 |

| 3.8.2 | Numlock                               | F-24 |

| 3.8.3 | Lock indicators                       |      |

| 3.9   | Typematic action                      |      |

| 3.10  | Ring buffer                           |      |

| 3.11  | PROM Size                             |      |

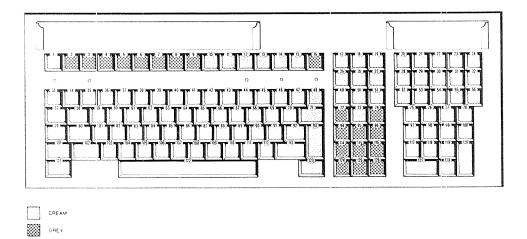

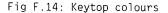

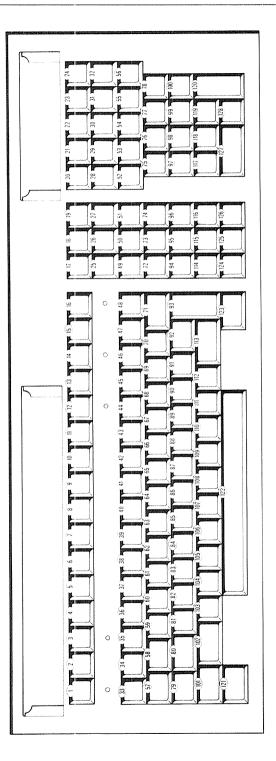

| 4<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7  | ELECTRO-MECHANICAL SPECIFICATION<br>Keystation layout and keytop colours<br>Function pad<br>Mouse port<br>LED layout<br>Bar Code Reader<br>System Unit cable and connectors<br>Other engineering specifications                     | F-27<br>F-27<br>F-29<br>F-30<br>F-30<br>F-30<br>F-31 |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.2<br>5.2.3 | KEYBOARD TO SYSTEM UNIT COMMUNICATION<br>Communication with standard IBM PC<br>Communication with IBM PC-AT<br>Standard commands from DOS/BIOS<br>Standard messages from keyboard<br>Additions to standard commands to the keyboard | F-32<br>F-32<br>F-33<br>F-33<br>F-34<br>F-35         |

| 6                                                   | CONVERSION OF KEYSTROKE TO SYSTEM SCAN CODES AND BIOS OUTPUT .                                                                                                                                                                      | F-36                                                 |

| 6.1<br>6.2<br>6.3<br>6.4                            | Direct IBM PC equivalent keys<br>NOTIS-compatible keys<br>Keys not having same scan codes in all states<br>Mouse push buttons                                                                                                       | F-37<br>F-39<br>F-40<br>F-42                         |

| 7                                                   | SYSTEM TO "AT" SCAN CODE CONVERSION TABLE                                                                                                                                                                                           | F-43                                                 |

# CHAPTER 1 Overview and Data Summary

TABLE OF CONTENTS

•

| Section                                 |                                                                                                                                    | Page                             |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.1                                     | INTRODUCTION                                                                                                                       | 1-5                              |

| 1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4 | SYSTEM CONFIGURATION<br>Basic hardware<br>Cluster configuration plus options<br>Communications Controller<br>Summary of components | 1-7<br>1-7<br>1-8<br>1-9<br>1-10 |

| 1.3<br>1.3.1<br>1.3.2                   | BUTTERFLY-110 SYSTEM UNIT                                                                                                          | 1-12<br>1-12<br>1-12             |

| 1.4                                     | BUTTERFLY DISPLAY UNIT                                                                                                             | 1-13                             |

| 1.5<br>1.5.1<br>1.5.2                   | BUTTERFLY KEYBOARD /MOUSE /BAR CODE READER                                                                                         | 1-13<br>1-13<br>1-14             |

| 1.6                                     | CENTRONICS PRINTER PARALLEL INTERFACE                                                                                              | 1-14                             |

| 1.7                                     | SERIAL INTERFACE                                                                                                                   | 1-14                             |

| 1.8<br>1.8.1<br>1.8.2<br>1.8.3          | DATA SUMMARY<br>Mechanical<br>Electrical<br>Environmental                                                                          | 1-15<br>1-15<br>1-15<br>1-16     |

| - | <br> | 101 Mar |  | <br><u></u> |  |                                     | <br> |  |           |

|---|------|---------|--|-------------|--|-------------------------------------|------|--|-----------|

|   |      |         |  |             |  |                                     |      |  |           |

|   | •    |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  | 5. 1. CO. |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  | S Lines   |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  | N. S. S.  |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     | ,    |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  | and that  |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  | A COMPANY OF THE OWNER OF THE OWNER |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  | Station . |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  | Sent Sert |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  | Sal Saure |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

|   |      |         |  |             |  |                                     |      |  |           |

Butterfly-110 Technical Reference Manual

# LIST OF ILLUSTRATIONS

| Figure                          |                                                                                                                                                                                | Page              |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | The Butterfly-110<br>Example Teamstation configuration<br>Interconnection of units<br>Enhancement capability in the Butterfly-110 system<br>Butterfly-110 communications ports | 1-6<br>1-7<br>1-8 |

\_\_\_\_\_

### **1.1 INTRODUCTION**

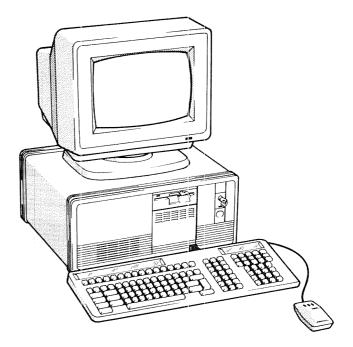

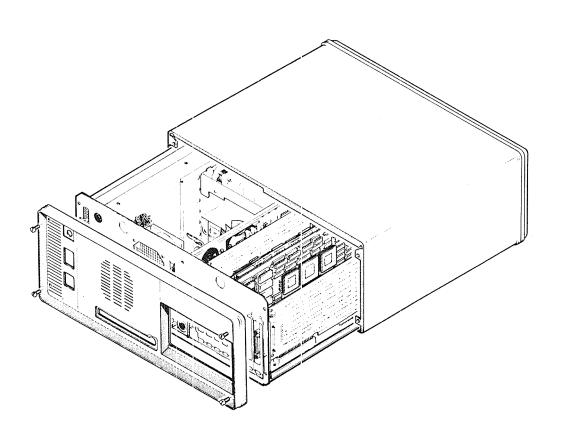

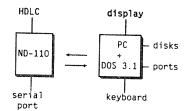

BUTTERFLY-110 (fig 1.1) is a ND-110PCX computer which coexists with an IBM-compatible PC-AT computer, inside the enclosure of the PC-AT.

Fig 1.1: The Butterfly-110

The OWS-110 offers in one unit the functionality of an IBM PC-AT, with all its currently available software running under MS-DOS, coupled with the extensive range of ND software (e.g. the NOTIS range) which runs under ND's SINTRAN operating system. Information in OWS-110 is freely interchangeable between the PC and ND operating systems, so that files created using the PC system may then be used by the ND system, and vice versa.

A centronics parallel printer port and RS232 serial port are provided as standard. Also included as standard is a Mouse, which connects to the Keyboard. A Bar Code Reader port is included in the keyboard, to suit connection of a Bar Code Reader wand.

Options include a Communications Controller board. This board provides a further 4xRS232 serial ports, for connection of ND-compatible terminals/devices to Butterfly-110. When one or more terminals are connected to these serial ports, then a clustered environment is created around the Butterfly-110, with the terminals running from the ND-110PCX. This configuration is called a Butterfly TEAMSTATION. An example of such an arrangement is shown in fig 1.2.

PRINTER

Fig 1.2: Example Teamstation configuration

In this configuration, the Butterfly-110 User may run ND or IBM-PC-compatible application packages, while the other users in the cluster may run ND application packages.

If these cluster terminals are also PCs, then a user environment is created in which all the terminals may be operated as PCs and as ND terminals.

### 1.2 SYSTEM CONFIGURATION

### 1.2.1 Basic hardware

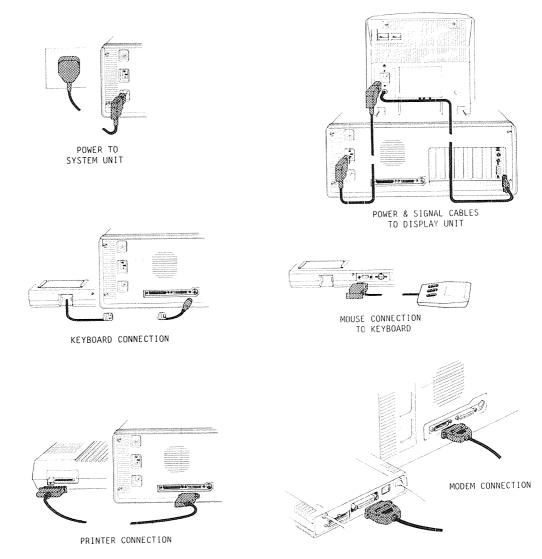

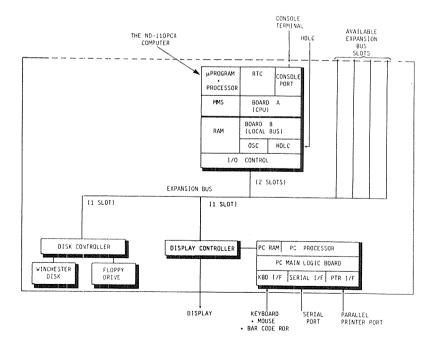

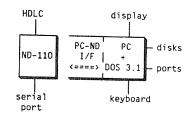

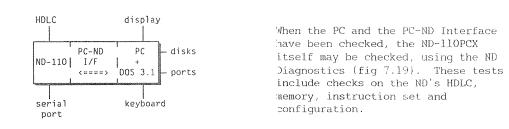

Fig 1.3 shows the interconnection between the main units in Butterfly-110:

Fig 1.3: Interconnection of units

#### 1.2.2 Cluster configuration plus options

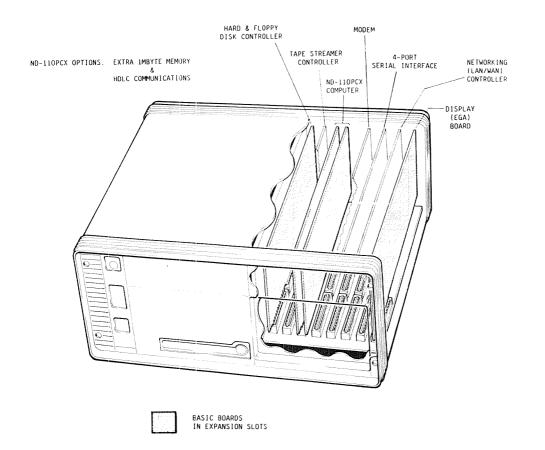

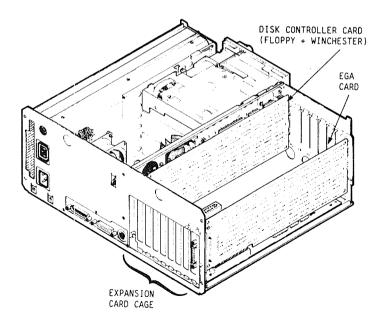

Fig 1.4 illustrates how the basic Butterfly-110 may be enhanced, by adding:

- a Communications Controller board, with connector box. See section 1.2.3.

- extra 1Mbyte RAM (to give a total of 2Mbytes).

- HDLC communications to a local computer system, for example, using ND's Computerlink.

Fig 1.4: Enhancement capability in the Butterfly-110 system

Space is available in the expansion card cage of the PC-AT to fit further cards. For example:

- a tape streamer controller card. connecting to a Tape Streamer cartridge device.

- an asynchronous modem communications card.

- a networking (LAN/WAN) interface card.

In addition to the Mouse, the Keyboard includes facility to connect a Bar Code Reader and an external Function Keypad.

## 1.2.3 Communications Controller

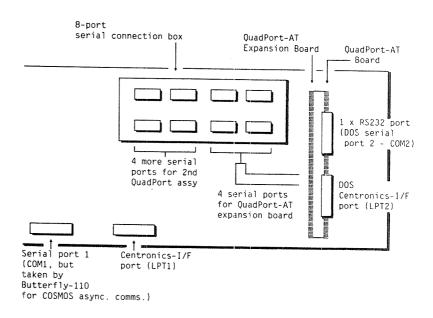

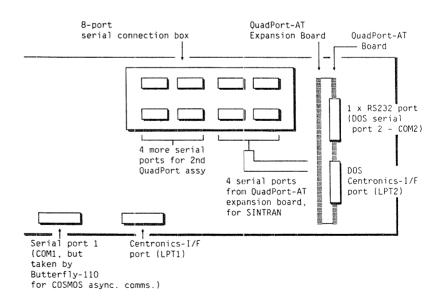

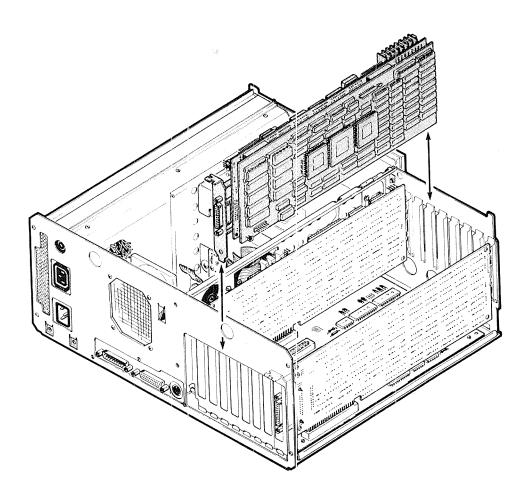

Fig 1.5 shows how adding the InterQuadram Communications Controller board extends the Butterfly-110 terminal to provide TEAMSTATION capability for up to four more terminals.

Fig 1.5: Butterfly-110 communications ports

DOS serial ports 1 and 2 Serial port 1 (native to the PC) is the DOS "COM1" port. In Butterfly-110, it is taken away from DOS by the Butterfly software which runs on the PC, and used for ND's COSMOS asynchronous communication facility.

Serial port 2 on the Quad-port-AT board is the DOS "COM2" port. To allow DOS to use this port, the Butterfly-110 software in the PC redirects it to the new value for COM2.

Parallel portsPort LPT1 (native to the PC) provides a centronics-compatibleLPT1 and LPT2interface for connection of a suitable printer. The<br/>print-spooling software shares this port between the PC's DOS<br/>and ND's SINTRAN operating systems.

Port LPT2 also provides a centronics-compatible interface. It is however only available to DOS.

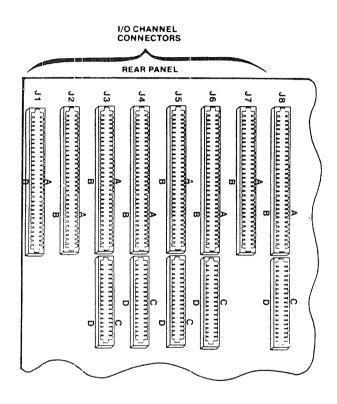

Quad-port A connection on the Quad-port-AT Expansion board provides the "TEAMSTATION" interface for four serial ports. These are brought out to a 4-port serial connection box, which mounts on the rear of the System Unit. Any serial-driven device supported by the software running on the ND-110PCX may be connected to this interface - e.g. ND-compatible terminals, or serial printer.

> If ND-compatible terminals are connected, they may run any of the ND application programs available in Butterfly-110. Any OWS-10/12 terminal which is also a PC may then be used both as a stand-alone PC and as an ND terminal running on Butterfly-110's ND-110PCX.

#### 1.2.4 Summary of components

Standard hardware System Unit (floppy disk and 40Mbyte hard disk, RS232 port and parallel port), Colour Display Unit with EGA graphics, Butterfly Keyboard (NOTIS and PC compatible), Mouse.

Operating system <u>MS-DOS for the PC</u> software

Additional Butterfly-110 programs run under the PC's MS-DOS to handle communication between the PC's 80286 microprocessor and the ND-110PCX, and to accommodate the System Manager and associated software which enables the PC and the ND-110PCX to share the same display, keyboard, disk storage, printer, etc.

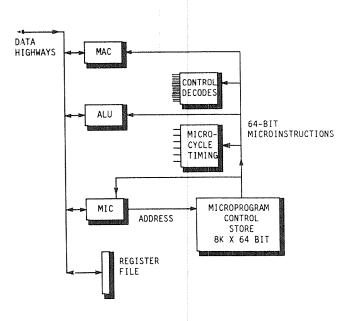

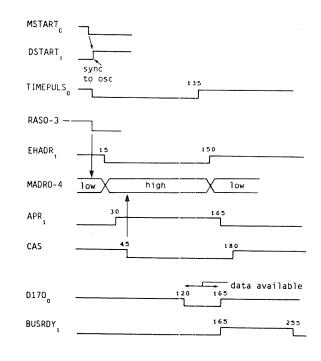

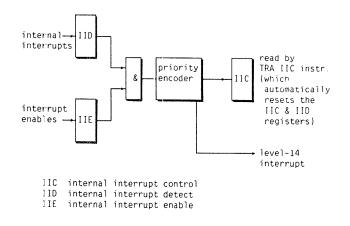

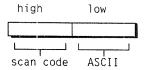

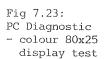

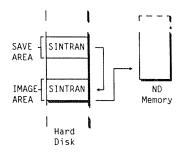

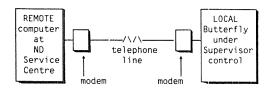

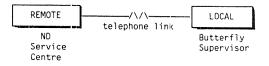

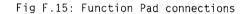

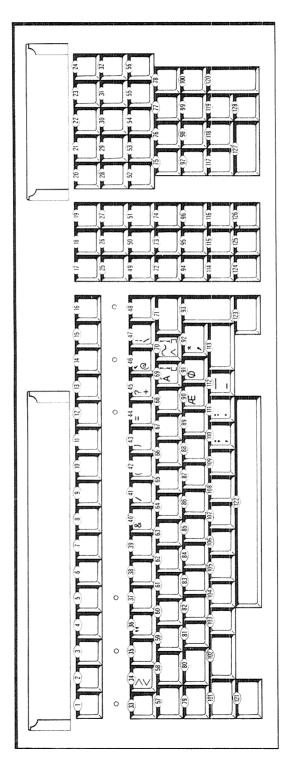

#### SINTRAN III/VSX for the ND-110PCX