NORD-10/S

Reference Manual

## NORSK DATA A.S.

### NORD-10/S Reference Manual

# **REVISION RECORD** Revision Notes 04/77 **Original Printing** 06/77 Revision A The following pages have been revised: 2-7, 3-1, 3-2, 3-23, 3-31, 3-38, 3-45, 3-46, 3-56, 3-57, 3-60, 3-63, 3-65, 4-1, 4-2, 4-3, 5-1, 5-2, 5-3, 5-13, 6-2, 6-5, 6-6, 6-7, 6-8, 6-10, 7-3, 8-7, 8-10, 9-6, 9-7, A-2, B-1.

NORD-10/S — Reference Manual Publication No. ND-06.008.01

#### TABLE OF CONTENTS

+ + +

| Section:                                                                                              |                                                                                                                                                                                                     | Page:                                                      |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 1                                                                                                     | INTRODUCTION                                                                                                                                                                                        | 1-1                                                        |

| 1.1<br>1.2<br>1.3                                                                                     | General Characteristics<br>Peripheral Equipment<br>Software                                                                                                                                         | 1–1<br>1–3<br>1–4                                          |

| 2                                                                                                     | SYSTEM ARCHITECTURE                                                                                                                                                                                 | 2-1                                                        |

| 2.1<br>2.2<br>2.2.1<br>2.2.2                                                                          | Introduction<br>Central Processor<br>Register Block<br>Indicators                                                                                                                                   | 2-1<br>2-3<br>2-6<br>2-7                                   |

| 2.3<br>2.4<br>2.5<br>2.5.1<br>2.5.2<br>2.5.2.1<br>2.5.2.2<br>2.5.2.3<br>2.5.2.4<br>2.5.2.5<br>2.5.2.6 | 32-Bit Double Word                                                                                                                                                                                  | 2-8 2-11 2-14 2-14 2-15 2-15 2-15 2-16 2-16                |

| 2.6<br>2.7                                                                                            | Interrupt System<br>Memory Management System                                                                                                                                                        | 2—19<br>2—21                                               |

| 3                                                                                                     | INSTRUCTION REPERTOIRE                                                                                                                                                                              | 3-1                                                        |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7                                    | Memory Reference Instructions Addressing Structure Store Instructions Load Instructions Arithmetical and Logical Instructions Sequencing Instructions Byte Instructions Register Block Instructions | 3-4<br>3-4<br>3-13<br>3-15<br>3-16<br>3-19<br>3-21<br>3-22 |

| Section:                                                 |                                                                                                                                                       | Page:                                |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 3.2<br>3.2.1<br>3.2.1.1<br>3.2.1.2                       | Operate Instructions Floating Point Conversion Instructions Standard 48-Bit Floating Point Conversion Optional 32-Bit Floating Point Conversion       | 3-24<br>3-24<br>3-26                 |

| 3.2.2<br>3.2.3<br>3.2.3.1<br>3.2.3.2<br>3.2.3.3          | Shift Instructions Register Operations ROP Register Operation Instructions EXTended Register Operation Instructions Inter Level Register Instructions | 3-26<br>3-29<br>3-31<br>3-37<br>3-39 |

| 3.2.4<br>3.2.5<br>3.2.6<br>3.2.6.1<br>3.2.6.2<br>3.2.6.3 | Skip Instructions Argument Instructions Bit Operation Instructions Bit Skip Instructions Bit Setting Instructions One Bit Accumulator Instructions    | 3-41<br>3-44<br>3-46<br>3-47<br>3-48 |

| 3.2.7<br>3.2.7.1<br>3.2.7.2                              | Accumulator Transfer Instructions Transfer to A Register Transfer from A Register                                                                     | 3-49<br>3-51<br>3-51                 |

| 3.3                                                      | Input/Output Control Instructions                                                                                                                     | 3-53                                 |

| 3.3.1<br>3.3.2                                           | Recommended Device Addresses<br>Format of Status and Control Word                                                                                     | 3–53<br>3–57                         |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                  | System Control Instructions Interrupt Control Instructions Memory Management Control Instructions Monitor Call Instruction Wait or Give Up Priority   | 3-58<br>3-58<br>3-61<br>3-62<br>3-63 |

| 3.5                                                      | Customer Specified Instructions                                                                                                                       | 3–64                                 |

| 4                                                        | THE INPUT/OUTPUT SYSTEM                                                                                                                               | 4-1                                  |

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3                           | Input/Output Hardware<br>General Description<br>Input/Output Bus Architecture<br>Vectored Interrupt Identification                                    | 4-1<br>4-1<br>4-3<br>4-3             |

| 4.2<br>4.2.1<br>4.2.2<br>4.2.3                           | Input/Output Programming Programming Examples Input/Output Interrupt Programming Design of an Input/Output Handler Routine                            | 4-4<br>4-4<br>4-5<br>4-5             |

| Section:                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | Page;                                                            |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 5                                                                                                            | THE INTERRUPT SYSTEM                                                                                                                                                                                                                                                                                                                                                        | 5–1                                                              |

| 5.1<br>5.1.1                                                                                                 | Control of Program Levels Program Level Activation                                                                                                                                                                                                                                                                                                                          | 5–2<br>5–4                                                       |

| 5.2<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5<br>5.4.6<br>5.4.7<br>5.4.8<br>5.4.9<br>5.4.10 | Initialization of Interrupt System Interrupt Program Organization Internal Hardware Status Interrupts Monitor Call Interrupt Protect Violation Interrupt Page Fault Interrupt Illegal Instruction Interrupt Error Indicator Interrupt Privileged Instruction Interrupt IOX Error Interrupt Memory Parity Error Interrupt Memory Out of Range Interrupt Power Fail Interrupt | 5-5<br>5-6<br>5-7<br>5-9<br>5-10<br>5-10<br>5-11<br>5-11<br>5-11 |

| 5.5<br>5.5.1<br>5.5.2                                                                                        | Memory Control and Status Error Detection Error Correction Control                                                                                                                                                                                                                                                                                                          | 5—12<br>5—12<br>5—15                                             |

| 5.6                                                                                                          | Vectored Interrupts                                                                                                                                                                                                                                                                                                                                                         | 5–16                                                             |

| 6                                                                                                            | MEMORY MANAGEMENT                                                                                                                                                                                                                                                                                                                                                           | 6–1                                                              |

| 6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3                                                                 | Memory Management Architecture Virtual to Physical Address Mapping Control of Memory Management System Control of Paging Control Registers Control of Page Index Tables Turning the Memory Management System On or Off                                                                                                                                                      | 6-2<br>6-3<br>6-5<br>6-5<br>6-5<br>6-7                           |

| 6.4<br>6.5<br>6.5.1<br>6.5.2                                                                                 | Memory Protection System Ring Protection System Privileged Instructions Paging Status Register                                                                                                                                                                                                                                                                              | 6-8<br>6-10<br>6-11<br>6-12                                      |

| 6.6                                                                                                          | Timing                                                                                                                                                                                                                                                                                                                                                                      | 6—14                                                             |

| 7                                                                                                            | OPERATOR'S PANEL                                                                                                                                                                                                                                                                                                                                                            | 7—1                                                              |

| 7.1<br>7.2<br>7.3                                                                                            | Panel Elements 18-Bit Switch Register 18-Bit Light Emitting Diode Register                                                                                                                                                                                                                                                                                                  | 7–1<br>7–2<br>7–3                                                |

| 7.4<br>7.5                                                                                                   | 16 Selector Push-buttons and 16 Associated Light<br>Emitting Diodes<br>Display Level Select                                                                                                                                                                                                                                                                                 | 7–4<br>7–6                                                       |

| Section:                                                                                       |                                                                                                                                                                                                   | Page:                                                              |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 7.6<br>7.6.1<br>7.6.2<br>7.6.3<br>7.6.4<br>7.6.5<br>7.6.6<br>7.6.7<br>7.6.8<br>7.6.9<br>7.6.10 | Control Buttons Master Clear Restart Load Decode Address Set Address Deposit Enter Register Single Instruction Continue Stop                                                                      | 7-7 7-7 7-7 7-7 7-8 7-8 7-8 7-8 7-9 7-9                            |

| 7.7                                                                                            | Mode Indicators                                                                                                                                                                                   | 7–10                                                               |

| 8                                                                                              | OPERATOR'S COMMUNICATION                                                                                                                                                                          | 8–1                                                                |

| 8.1<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>8.1.5<br>8.1.6<br>8.1.7<br>8.1.8<br>8.1.9<br>8.1.10 | Functions Start a Program Memory Examine Memory Deposit Register Examine Register Deposit Internal Register Examine Internal Register Deposit Current Location Counter Break Function Bank Number | 8-3<br>8-3<br>8-3<br>8-4<br>8-4<br>8-5<br>8-5<br>8-6<br>8-7<br>8-7 |

| 8.2<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5                                               | Bootstrap Loaders Octal Format Load Binary Format Load Mass Storage Load Automatic Load Descriptor Examples                                                                                       | 8-8<br>8-8<br>8-8<br>8-10<br>8-10                                  |

| 9                                                                                              | CACHE MEMORY                                                                                                                                                                                      | 9–1                                                                |

| 9.1<br>9.2<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.2.5                                        | Cache Memory Architecture Cache Memory Access Definitions Cache Addressing Read Access Write Access Cache Inhibit Area                                                                            | 9-2<br>9-4<br>9-4<br>9-4<br>9-4<br>9-5                             |

| Section:                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page:                                                                    |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

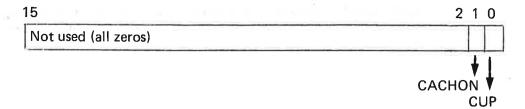

| 9.3<br>9.3.1<br>9.3.2<br>9.3.3                                      | Control of the Cache Memory Setting of Cache Inhibit Limits Cache Initialization Cache Status Register                                                                                                                                                                                                                                                                                                                                                                                                    | 9-6<br>9-6<br>9-6<br>9-7                                                 |

| 9.4                                                                 | Cache Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9–8                                                                      |

| Appendix                                                            | c:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          |

| A                                                                   | NORD-10 Mnemonics and Their Octal Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A-1                                                                      |

| В                                                                   | NORD-10/S Instruction Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | B-1                                                                      |

| Figure:                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | Medium Sized NORD-10/S Computer System NORD-10/S CPU Bus Structure CPU Block Diagram NORD-10/S Two-processor System NORD-10/S Four-processor System Remote LOAD from Master CPU Example of Remote LOAD via Telephone Line and HCLC Protocol Automated TEST System NORD-10/S Bit Numbering Convention Program Level Control                                                                                                                                                                                | 2-1<br>2-4<br>2-5<br>2-9<br>2-10<br>2-11<br>2-12<br>2-13<br>2-14<br>2-20 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                | Schematic Illustration of P-relative Addressing Schematic Illustration of Indirect P-relative Addressing Schematic Illustration of B-relative Addressing Schematic Illustration of Indirect B-relative Addressing Illustration of the Effect of the Stack Code Schematic Illustration of X-re lative Addressing Schematic Illustration of B-relative Indexed Addressing Schematic Illustration of Indirect P-relative Indexed Addressing Schematic Illustration of Indirect B-relative Indexed Addressing | 3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11<br>3-11<br>3-12                 |

| 4.1                                                                 | NORD-10/S Bus System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4–2                                                                      |

| 6.1                                                                 | Virtual to Physical Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-4                                                                      |

#### viii

| Figure:    |                                                   | Page:      |

|------------|---------------------------------------------------|------------|

| 8.1        | Binary Load Format                                | 8–9        |

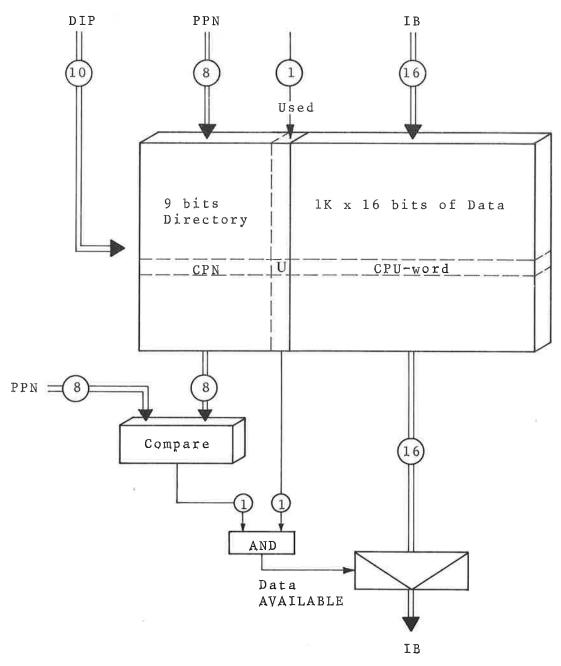

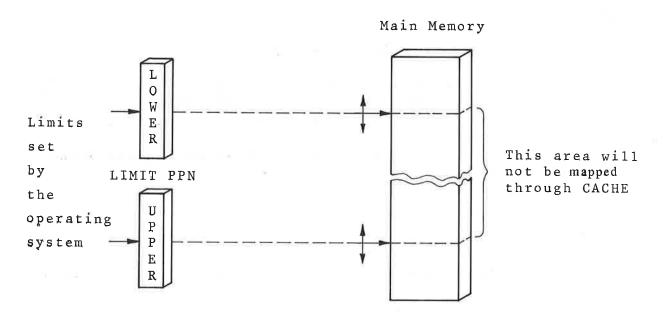

| 9.1<br>9.2 | Cache Memory Organization Cache Limits            | 9–2<br>9–5 |

| Table:     |                                                   | Page:      |

| 3.1        | Addressing Modes                                  | 3–5        |

| 3.2        | The ROP Instruction                               | 3-34       |

| 3.3        | Survey of Registers Controlled by Accumulator     |            |

|            | Transfer Instructions                             | 3-50       |

| 3.4        | Accumulator Transfer Instructions                 | 3-52       |

| 3.5        | Standard Device Addresses for Norsk Data Produced |            |

| 0.0        | Equipment                                         | 3-54       |

| 3.6        | Standard IOX addresses and IDENT codes            | 3–65       |

| 5.1        | Internal Hardware Status Interrupt                | 5-7        |

| 5.2        | Correction Codes                                  | 5–14       |

| 6.1        | Use of Alternate Page Table                       | 66         |

| 8 1        | ALD Setting                                       | 8-12       |

#### 1 INTRODUCTION

#### 1.1 GENERAL CHARACTERISTICS

The NORD-10/S computer system is a medium scale general purpose computer system which, because of the modular design, is actually a family of computer systems.

A basic instruction set is common to all NORD-10/S machines, and this set is highly optimized to produce effective code; hardware floating point arithmetic is standard as are the instructions to manipulate individual bits at high speed.

The register structure and addressing scheme facilitate the processing of structured data with high efficiency.

The NORD-10/S is micro-programmed, and all NORD-10/S instructions are executed by means of a micro-program located in a very fast (65 ns) read-only memory. Micro-programming gives the NORD-10/S computer flexibility and a very large growth potential. New instructions may be added to the NORD-10/S and instructions for special applications may be optimized for a particular use.

The NORD-10/S provides up to 1024 customer-specified instructions. These instructions are micro-programmed in a programmable read-only memory, which is added onto the standard read-only memory.

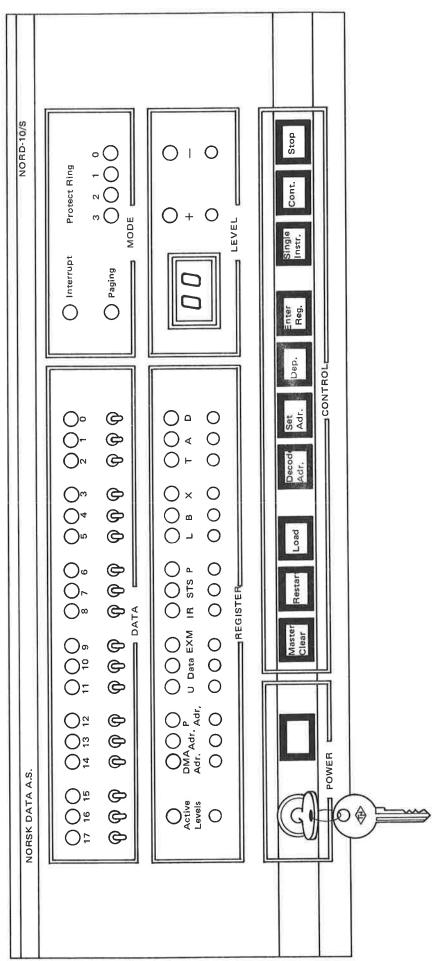

Micro-programming in NORD-10/S is also used to control the operator's panel and to perform operator communication between the operator and the console Teletype or display.

Bootstrap loaders, both for character oriented devices and mass storage devices are also controlled by a micro-program.

The NORD-10/S is designed to be equipped with a wide range of main memories. Memory size may vary from 1K to 256K 16-bit words, and both read-only memories and read/write memories may be used. The speed range is from a high-speed bipolar memory of 100 ns cycle time to core memories, which require 900 ns cycle time.

Standard memory type is MOS semiconductor memory with a cycle time of 400 ns. Parity checking with a parity bit for each byte is standard, while memory error correction with 21 bit memory modules is optional.

As an option, the NORD-10/S CPU may be equipped with 1K words of bipolar cache memory, which significantly increases the CPU performance.

The speed of the NORD-10/S standard processor is 260 ns per micro-instruction, and the NORD-10/S CPU will make efficient use of main memories with a cycle time of 300 ns.

The input/output and interrupt systems of NORD-10/S are designed for ease of use and very high speed. NORD-10/S has 16 program levels each with its own set of registers, making possible a complete context switching from one program level to another in only 1  $\mu$ s. In addition, 2048 priority vectored interrupts are standard, as well as 10 priority internal hardware status interrupts.

As an option, the NORD-10/S may have a Memory Management System which includes a Paging System which performs program relocation, dynamic memory allocation and Ring Protection and Memory Protection Systems.

#### 1.2 PERIPHERAL EQUIPMENT

The range of standard peripherals includes paper tape reader and punch, punched card reader and punch, Teletypes, alphanumeric and graphic displays, sémigraphic colour terminals, line printers, matrix plotters/printers, magnetic tape stations, fixed head drums, disk systems with capacities from 5 to 2000 million bytes, floppy disks, modem controllers including HDLC/SDLC controllers and CAMAC crate controllers.

#### 1.3 SOFTWARE

The standard operating system for NORD-10/S computers is SINTRAN III, which has capabilities for concurrent real-time, batch and time-sharing processes.

- The version of SINTRAN III for machines without mass storage devices is intended for real-time applications in process control and data communication.

- The mass storage version of SINTRAN III includes a general file system with permanent files, scratch files and peripheral device files.

- Subsystems: compilers, text editors, assembler, remote job entry emulators, etc.

For further information, please contact Norsk Data A.S.

#### 2 SYSTEM ARCHITECTURE

#### 2.1 INTRODUCTION

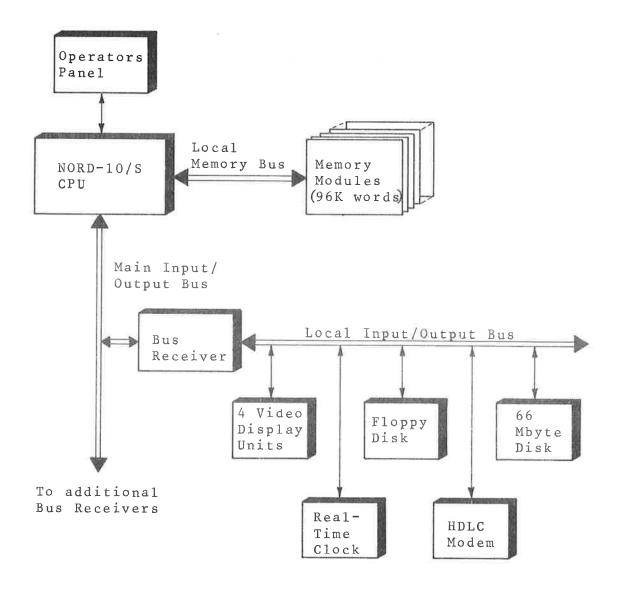

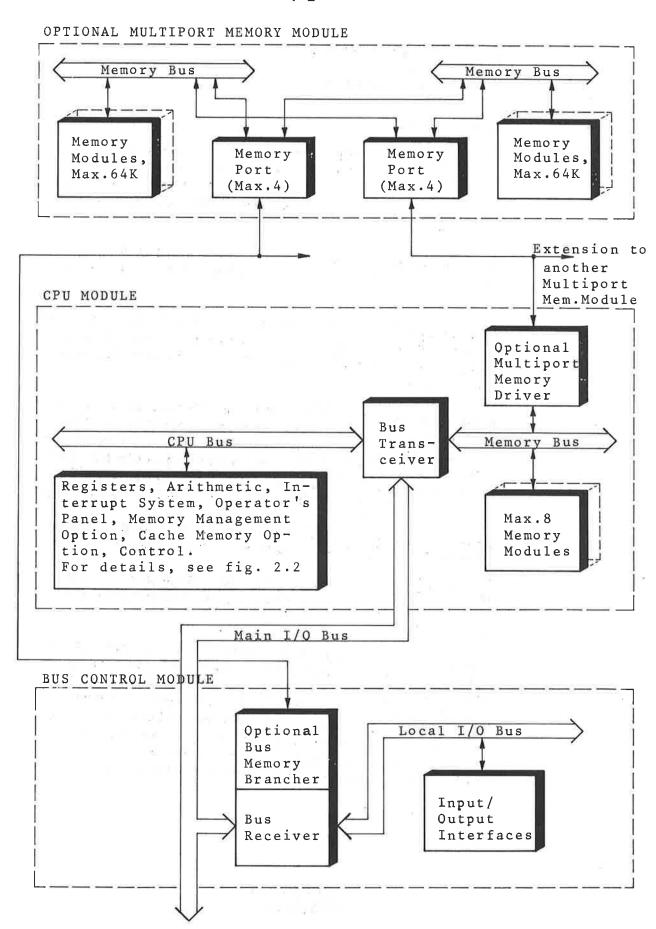

Figure 2.1 shows a typical medium sized NORD-10/S single processor system.

Figure 2.1: Medium Sized NORD-10/S Computer System

In this example, the size of the main memory is 96K 16-bit words, based on 32K MOS semiconductor memory. Details concerning memory flexibility and options are presented in Section 2.3.

Parts of the Input/Output System are shown separated from the rest of the Bus Receiver which efficiently combines flexibility, simplicity and reliability. The Bus Receiver provides the necessary fan out and reduces complexity of device control units. Reliability is increased because errors, in most cases, have only limited consequences on the Local Input/Output Bus.

An important factor in designing the completely modular Input/Output System with all device interfaces made to a common standard, has been the frequent field installations of expanded systems typical to Norsk Data's customers. Interface modules plug directly into prewired positions.

Substantial effort was made to prepare the NORD-10/S for multi-CPU applications and remotely operated installations.

#### 2.2 CENTRAL PROCESSOR

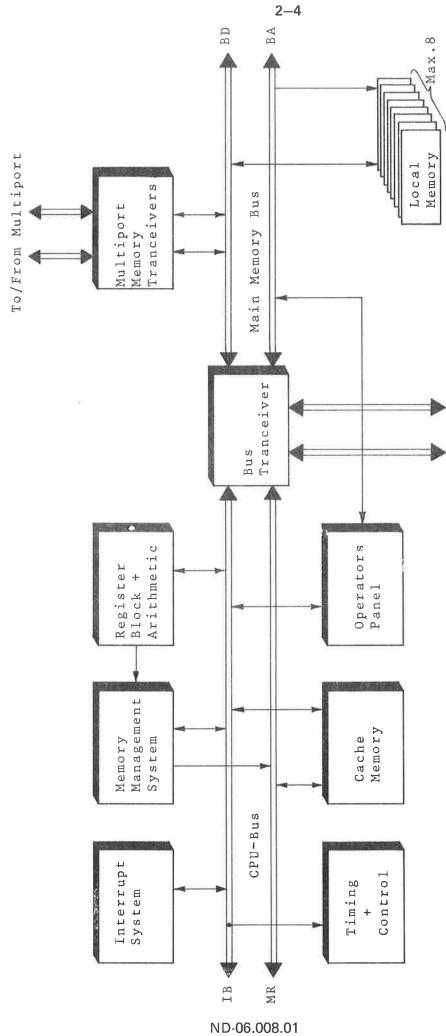

The connection of main modules in the CPU is through the common data bus, IB, and common address bus, MR, as shown in Figure 2.2. For simplicity, control lines and inter-register buses are omitted in this figure.

When the optional Memory Management System is not included, the R-bus is connected directly to the MR-bus.

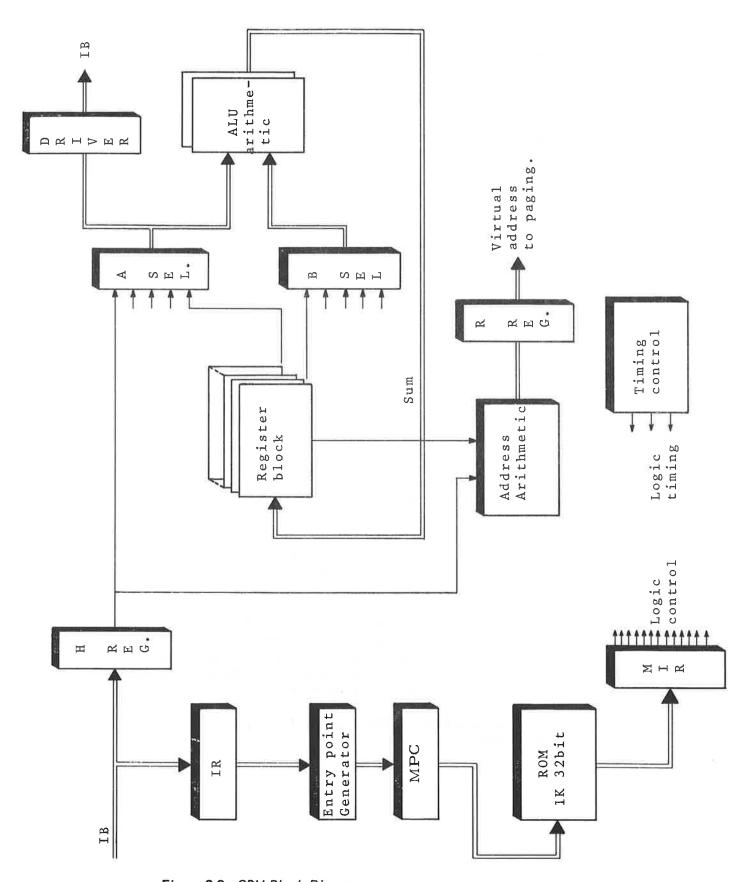

A more detailed diagram of the control section and register block is given in Figure 2.3.

The register block contains 8 general registers for each program level and two scratch registers for each level to be used by the micro-processor.

The arithmetic unit is normally operated in a 16-bit format. The full 32-bit format is used for floating point and double precision operations. The arithmetic unit contains the necessary buffer registers to do the complete inner loop in the floating point micro-programs using only 260 ns.

Some instructions in the NORD-10/S instruction set are general two-address inter-register instructions. Due to the generality of these instructions, 2048 inter-register instructions (see Section 3.2.3) are converted directly to the three-address format of the micro-instruction and fed directly into the micro-instruction register. The remaining bits, i.e., cycle control, etc. are read from the read-only memory.

Figure 2.2: NORD-10/S CPU Bus Structure

MA

MD

Figure 2.3: CPU Block Diagram

#### 2.2.1 Register Block

There are 16 register sets in NORD-10/S, one for each of 16 program levels. Each of the register sets consists of 8 general programmable registers. There is a total of 128 general registers, referred to as the register block.

The 8 general registers are:

Status register: This register holds the indicators described in

Section 2.2.2.

A register: This is the main register for arithmetic and logical

operations directly with operands in memory.

This register is also used for input/output com-

munication.

D register: This register is an extension of the A register

in double precision or floating point operations. It may be connected to the A register during

double length shifts.

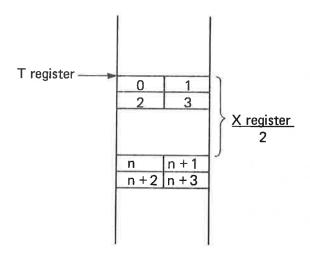

T register: Temporary register. In floating point instruc-

tions it is used to hold the exponent part.

L register: Link register. The return address after a sub-

routine jump is contained in this register.

X register: Index register. In connection with indirect

addressing it causes post-indexing.

B register: Base register or second index register. In con-

nection with indirect addressing, it causes

pre-indexing.

P register: Program counter, address of current instruction.

This register is controlled automatically in the normal sequencing or branching mode. But it is also fully program controlled and its contents may be transferred to or from other registers.

Two instructions, ROP and SKP, may specify a register whose content is always zero.

#### 2.2.2 Indicators

Eight indicators are accessible by program. These 8 indicators are:

- C Carry indicator. The carry indicator is dynamic.

- Q Dynamic overflow indicator.

- O Static overflow indicator. This indicator remains set after an overflow condition until it is reset by program.

- Z Error indicator. This indicator is static and remains set until it is reset by program. The Z indicator may be internally connected to an interrupt level such that an error message routine may be triggered.

- K One bit accumulator. This indicator is used by the BOP bit operations, instructions operating on one-bit data.

- TG Rounding indicator for floating point operations.

- M Multi-shift link indicator. This indicator is used as temporary storage for discarded bits in shift instructions in order to ease the shifting of multiple precision words.

- PTM Page table modus. Enables use of the alternate page table.

These 8 indicators are fully program controlled either by means of the BOP instructions or by the TRA or TRR instructions where all indicators may be transferred to and from the A register.

#### 2.3 MEMORY CONFIGURATIONS

The NORD-10/S CPU main frame has eight general slots for memory modules, and two slots reserved for optional multiport memory interface buffers.

The following standard memory modules are available at printing time for direct connection into each of the eight slots:

8K by 18 bits, 300 ns access time 8K by 21 bits, 300 ns access time 32K by 18 bits, 350 ns access time 32K by 21 bits, 350 ns access time 32K by 18 bits, 300 ns access time 32K by 21 bits, 300 ns access time

Memory modules with 18 bits word length provide one parity bit per byte, while 21 bit modules are used for memory error correction. Maximum memory size addressable from one CPU is 256K words.

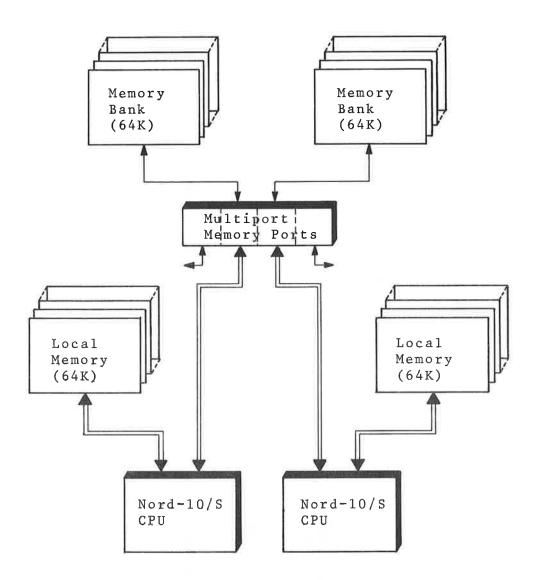

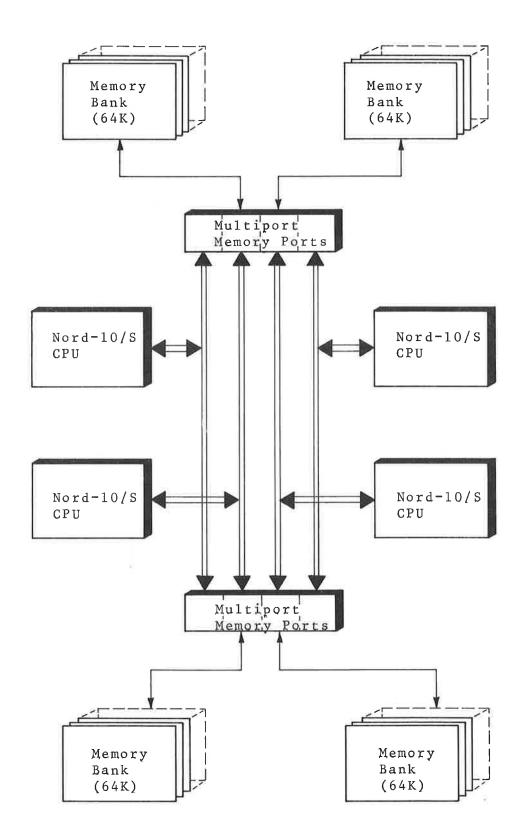

The NORD-10/S multi-processor system is shown in Figure 2.4.

Common main memory is connected via the multiport memory interface unit, which is capable of handling requests from both CPU's in parallel if they do not address the same 64K module. The "local" 64K modules shown in the figure may, of course, be omitted; they are shown to demonstrate the flexibility of the system.

The connection of Input/Output devices and mass storage units in a multi-processor system is described in Chapter 4.

The total capacity of the dual memory interface is four independent channels as shown in Figure 2.5.

The memory access priority for the CPU's is normally allocated in a different order for each 64K unit.

By omitting three of the CPU's in Figure 2.5, we obtain a one-processor system with a maximum memory configuration of 256K.

Figure 2.4: NORD-10/S Two-processor System

Figure 2.5: NORD-10/S Four-processor System

#### 2.4 REMOTE OPERATION

Several facilities for the remote operation of the NORD-10/S are available. Remote operation here means one NORD-10/S being controlled by another NORD-10/S. In some cases, the two machines may be in the same room, or they are connected over telephone lines using low or high speed modem.

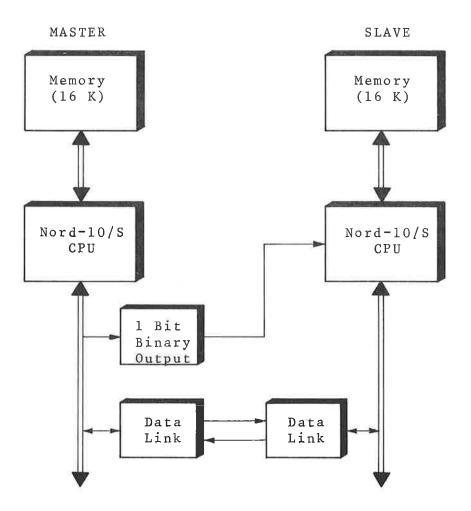

The simplest form of remote operation is shown in Figure 2.6.

Figure 2.6: Remote LOAD from Master CPU

In this case, the automatic LOAD function built into the microprogrammed control unit of all NORD-10/S CPU's is used to start reading data via the data link. The LOAD function is described in Section 8.2.

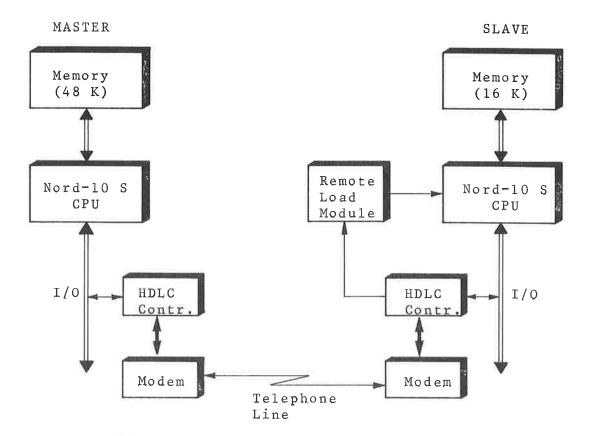

Figure 2.7: Example of Remote LOAD via Telephone Line and HDLC Protocol

In the example shown in Figure 2.7, the SLAVE computer is equipped with a Remote Load Module, which decodes a special "Remote Load Trigger" frame sent by the MASTER Computer, thus, activating a load micro-program in the slave. A remote load operation may be initiated both by the MASTER computer and by an operator at the SLAVE computer site.

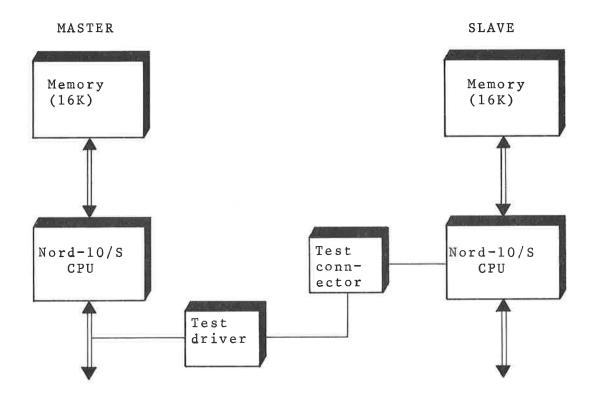

A closer control of the slave computer is obtained by using the test connector developed for automatic debugging of CPU and microprocessor. This system is shown in Figure 2.8.

In the automated TEST system, the operator's panel connections of the slave computer are replaced by a TEST connector, which is controlled by a special interface in the master computer. The master CPU thereby obtains direct control of buses and micro-processor in the slave computer. This may be used for automatic checkout, diagnostics, and microprogram debugging.

Figure 2.8: Automated TEST System

#### 2.5 INSTRUCTION AND DATA FORMATS

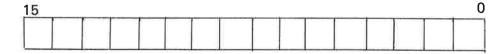

The NORD-10/S has a 16-bit word format. The bits are conventionally numbered 0 to 15 with the most significant bit numbered 15 and the least significant bit numbered 0.

16-bit NORD-10/S word

Figure 2.9: NORD-10/S Bit Numbering Convention

The content of a NORD-10/S word is conventionally represented by a 6-digit octal number. Thus, the content of a word with all 16 bits set to zero is represented as 000000, while the contents of a word with all bits set to one is represented as 177777.

#### 2.5.1 Instruction Formats

All NORD-10/S instructions are contained in one single 16-bit word.

The instruction set is divided into the following five subclasses:

- Memory Reference Instructions

- Operate Instructions

- Input/Output Control Instructions

- System Control Instructions

- Customer Specified Instructions

In Chapter 3, each instruction is given a short description. This includes a diagram showing the instruction format.

#### 2.5.2 Data Formats

The standard NORD-10/S instruction set provides instructions for the following six different data formats:

- 1. Single bit

- 2. 8-bit byte

- 3. 16-bit word

- 4. 32-bit double word

- 5. 48-bit floating point word

- 6. 32-bit floating point word (optional, instead of 48-bit floating point)

#### 2.5.2.1 Single Bit

A single bit data word is typically used for a logical variable; the bit instructions (see Section 3.2.6) are used for manipulation of single bit variables. The bit instructions specify operations on any bit in any of the general registers, as well as the accumulator indicator K.

#### 2.5.2.2 8-Bit Byte

Two instructions are available in the standard NORD-10/S instruction set for byte manipulations, i.e., load byte and store byte (see Section 3.1.6).

A byte consists of 8 bits, giving a range of  $0 \le X \le 255$ .

The byte addressing (see Section 3.1.6) is such that when two bytes are packed into a word, the even byte address points to the left half of the word.

| 15           | 8 7         | 0 |

|--------------|-------------|---|

| Even address | Odd address |   |

| n            | n + 1       |   |

Byte Format

#### 2.5.2.3 16-Bit Word

The most common data word format is the 16-bit word contained in one memory location or one register.

Representation of negative numbers is in 2's complement. The skip instruction (see Section 3.2.4) also contains instructions to treat numbers as unsigned (magnitude) numbers.

Range

or

$$0 \le X \le 65535$$

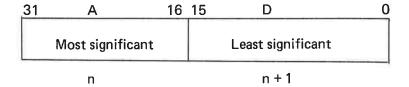

#### **2.5.2.4** 32-Bit Double Word

Two instructions are available to handle double word formats, load double and store double (see Sections 3.1.2 and 3.1.3).

A double word is a 32-bit number which occupies two consecutive locations (n, n + 1) in memory, and where negative numbers are in 2's complement.

#### **Double Word Format**

A double word is always referred to by the address of its most significant part. Normally, a double word is transferred to the registers so that the most significant part is contained in the A register and the least significant in the D register. Range as integers:

$$-2$$

147 483 648  $\leq$  X  $\leq$  2 147 483 647

#### 2.5.2.5 48-Bit Floating Point Word

The standard NORD-10/S instruction set provides full floating point hardware arithmetic instructions, load floating, store floating, add, subtract, multiply, and divide floating, convert floating to integer, and convert integer to floating.

The data format of floating point words is of 32 bits mantissa magnitude, one bit for sign and 15 bits for a biased exponent.

The mantissa is always normalized,  $0.5 \le \text{mantissa} < 1$ . The exponent base is 2, the exponent is biased with  $2^{14}$ . A standarized floating zero contains zero in all 48 bits.

In main memory, one floating point data word occupies three 16-bit core locations, which are addressed by the address of the exponent part.

- n exponent and sign

- n + 1 most significant part of mantissa

- n + 2 least significant part of mantissa

In CPU registers, bits 0-15 of the mantissa are in the D register, bits 16-31 in the A register and bits 32-47, exponent and sign, in the T register. These three registers together are defined as the floating accumulator.

#### Floating Word Format

The accuracy is 32 bits or approximately 10 decimal digits; any integer up to  $2^{32}$  has an exact floating point representation.

The range is

$$2^{-16384} \cdot 0.5 \le X < 2^{16383} \cdot 1 \text{ or } X = 0$$

or

$$10^{-4920} < X < 10^{4920}$$

#### Examples (octal format):

|     | Т      | Α      | D |

|-----|--------|--------|---|

| 0:  | 0      | 0      | 0 |

| +1: | 040001 | 100000 | 0 |

| -1: | 140001 | 100000 | 0 |

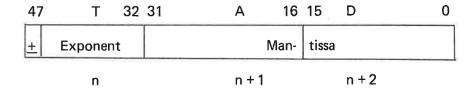

#### 2.5.2.6 32-bit Floating Point Word

As an option, the NORD-10/S may be equipped with microprogram for 32-bit floating point format instead of the standard 48-bit format described in Section 2.5.2.5. The instructions affected are:

| FAD | Floating Point Add                |

|-----|-----------------------------------|

| FSB | Floating Point Subtract           |

| FMU | Floating Point Multiply           |

| FDV | Floating Point Divide             |

| NLZ | Convert Integer to Floating Point |

| DNZ | Convert Floating Point to Integer |

The data format of 32-bit floating point words is of 23 bits mantissa magnitude, one bit for sign and 9 bits for a biased exponent. These 33 bits are packed in two 16-bit words by omitting the most significant bit of the mantissa, which is always a one in non-zero numbers.

The mantissa is always normalized,  $0.5 \le \text{mantissa} \le 1$ . The exponent base is 2, the exponent is biased with  $2^8$ .

A standarized floating zero contains zero in all 32 bits.

In main memory, one 32-bit floating point data word occupies two 16-bit memory locations, which are addressed by the address of the exponent part.

n exponent, sign and mantissa bits 16-21 n + 1 mantissa bits 0-15

In CPU registers, bits 0-15 of the mantissa are in the D register, bits 16-21 and exponent and sign are in the A register. These two registers together are defined as the 32-bit floating accumulator. The T register is not affected by 32-bit Floating Point operations.

| 31 | 30      | Α | 22 21 | 16   | 15    | D     | 0 |

|----|---------|---|-------|------|-------|-------|---|

| +  | Exponen |   |       | Man- | tissa |       |   |

|    |         | n |       |      |       | n + 1 |   |

#### 32-bit Floating Point Word Format

The accuracy is 23 bits or appoximately 7 decimal digits. Any integer up to  $2^{23}$  has an exact floating point representation.

The range is

$$2^{-256} \cdot 0.5 \le X < 2^{255} \cdot 1 \text{ or } X = 0$$

or

$$10^{-76} < x < 10^{76}$$

#### Examples (octal format):

|              | A      | D |

|--------------|--------|---|

| 0:           | 0      | 0 |

| +1.0:        | 040100 | 0 |

| <b>-1.0:</b> | 140100 | 0 |

| +3.0:        | 040240 | 0 |

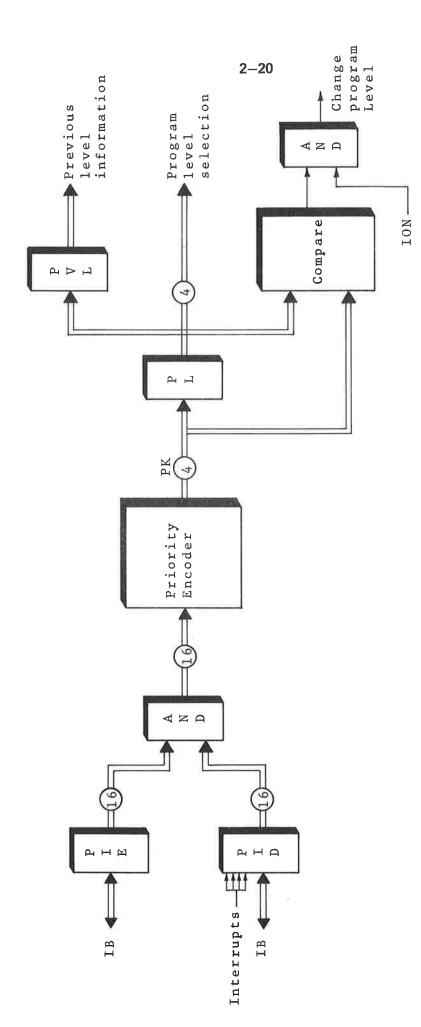

#### 2.6 INTERRUPT SYSTEM

The NORD-10/S Interrupt System allows priority interrupt handling at extremely high speed. The interrupt system consists of 16 program levels in hardware, each program level with its own complete set of general registers and status indicators. The program levels are numbered from 0 to 15 with increasing priority; program level 15 has the highest priority, program level 0 has the lowest. The context switching from one program level to another is completely automatic and requires only 1  $\mu$ s.

All program levels can be activated by program. In addition, program levels 10-13 and 15 can be activated by external devices and program level 14 by CPU internal hardware status interrupts.

As many as 2048 vectored interrupts may be connected.

By using these program levels, large programming systems may be greatly simplified. Independent tasks may be organized at different program levels with all priority decisions determined by hardware and with almost no overhead because of the rapid context switching.

The program level to run is controlled from the two 16-bit registers:

PIE Priority Interrupt Enable

PID Priority Interrupt Detect

Each program level is controlled by the corresponding bits in these registers. The PIE register is program controlled and the PID register is controlled by both program and vectored interrupts.

At any time, the highest program level, which has its corresponding bits set in both PIE and PID is running. This level is called PL.

A change from a lower to a higher program level is caused by an interrupt request. A change from a higher program level to a lower takes place when the program on the higher program level gives up its priority.

Figure 2.10: Program Level Control

ND-06.008.01

#### 2.7 MEMORY MANAGEMENT SYSTEM

The Memory Management System is designed to extend the NORD-10/S's physical address space to provide a virtual memory and to provide a sophisticated memory and privileged instruction protection system.

The basic parts of the system are the:

- Paging System

- Memory Protection System

- Ring Protection System

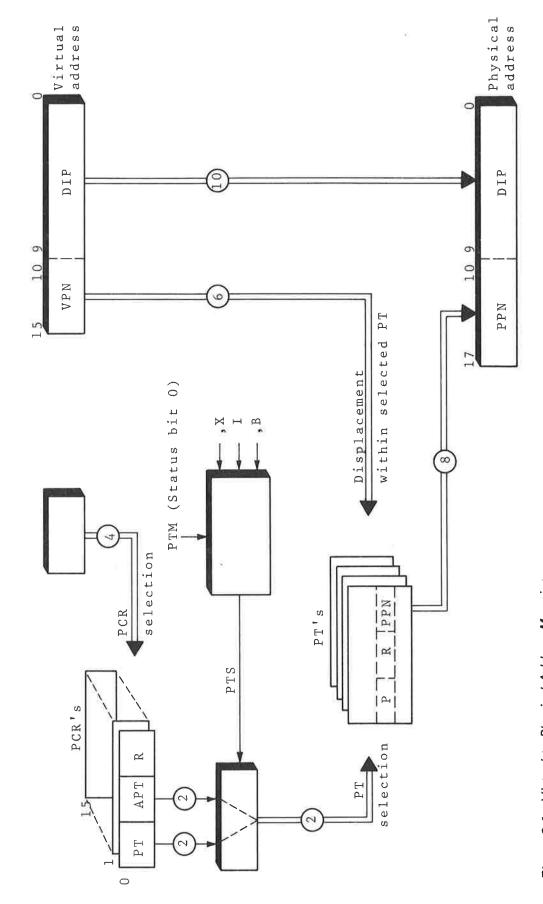

The Paging System is an automatic address interpretation system which maps a 16-bit virtual address, as seen from the program, into an 18-bit physical address. This implies that the maximum memory size may be extended from 64K words to 256K words. The system also allows programs to be written for 64K virtual memory with only parts of the program residing in physical memory at a given time, the rest being kept on mass storage.

The Paging System divides the memory into memory blocks or pages of 1024 words or 1K words. The pointers to these pages are found in the page-index-tables. In NORD-10/S there are four page-index-tables each consisting of 64 words, which each yield a full 64K address space. The tables are kept in high-speed registers with 16 bits word length.

Two independent protection systems are also included in the Memory Management System: the Memory Protection System and the Ring Protection System.

The Memory Protection System is a protection system for each individual page of memory. Each individual page may be protected against:

- read accesses

- write accesses

- instructions fetch accesses

and any combination of these. Thus, there are eight modes of memory protection for each page.

The Ring Protection System is a combined privileged instruction and inter-page memory protection system. The system divides the pages into four classes called rings: ring 0, ring 1, ring 2 and ring 3. Ring 3 is called the highest ring and ring 0 the lowest ring. A program located on a particular page is said to run on the ring the page belongs to. Programs running on ring 2 and ring 3 may use the whole NORD-10/S's instruction repertoire while programs running on ring 0 and 1 may only operate on a restricted instruction set.

The inter-page protection feature allows programs on a high ring to access pages on a lower ring while programs on a lower ring are not permitted to access pages on a higher ring. If a prohibited ring access or privileged instruction execution is attempted, the illegal operation will not proceed and an internal hardware status interrupt will occur to indicate an error.

This Ring Protection System will protect large programming systems against illegal operations by allowing independent tasks to be placed on different rings. The recommended way of organizing a system is as follows:

Ring 0: User programs

Ring 1: Compilers, assembler Ring 2: Operating systems

Ring 3: Kernel of operating systems

One should note that the two protection systems are independent of each other and that both the individual memory protection mode and the ring mode must be satisfied before an operation is performed. For example, if a program PROG tries to read from page P belonging to ring 2, then PROG must be running on ring 2 or 3 and page P's individual memory protection mode must allow P to be read.

#### 3 INSTRUCTION REPERTOIRE

In the NORD-10/S all instructions occupy a single word, 16 bits, yielding a very efficient user of memory and also producing code with unusual efficiency with regard to speed. Floating point arithmetic operations and floating/integer conversions are standard.

Note that in this chapter one is always referring to the register set on the current program level, for example, "the A register" means "the A register on current program level".

In this manual, the instruction set of NORD-10/S is divided into the following five subclasses:

- Memory Reference Instructions

- Operate Instructions

- Input/Output Control Instructions

- System Control Instructions

- Customer Specified Instructions

Each instruction is given a short description. This includes its mnemonic as used in the assembly language, octal code, a diagram showing its format, timing information and special comments. For each instruction, the systems and indicators that can be affected by the instruction are listed.

The definitions used in the descriptions are as follows:

#### **General Registers:**

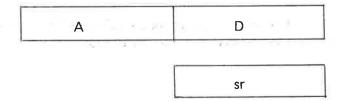

- A A register

- D D register

- T T register

- L L register

- X X register

- B B register

- P Program counter

STS Status register containing PTM, TG, K, Z, Q, O, C, M

# Status Word:

# Bit

| 0   | PTM  | Page table mode                                  |

|-----|------|--------------------------------------------------|

| 1   | TG   | Rounding indicator for floating point operations |

| 2   | K    | One bit accumulator                              |

| 3   | Z    | Error indicator                                  |

| 4   | Q    | Dynamic overflow indicator                       |

| 5   | 0    | Static overflow indicator                        |

| 6   | C    | Carry indicator                                  |

| 7   | M    | Multi-shift link indicator                       |

| 8-1 | 1 PL | Program level indicator                          |

| 14  | PONI | Memory Management On indicator                   |

| 15  | IONI | Interrupt System On indicator                    |

#### Internal Registers:

| STS              | Status word (see above)           |

|------------------|-----------------------------------|

| OPR              | Operator's panel                  |

| LMP              | Lamp register                     |

| PGS              | Paging status register            |

| PCR <sup>-</sup> | Paging control register           |

| PVL              | Previous level register           |

| IIC              | Internal interrupt code           |

| IIE              | Internal interrupt enable         |

| PID              | Priority interrupt detect         |

| PIE              | Priority interrupt enable         |

| ALD              | Automatic load descriptor         |

| PES              | Memory error register             |

| IR               | Instruction register              |

| PEA              | Memory error address              |

| CILR             | Cache inhibit limits register     |

| ECCR             | Error correction control register |

| CCLR             | Clear cache                       |

|                  |                                   |

# Abbreviations:

| EL | Effective location   |

|----|----------------------|

| EW | Effective word       |

| AD | Double accumulator   |

| FA | Floating accumulator |

| DW | Double word          |

| FW | Floating word        |

| sr | source register      |

| dr | destination register |

| ٨  | Logical AND          |

| V  | Logical inclusive OR |

| V  | Logical exclusive OR |

| () | The contents of      |

| μs | Microsecond          |

| ns | Nanosecond           |

|    |                      |

ND-06.008.01 Revision A The NORD-10 instructions are controlled from a micro-processor which takes its instructions from a high speed bipolar read-only memory (cycle time - 65 ns).

The execution time of a NORD-10/S instruction is primarily given by the number of micro instructions and the speed of the main memory.

The NORD-10 may efficiently utilize memories of different type and speed. It will make full use of a bipolar TTL memory and may also run with , for example, a slow core memory.

With the cache memory option, one is able to obtain a speed nearly as fast as that of a bipolar TTL memory.

The instruction times given in Chapter 3 are as measured from a program running on a standard NORD-10/S with all references in cache memory.

If this is not the actual case, the following changes should be made:

For indirect addressing add 0.45  $\mu$ s.

For each read reference to Local Memory add 0.45  $\mu$ s.

For each write reference to Local Memory add 0  $\mu$ s.

For each read reference to Multiport Memory via 0.5 m cable add 0.85  $\mu$ s.

For each write reference to Multiport Memory via 0.5 m cable add 0.35  $\mu s$ .

#### 3.1 MEMORY REFERENCE INSTRUCTIONS

Memory reference instructions specify operations in words in memory. For all the memory reference instructions in NORD-10/S, the addressing mode is the same, with the exception of the conditional jump, the byte and the register block instructions. The addressing structure for these memory reference instructions is given under the specific instruction specification.

The NORD-10/S has the following groups of memory references instructions:

- Store Instructions

- Load Instructions

- Arithmetic and Logical Instructions

- Sequencing Instructions

- Byte Instructions

- Register Block Instructions

### 3.1.1 Addressing Structure

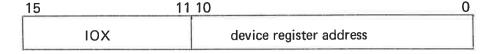

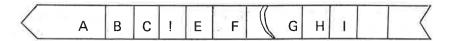

In memory reference instruction words, 11 bits are used to specify the address of the desired word(s) in memory, 3 address mode bits and an 8-bit signed displacement using 2's complement for negative numbers and sign extension. (Note that excluded from this is the conditional jump, the byte and the register block instructions.)

| 15     | 11 10 | 9 | 8  | 7 |              | 0 |

|--------|-------|---|----|---|--------------|---|

| op. co | de ,X | 1 | ,В |   | displacement |   |

NORD-10/S uses a relative addressing system, which means that the address is specified relative to the contents of the program counter or relative to the contents of the B and/or X registers.

The three addressing mode bits called ",X", "I" and ",B" provide eight different addressing modes.

The addressing mode bits have the following meaning:

- The I bit specifies indirect addressing.

- The ,B bit specifies address relative to the contents of the B register, pre-indexing. The indexing by ,B takes place before a possible indirect addressing.

The ,X bit specifies address relative to the contents of the X register post-indexing. The indexing by ,X takes place after a possible indirect addressing.

If all the ,X, I and ,B bits are zero, the normal relative addressing mode is specified. The effective address is equal to the contents of the program counter plus the displacement, (P) + disp.

The displacement may consist of a number ranging from -128 to +127. Therefore, this addressing mode gives a dynamic range for directly addressing 128 locations backwards and 127 locations forwards.

Generally, a memory reference instruction will have the form:

<operation code> <addressing mode> <displacement>

Note that there is no addition in execution time for relative addressing, pre-indexing, post-indexing or both. Indirect addressing, however, adds one extra memory cycle to the listed execution time.

The address computation is summarized in Table 3.1. The symbols used are defined as follows:

| ,X    | Bit 10 of the instruction                              |

|-------|--------------------------------------------------------|

| 1     | Bit 9 of the instruction                               |

| ,B    | Bit 8 of the instruction                               |

| disp. | Contents of bits 0-7 of the instruction (displacement) |

| (X)   | Contents of the X register                             |

| (B)   | Contents of the B register                             |

| (P)   | Contents of the P register                             |

| ()    | Means contents of the register or word                 |

The effective address is the address of that memory location which is finally accessed after all address modifications (pre- and post-indexing) have taken place in the memory address computation.

| ,X | 1 | ,В | Mnemonic | Effective Address   |

|----|---|----|----------|---------------------|

| 0  | 0 | 0  |          | (P) + disp.         |

| 0  | 1 | 0  | 1        | ((P) + disp.)       |

| 0  | 0 | 1  | ,B       | (B) + disp.         |

| 0  | 1 | 1  | ,B I     | ((B) + disp.)       |

| 1  | 0 | 0  | ,X       | (X) + disp.         |

| 1  | 0 | 1  | ,B ,X    | (B) + disp. + (X)   |

| 1  | 1 | 0  | Ι ,Χ     | ((P) + disp.) + (X) |

| 1  | 1 | 1  | ,В I ,Х  | ((B) + disp.) + (X) |

Table 3.1: Addressing Modes

Wise and competent use of the NORD-10/S addressing modes will result in efficient programs. Advanced readers may wish to skip the rest of this section after perusing Table 3.1, which summarizes the addressing structure.

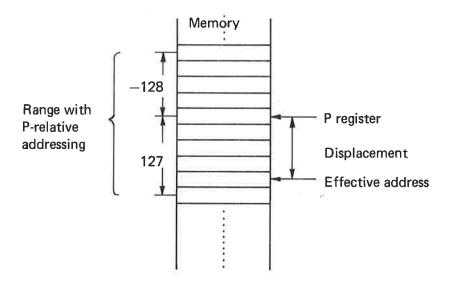

### P-relative Addressing ,X=0 I=0 ,B=0

The *P-relative* addressing mode is specified by setting the ,X, I and ,B bits all to zero. In this mode, the displacement bits (bits 0-7) specify a positive or negative 7-bit address relative to the current value of the program counter (P register).

#### Example:

Suppose memory location 403 contains the instruction 004002, which in this chapter we shall represent by STA \* 2, and this instruction is executed. The ,X, I and ,B bits are all set to zero indicating P-relative addressing and a positive displacement of 2 is given; the contents of the A register will therefore be stored in memory location 405. If, instead, location 403 contains the instruction JMP \* -2 and it is executed, the next instruction to be executed will be taken from location 401. While there is an obvious limitation to this mode of addressing (locations more than 1288 words away from the instruction being executed cannot be accessed), this mode of addressing is still quite useful for doing local jumps and accessing nearby constants and variables.

Figure 3.1: Schematic Illustration of P-relative Addressing

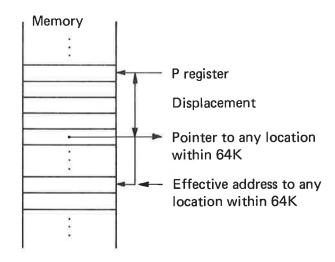

### Indirect P-relative Addressing ,X=0 I=1 ,B=0

Since one must be able to access memory locations more than 128<sub>10</sub> words away from the instruction being executed, the simplest method of doing this is to use the *indirect P-relative* addressing mode, specified by setting the I bit to one and the ,X bit and ,B bit to zero in memory address instructions. In this mode an address relative to program counter is computed, exactly as for P-relative addressing, by adding the displacement to the value of the program counter, but rather than the addressed location actually being accessed, the contents of the addressed location are used as a 16-bit address of a memory location which is accessed instead.

### Example:

Suppose location 405 contains the instruction LDA I \* 2 (045002<sub>8</sub>) and that this instruction is executed. Let us also suppose memory location 16003 contains the value 17 and that memory location 407 contains 016003. The net result of executing the instruction in location 405 is to load the value 17 into the A register. First the displacement 2 of the LDA instruction is added to the value of the location counter 405, giving the result 407; then the contents of location 407, 16003 are used as an address and the contents of this address 17 are finally loaded into the A register.

Figure 3.2: Schematic Illustration of Indirect P-relative Addressing

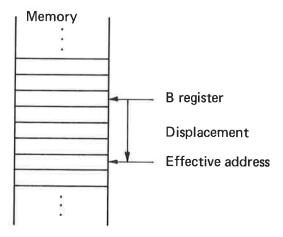

### B-relative Addressing ,X=0 I=0 ,B=1

The above two addressing modes are quite sufficient, in fact, theoretically, either one alone is sufficient. However, if the NORD-10/S provided only one or both of the two addressing modes already described, it would not be particularly convenient for program efficiency. For instance, suppose that two subprograms, each a couple of hundred words long, need to communicate. Within each subprogram memory accesses are commonly made using P-relative addressing or occasionally, indirect P-relative addressing. But between the subprograms indirect P-relative addressing would have to be used almost exclusively since, in general, locations in one subprogram, which instruction in the other subprogram must access, will not be less than 128 words apart. But this is very inefficient since both subprograms must contain indirect pointers to data and instructions local to the other subprogram.

To overcome this difficulty another addressing mode is available *B-relative* addressing, which permits both subprograms to directly address a common data area. B register relative addressing is specified by setting the ,X and I bits to zero and the ,B bit to one in memory address instructions. This addressing mode is quite closely related to P-relative addressing, but instead the displacement is added to the current value of the B register, the resultant sum is used to specify the memory location accessed.

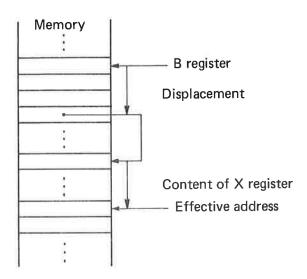

Figure 3.3: Schematic Illustration of B-relative Addressing

#### Example:

Let location 405 contain the instruction LDA -4, B (044774g) and the B register contains the value 10035. Execute the instruction in location 405. This causes the contents of location 10031 to be loaded into the A register. The minus 4 in the displacement field of the LDA instruction in location 405 is added to the contents of the B register, 10035, giving a sum of 10031, and the contents of location 10031 are loaded into the A register.

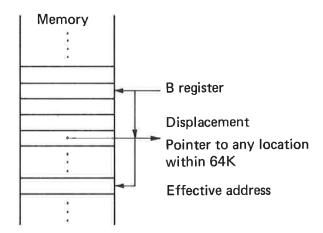

# Indirect B-relative Addressing ,X=0 I=1 ,B=1

Naturally, there is also an indirect B-relative addressing mode which is specified by setting the ,B and I bits to one and the ,X bit to zero in memory reference instructions. This mode has the same relationship to B-relative addressing that indirect P-relative addressing has to P-relative addressing. This permits a subprogram to access data or locations in other subprograms indirectly via pointers in an area common to several subprograms. This address mode is used extensively for calling library routines.

#### Example:

Let location 10031 contain the instruction JPL I 3 ,B (135403<sub>8</sub>) and the B register contain 400, a pointer to an area common to several subprograms. Furthermore, let location 403 contain the value 2000. If the instruction in location 10031 is executed, the subroutine beginning at location 2000 will be called. The displacement, 3, in the JPL instruction is added to the contents of the B register, 400, giving a result of 403. The contents of location 403, 2000, are then used as a pointer to the subroutine.

Figure 3.4: Schematic Illustration of Indirect B-relative Addressing

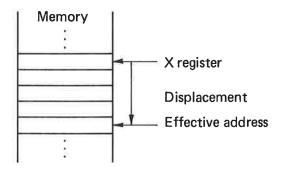

### X-relative (or indexed) Addressing ,X=1 I=0 B=0

The other four addressing modes all involve use of the X register. The simplest of these is *X-relative* addressing which works like P- and B-relative addressing, but the displacement is added to the X register's contents during the address calculation instead of to the contents of the P or B register. This addressing mode is often used for randomly accessing the elements of a block of data.

#### Example:

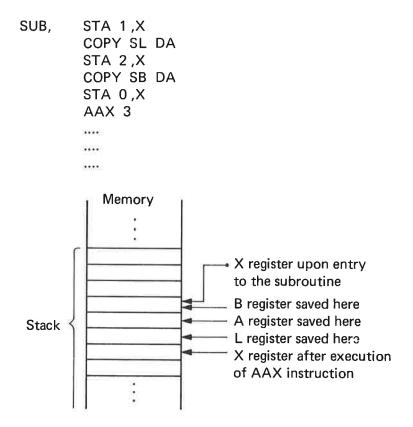

Let a recursive subroutine, when being called, save the contents of the L, A and B registers in a three word block on a push down stack, and the X register point to the first free register in the stack. The following code might then be found at the beginning of the recursive subroutine:

Figure 3.5: Illustration of the Effect of the Stack Code.

For another example reread B-relative addressing, substituting "X register" for "B register".

Figure 3.6: Schematic Illustration of X-relative Addressing

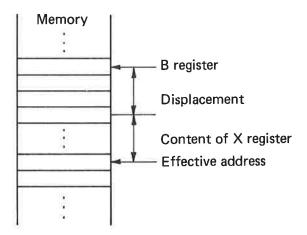

# B-relative Indexed Addressing ,X=1 I=0 ,B=1

When the ,X and ,B bits are set to one and the I bit to zero in memory reference instructions, the mode is called *B-relative indexed* addressing. In this mode, the contents of the X and B registers and the displacement are all added together to form the effective address.

B-relative indexed addressing is often very useful, for instance, when accessing row by row elements of a two-dimensional array stored column by column.

Figure 3.7: Schematic Illustration of B-relative Indexed Addressing

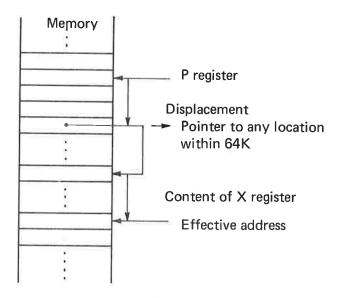

# Indirect P-relative Indexed Addressing ,X=1 I=1 ,B=0

The last two addressing modes are difficult to describe, but very useful. Indirect P-relative indexed addressing is selected by setting the ,X and I bits to one and the ,B bit to zero in the memory address instruction. This mode allows successive elements of an array arbitrarily placed in memory to be accessed in a convenient manner.

The address calculation in the mode takes place as follows. The contents of the P register, say 4002, are added to the displacement, say -1, and produce a sum, 4001. The contents of the location 4001, say 10100, are added to the contents of the X register, say -100, to produce a new sum, 10000, the effective address. By incrementing the X register, successive locations may be accessed. For instance, using the above example, locations 10000 through 10100 can be successively accessed by stepping the contents of the X register from -100 to zero.

Readers are advised to go over this example carefully. Stepping through an array in this fashion is done very often.

Figure 3.8: Schematic Illustration of Indirect P-relative Indexed Addressing

#### Indirect B-relative Indexed Addressing ,X=1 I=1 ,B=1

The final addressing mode, *indirect B-relative indexed* addressing, is identifical to indirect P-relative indexed addressing except that the contents of the B register are used instead of the contents of the P register in the effective address computation. This mode can therefore be used to step through arrays pointed to from a data area common to several subprograms.

Figure 3.9. Schematic Illustration of Indirect B-relative Indexed Addressing

### 3.1.2 Store Instructions

STZ Store zero Code: 000 000

Format: STX <address mode> <disp.>

The effective location is cleared.

Affected: (EL) Time:  $1.3 \mu s$

STA Store A register Code: 004 000

Format: STA <address mode> <disp.>

The contents of the A register are stored

in the effective location.

Affected: (EL) Time:  $1.3 \mu s$

STT Store T register Code: 010 000

Format: STT <address mode> <disp.>

The contents of the T register are stored in the

effective location.

Affected: (EL) Time:  $1.3 \mu s$

Code: 014 000 STX Store X register

Format: STX <address mode> <disp.>

The contents of the X register are stored in the effective location. The address of this instruction may be modified by the contents

of the X register.

Time:  $1.3 \mu s$ Affected: (EL)

Code: 020 000 STD Store double word

Format: STD <address mode> <disp.>

The contents of the A register are stored in the effective location, and the contents of the D register are stored in the effective

location plus one.

Affected: (EL),(EL+1) Time: 2.2 μs

Code: 030 000 STF Store floating accumulator

Format: STF <address mode> <disp.>

The contents of the floating accumulator are stored in three memory locations, starting with exponent part in effective location.

Time 2.8  $\mu$ s Affected: (EL), (EL + 1), (EL + 2)

Code: 040 000 MIN Increment memory and skip if zero

Format: MIN <address mode> <disp.>

Effective word is read and incremented by one and then restored in the effective location. If the result becomes zero, the

next instruction is skipped.

True Time: 2.9 μs Affected: (EL), (P) False Time: 2.6 μs

3.1.3 Load Instructions

LDA Load A register Code: 044 000

Format: LDA <address mode> <displ.>

The effective word is loaded into the A

register.

Affected: (A) Time:  $1.0 \mu s$

LDT Load T register Code: 050 000

Format: LDT <address mode> <disp.>

The effective word is loaded into the T

register.

Affected: (T) Time:  $1.0 \mu s$

LDX Load X register Code: 054 000

Format: LDX <address mode> <disp.>

The effective word is loaded into the X register. The address of this instruction may be modified by the previous contents

of the X register.

Affected: (X) Time:  $1.0 \mu s$

LDD Load double word Code: 024 000

Format: LDD <address mode> <disp.>

The contents of the effective location are loaded into the A register, and the contents of the effective location plus one are loaded

into the D register.

Affected: (A), (D) Time: 1.6  $\mu$ s

LDF Load floating accumulator Code: 034 000

Format: LDF <address mode> <disp.>

The contents of the effective location and the two following locations are loaded into the floating accumulator, i.e., T, A and D

registers.

Affected: (T), (A), (D)

Time:  $2.0 \mu s$

# 3.1.4 Arithmetical and Logical Instructions

ADD Add to A register

Format: ADD <address mode> <disp.>

The effective word is added to the A register with the result in the A register. The carry indicator is set to 1 if a carry occurs from the sign bit positions of the adder, otherwise the carry indicator is reset to 0. If the sign of the result is different, overflow has occurred, and both the dynamic and static overflow indicators are set to one. If the condition for overflow does not exist, the dynamic overflow indicator is reset to 0, while the static overflow indicator is left unchanged.

Affected: (A), C, O, Q

Time:  $1.0 \mu s$

Code: 064 000

Code: 060 000

SUB Subtract from A register

Format: SUB <address mode> <disp.>

The 2's complement of the effective word is formed and added to the contents of the A register with the result in the A register. The same rules as for ADD apply for the setting of the overflow and carry indicators.

Affected: (A), C, O, Q

Time:  $1.0 \mu s$

Code: 070 000

AND Logical and

Format: AND <address mode> <disp.>

The logical product of the effective word and the contents of the A register are formed, with the result in the A register. The logical product contains a one in each bit position for which there is a corresponding one in both the A register and the effective word, otherwise the bit position contains a zero.

Affected: (A)

Time:  $1.0 \mu s$

ORA Logical inclusive or

Code: 074 000

Format: OR <address mode> <disp.>

Logical inclusive or is formed between the effective word and the contents of the A register, with the result in the A register. Logical inclusive or contains a zero in each bit position for which there is a corresponding zero in both the A register and the effective word, otherwise the bit position contains a one.

Affected: (A)

Time: 1.0 μs

Code: 120 000

MPY Multiply integer

Format: MPY <address mode> <disp.>

The effective word and the A register are multiplied and the result is placed in the A register. Both numbers are regarded as signed integers and the result as a 16-bit signed integer. If the result in absolute value is greater than 32767, overflow has occurred and the static and dynamic overflow indicators are set to one.

Affected: (A), O, Q

Time: 8.7 μs

Code: 100 000

FAD Add to floating accumulator

Format: FAD <address mode> <disp.>

The contents of the effective location and the two following locations are added to the floating accumulator with the result in the floating accumulator. The previous setting of the carry and overflow indicators are lost.

Affected: (T), (A), (D), C, O, Q, TG

Time: 3.6 - 14.0  $\mu$ s\*

For 32 bit floating point operation, add 5  $\mu$ s.

<sup>\*</sup> Time dependent of operands mantissa overlap.

FSB Subtract from floating accumulator

Code: 104 000

Format: FSB <address mode> <disp.>

The contents of the effective location and the two following locations are subtracted from the floating accumulator with the result in the floating accumulator. The previous setting of the carry and overflow indicators are lost.

Affected: (T), (A), (D), C, O, Q, TG

Time:  $3.9 - 16.5 \mu s^*$

For 32 bit floating point operation, add 5  $\mu$ s.

FMU Multiply floating accumulator

Code: 110 000

Format: FMU <address mode> <disp.>

The contents of the floating accumulator are multiplied with the number of the effective floating word locations with the result in the floating accumulator. The previous setting of the carry and overflow indicators are lost.

Affected: (T), (A), (D), O, Q, TG

Time:  $13.5 \mu s$

For 32 bit floating point operation, add 2  $\mu$ s.

FDV Divide floating accumulator

Code: 114 000

Format: FDV <address mode> <disp.>

The contents of the floating accumulator are divided by the number in the effective floating word locations. Result in floating accumulator. If division by zero is attempted, the error indicator Z is set to one. The error indicator Z may be sensed by a BSKP instruction (see BOP). The previous setting of the carry and overflow indicators are lost.

Affected: (T), (A), (D), Z, C, O, Q, TG

Time:  $4.3 - 15.2 \,\mu s^*$

For 32 bit floating point operation, add 0  $\mu$ s.

<sup>\*</sup> Time dependent of operands mantissa overlap.

### 3.1.5 Sequencing Instructions

JMP Jump

Code: 124 000

Format: JMP <address mode> <disp.>

The effective address is loaded into the program counter and the next instruction is taken from the effective address of the JMP instruction.

Affected: (P)

Time: 1.1 µs

JPL Transfer P to L and jump

Code: 134 000

Format: JPL <address mode> <disp.>