## NORD=10

Input/Output System

# A/S NORSK DATA-ELEKTRONIKK

## NORD-10

Input/Output System

# **REVISION RECORD**

| Revision | Notes                                    |

|----------|------------------------------------------|

| 04/74    | Original Printing                        |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          | an a |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

|          |                                          |

Publication No. ND-06.004.01 April 1974

NORSK DATA A.S.

ļ

#### TABLE OF CONTENTS

## + | +

| <u>Chapters</u> :       |                                                                  | Page              |

|-------------------------|------------------------------------------------------------------|-------------------|

| 1                       | GENERAL DESCRIPTION                                              | 1-1               |

| 2                       | IOX-INSTRUCTION                                                  | 2-1               |

| 2.1                     | Recommended Device Addresses                                     | 2-1               |

| 3                       | EXTERNAL INTERRUPT IDENTIFICATION                                | 3-1               |

| 4                       | I/O BUS ARCITECTURE                                              | 4-1               |

| 5                       | I/O BUS SIGNALS                                                  | 5-1               |

| 6                       | PROGRAMMED INPUT/OUTPUT                                          | 6-1               |

| 6.1<br>6.2              | Bus Signals<br>Data Transfer                                     | $6-1 \\ 6-2$      |

| $6.2.1 \\ 6.2.2$        | Input<br>Output                                                  | 6-2<br>6-2        |

| 7                       | INTERRUPT IDENTIFICATION SEQUENCE                                | 7-1               |

| 7.1<br>7.2              | Bus Signals<br>Interrupt Sequence                                | 7-1<br>7-2        |

| 8                       | DMA INPUT/OUTPUT                                                 | 8-1               |

| 8.1<br>8.2              | Bus Signals<br>Data Transfer                                     | 8-1<br>8-2        |

| 8.2.1<br>8.2.2          | DMA Output<br>DMA Input                                          | 8-2<br>8-5        |

| 8.3                     | DMA Sequence for a Device that has not generated a Request       | 8-5               |

| 9                       | TECHNICAL SPECIFICATIONS                                         | 9-1               |

| 9.1<br>9.2<br>9.3       | Cables<br>Signal Levels<br>Card Module Specifications            | 9-1<br>9-1<br>9-1 |

| 9.3.1<br>9.3.2<br>9.3.3 | General Description<br>Connector Standards<br>Mounting Standards | 9-1<br>9-3<br>9-3 |

| Chapters:    |                                             | Page         |

|--------------|---------------------------------------------|--------------|

| 10           | SIGNAL DISTRIBUTION WITHIN ONE<br>CARD RACK | 10-1         |

| 11           | FORMAT OF STATUS AND CONTROLWORD            | 11-1         |

| 11.1<br>11.2 | Status Word<br>Control Word                 | 11-1<br>11-2 |

v

#### GENERAL DESCRIPTION

The NORD-10 I/O system consists of two different I/O systems. One compatible with the NORD-1 I/O controlled by the IOTinstruction (160000) and a new system controlled by the IOXinstruction (164000). The NORD-1 I/O system is included to give old customers the ability of connecting already well-proven custom-designed equipment to a NORD-10 CPU.

Only the I/O system controlled by the IOX instruction will be covered in this manual.

In NORD-10 all I/O device interface cards are made to a common standard. The cardrack contains a prewired bus with a number of identical interface slots permitting any mix of devices without changing the backwiring and plug-panel. Device plugs are also made to a common standard.

This system permits the use of printed backplane wiring for all wiring within one cardrack. Cable connectors are plugged directly into the backplane or to front end connectors mounted on the circuit board.

Devices with interface integrated in the CPU (first card rack) can be operated via the A-register. When the I/O-system is expanded with another cardrack, all devices in the second rack may be programmed for transfer of characters (words) one by one via the A-register or for block transfer directly to memory. (Mass storage, card reader, high speed modem etc.)

An optional rack controller which permits control of the devices from two different CPU's (multi-machine environment) will also be available.

1

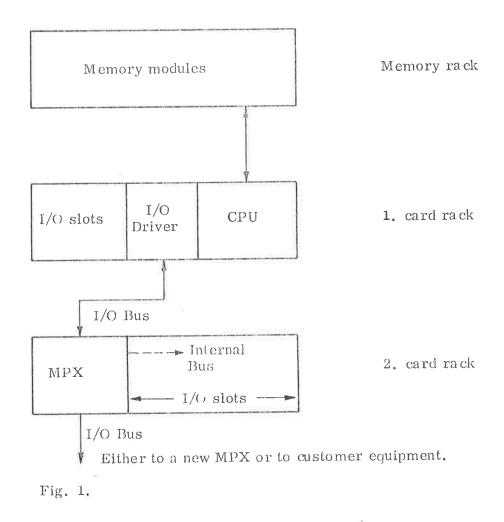

NORD-10 - General system

All card rack modules shown in figure 1 are 19" standard rack modules. One memory module holds up to 32K memory. The maximum size memory is 256K. The first card rack contains the CPU and ten standard I/O slots. All the main I/O operated by program control - such as consol teletype, paper tape reader, paper tape punch, card reader, lineprinter, display, operator panel, real time clock etc. - will be contained in the first rack.

The connection between the first rack and the second rack is a general I/O Bus which will be described in detail below. The internal bus in the 2. card rack is logicly the same general I/O Bus only separated by electronic switches. Each new card rack

1 - 2

requires a multiplexer (MPX) that contains necessary rack buffer and control and also 16 memory address registers to be used by the local I/O devices in that rack. Thus in case of DMA transfer the individual device need not supply the memory address as this is integrated in the MPX.

The position of the device interface in the card rack determines the interrupt priority of the device. If several devices within one rack are connected to the same interrupt level, the device closest to the MPX has the highest priority within that level. Also if two devices in the same card rack competes for a Direct Memory Access – the device closest to the MPX has the highest priority and will win.

#### 2-1

2

#### IOX-INSTRUCTION

All program controlled transfer between the CPU A-register and external devices is controlled by using the IOX-instruction. The IOX-instruction is loaded into the instruction register IR of the CPU, which in turn generates the I/O timing and enables the selection of the approriate device. The IOX-instruction has the following format:

|    | IOX | DEV. REGISTER ADDRESS |   |

|----|-----|-----------------------|---|

| 15 | 11  | 10                    | 0 |

IR:

| Bit 15-11: | IOX instruction = Octal value 16400 | 00 |

|------------|-------------------------------------|----|

|            |                                     |    |

Bit 10-0: 11 bits define the different device register addresses. A maximum of 2<sup>1</sup> i.e. 2048 register addresses may be specified.

The 2048 register addresses define an upper limit to the number of registers that may be addressed – some registers may require two register addresses, one for reading and one for loading. Different devices will, however, require different number of device addresses. Thus the maximum number of physical devices that may be connected will depend upon the specific configuration of devices.

Simple devices will usually require at least three different instructions (addresses), load status / control register, read status / control register and read or write data buffer register. More complex devices like magnetic tape units may need up to 8 instructions. Instructions for one and the same device are assigned successive device register addresses.

2.1 Recommended Device Addresses

Device address used for A/S Norsk Data-Elektronikk produced equipment on a standard I/O bus follows a preset assignment. The format for the different groups of devices is as follows:

| _15<br>  IOX | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                            |

|--------------|----------------------------------------------------------------------------------|

| IOX          | C=0 = 1 0 1 DISC NO. REG. NOOU MT                                                |

| IOX          | C=0 E 0 1 1 TTY NO. $\begin{array}{c} CUT \\ CII \\ CII \end{array}$ Modem       |

| IOX          | C=0 E 1 0 0 DEV. NC. DE S/COUT Tape reader<br>GRCUP                              |

| C - 0        | ND produced equipment                                                            |

| C = 1        | Customer produced equipment                                                      |

| F =          | extension                                                                        |

| Group:       |                                                                                  |

| 0 (10)       | Directly controlled registers                                                    |

| 1 (11)       | Modem (spare for group 2 & 3)                                                    |

| 2 (12)       | Alfanumeric display (spare for group 1 & 3)                                      |

| 3 (13)       | Teletype (spare for group 1 & 2)                                                 |

| 4 (14)       | Paper tape etc.                                                                  |

| 5 (15)       | Mass storage devices                                                             |

| 6 (16)       | Plotter, Intercore or other DMA-device                                           |

| 7 (17)       | Miscellaneous (not exclusive, i.e. same number may be used for different device) |

DISC NO.:

| 0 | DISC I      | (4 units) |

|---|-------------|-----------|

| 1 | DISC II     | (4 units) |

| 2 | Mag.tape I  | (4 units) |

| 3 | Mag.tape II | (4 units) |

| 4 | Drum I      | (1 unit)  |

| 5 | Drum II     | (1 unit)  |

| 6 | Drum III    | (1 unit)  |

| 7 | Drum IV     | (1 unit)  |

| REG. NO.: | Different registers within the mass memory control. |

|-----------|-----------------------------------------------------|

| 0         | Core address register                               |

| 1         | Sector-block address register                       |

| 2         | Status-control register                             |

| 2 | Status-control register |

|---|-------------------------|

| 3 | Word count register     |

| OUT C |     | Output channel } full duplex TTY Input channel } |

|-------|-----|--------------------------------------------------|

| S/C   | = 1 | Status or control register                       |

| S/C   | = 0 | Data register                                    |

| OUT   | = 1 | Output                                           |

| OUT   | = 0 | Input                                            |

## ND-06.004.01

et.

#### EXTERNAL INTERRUPT IDENTIFICATION

3

The NORD-10 has a multiprogram system based on a 16 level priority interrupt system. Each program level has a complete set of registers. Out of these 16 levels five different levels are available to external devices. These levels are:

| 15 |   | reserved extremely fast user I/O |

|----|---|----------------------------------|

| 13 | ) | Normal external                  |

| 12 |   | devices                          |

| 11 |   |                                  |

| 10 | J |                                  |

Several different interrupt sources may be connected to the interrupt levels 10, 11, 12 and 13.

To identify which device is interrupting a "who are you" type of instruction is used. This returns an 8 bit identification number from the interrupting device to the A-register. The instruction is called

#### IDENT

and belongs to the MIS-group of instructions.

Each physical device is given a unique interrupt identification number. These numbers will range from zero to 255. There is no functional correspondance between these numbers and the device register addresses used to control the devices. - Each device uses only <u>one</u> interrupt identification number while it may use several register addresses.

For level 15, which is exclusively reserved user I/O, there is no identification system, and interrupt identification is obtained by reading a status work

The detailed description of the function of the IDENT instruction is given in the section INTERRUPT HANDLING.

ND-06.004.01

. ÷ ŕ 159C

#### I/O BUS ARCITECTURE

4

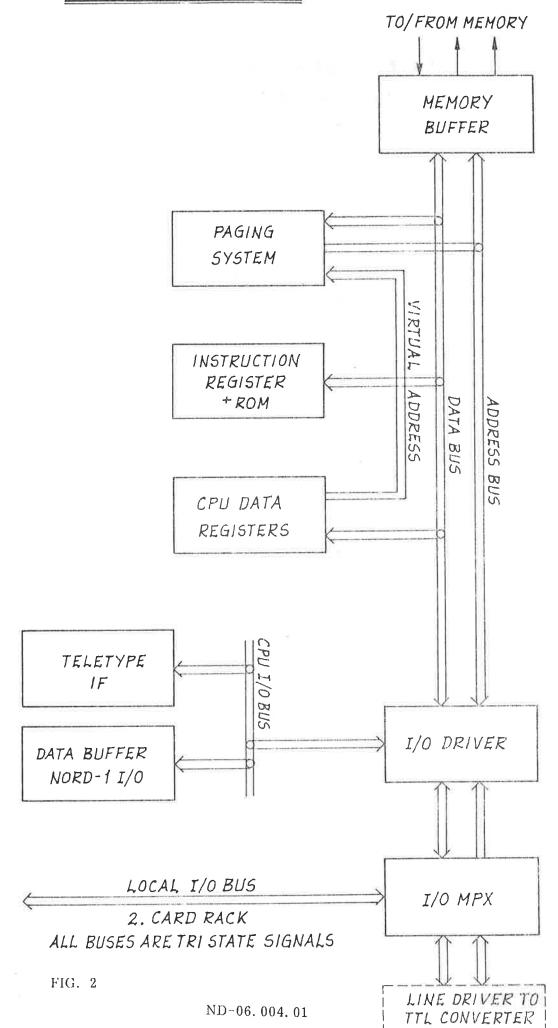

The general layout of the I/O Bus System is shown in figure 2. One of the important features with this structure is the electronic separation of the bus in each branch point such as the I/O Multiplexer and the I/O Driver.

At the I/O Driver there are provisions to manually disconnect either the external I/O bus or the internal CPU I/O bus or both. If an external device by malfunctioning is jamming the bus, the ability to disconnect the external bus at the I/O driver will allow the CPU and its local devices to operate. If an internal device by malfunctioning is jamming the local CPU I/O bus it will be possible to run a memory check program with the internal bus disconnected – thus verifying the origin of the error.

Furthermore within each Multiplexer there are provisions to protect the system from being influenced by malfunctioning devices. This is done by giving each Multiplexer the possibility to disconnect the busses branched from the Multiplexer by program control.

One device register is reserved for this purpose in each Multiplexer. Two of the bits in this register will define which of the busses to disconnect, the internal bus controlled by the Multiplexer or the external bus branching off to a lower priority Multiplexer or to customer devices.

ND-06.004.01

## I/O BUS ARCHITECTURE

#### I/O BUS SIGNALS

Table 5.1 lists the different signals on the I/O Bus:

|                 |                | SOURCE           |     |        |

|-----------------|----------------|------------------|-----|--------|

| NO. OF<br>LINES | NAME           | MEMORY<br>BUFFER | CPU | DEVICE |

| 16              | DATA           | х                | x   | х      |

| 18              | ADDRESS        |                  | х   | х      |

| 5               | * INTERRUPT    |                  |     | х      |

| 1               | IOXE           |                  | х   |        |

| 1               | CONNECT        |                  |     | х      |

| 1               | INIDENT        |                  | х   | х      |

| 1               | OUTIDENT       | ÷                |     | х      |

| 1               | INPUT          |                  |     | х      |

| 1               | INGRANT        |                  |     | х      |

| 1               | OUTGRANT       |                  |     | x      |

| 1               | * DMA REQUEST  |                  |     | x      |

| 1               | DMA DATA READY | х                |     |        |

| 1               | MPX ADDRESS    |                  |     | х      |

| 1               | MASTER CLEAR   |                  | x   |        |

Table 5.1

\* These lines are open collector signals in the internal bus, as several sources may operate these lines simultaneously. The rest of the signals are generated by tri-state logic.

5

6-1

#### 6 PROGRAMMED INPUT/GUTPUT

6.1 Bus Signals

The following signals on the I/O Bus are relevant for programmed input/output:

DATA

ADDRESS

IOXE

CONNECT

INPUT

#### MASTER CLEAR

| 16 DATA<br>Source:<br>Device or CPU | 16 lines carrying the data information from the CPU or from the device depending upon the control signal INPUT.                                                                                                                                                                                                                                    |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 ADDRESS<br>Source:<br>CPU        | Bit 0-10: Gives the value of the 11 least signifi-<br>cant bits of the CPU instruction register, i.e.<br>the device register address during an IOX-<br>instruction.                                                                                                                                                                                |

| Source:<br>Device                   | Bit 11-14: These bits are used only for loading<br>a core address into the corresponding register<br>in the Multiplexer, and selects one of sixteen<br>registers.                                                                                                                                                                                  |

| Source:<br>Device                   | Bit 15: A strobe pulse for the specific MPX core<br>address register if the same conditions as for<br>ADDRESS bits 11-14 above are true.                                                                                                                                                                                                           |

| 1 IOXE<br>Source:<br>MPX            | IOX enabling time signal, acts as a master enable<br>signal during the relevant IOX instructions. This<br>signal is defined as<br>$(IOXE_{CPU} \cdot IR \ 10_X)$<br>X = 0  or  1  depends on a strapping in the MPX.                                                                                                                               |

| 1 CONNECT<br>Source:<br>Device      | A device answer on the IOXE signal indicating that<br>the IOXE signal has been received and that the<br>device has decoded the ADDRESS bits 0-10 and<br>recognized one of its device register addresses.<br>CONNECT has to be returned within a specified<br>time (max 5 µs) otherwise the CPU will generate<br>an internal interrupt on level 14. |

1 INPUTDefines the direction of the data lines. INPUTSource:true; data transferred from device to CPU A-Deviceregister. INPUT false; data transferred from<br/>CPU A-register to device.

1 MASTER CLEAR Used to clear the logic in the device controllers. Source: CPU

#### 6.2 Data Transfer

A programmed data transfer on the I/O Bus is initiated as follows:

The IOXE signal together with the ADDRESS bits 0-10 connects a specific device to the bus. This is confirmed by the device by returning the CONNECT signal. The type of transfer depends upon the control signals INPUT.

#### 6.2.1 Input

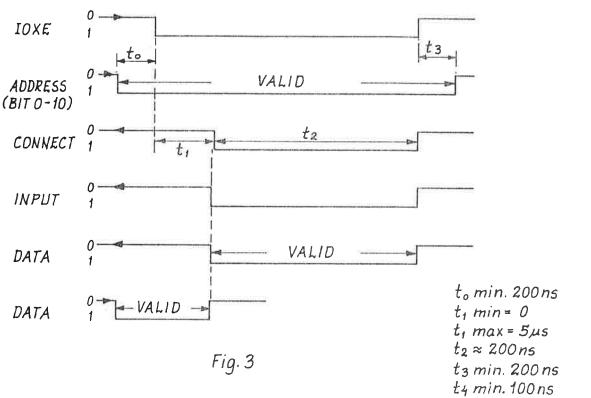

If the transfer is an input transfer i.e. data transferred from the device to the CPU, the device will together with returning the CONNECT signal also return the INPUT control signal and enable data on the DATA lines. The DATA lines has to remain stable during the rest of the IOXE signal. As soon as the IOXE signal drops, the CONNECT and INPUT signal have to be dropped. The timing sequence is shown in figure 3.

As shown in the figure it may be possible to perform both an output and an input transfer on the same IOXE. This is done by delaying the CONNECT and INPUT signal until the DATA from the CPU has been strobed by the device.

#### 6.2.2 Output

1

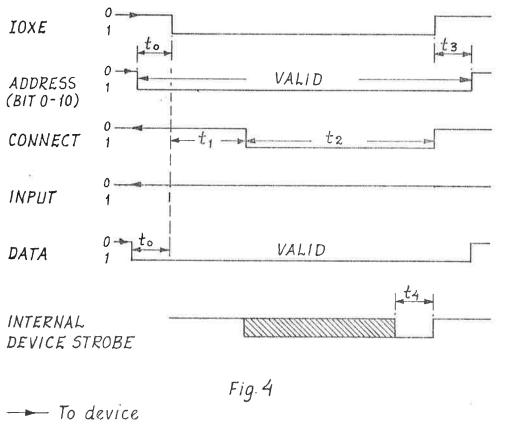

After receiving the IOXE signal as for input, the data from the CPU may be strobed into a device register. This strobe pulse could be identical to the CONNECT signal. The timing sequence is shown in figure 4.

PROGRAMMED INPUT FROM DEVICE

tymax = CONNECT

## PROGRAMMED OUTPUT TO DEVICE

ND-06.004.01

----- From device

÷. ie.

#### 7 - 1

#### 7 INTERRUPT IDENTIFICATION SEQUENCE

#### 7.1 Bus Signals

The following signals on the I/O Bus are relevant during an interrupt sequence:

DATA ADDRESS INTERRUPT INIDENT OUTIDENT CONNECT INPUT MASTER CLEAR

8 DATA Source: Device: Bit 0-7: The value of these lines are equal to the specific INTERRUPT IDENTIFICATION NO. for the device. Each physical device is given a unique interrupt identification number.

6 ADDRESS Source: CPU

Bits 0-1: Give a coded value for the external interrupt level where the program is seeking to identify an interrupt. The code is as follows:

Bit 1 0

00 - Interrupt level 10

01 - Interrupt level 11

1 0 - Interrupt level 12

1 1 - Interrupt level 13

Source: CPU Bits 2-5: Give the value of the external interrupt level where the program is seeking to identify an interrupt. The code is as follows:

Bit 5432

0001 - Interrupt level 10

0010 - Interrupt level 11

0100 - Interrupt level 12

1000 - Interrupt level 13

| 5 INTERRUPT<br>Source:<br>Device       | One line for each external interrupt level (10, 11, 12, 13 and 15). When the device wants the CPU attention one of these lines are grounded - set true. The level has to remain true until the device has been serviced by the IDENT instruction for the specific level. |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 INIDENT<br>Source:<br>CPU and device | This signal is generated at the CPU as a decoding of one of the four IDENT instructions.                                                                                                                                                                                 |

| 1 OUTIDENT<br>Source:<br>Device        | A signal transmitted to the next device's INIDENT<br>pin if the device did not generate an INTERRUPT<br>or the interrupt code did not correspond to the<br>interrupt level of the device.                                                                                |

| 1 CONNECT<br>Source:<br>Device         | A device answer on the INIDENT indicating that<br>the device that gave the INTERRUPT has recognized<br>the INIDENT and found the code for the interrupt<br>level to correspond to the level of its specific<br>interrupt.                                                |

| 1 INPUT<br>Source:<br>Device           | A line indicating that the connected device is return-<br>ing its DEVICE IDENTIFICATION NO. on the DATA<br>lines bit 0-7.                                                                                                                                                |

| 1 MASTER CLEAR<br>Source:<br>CPU       | Used to clear the logic in the device controllers.                                                                                                                                                                                                                       |

#### 7.2 Interrupt Sequence

The first device receiving the INIDENT is the first device in the interrupt priority chain. If this device gave no interrupt or the INIDENT signal was for a different level, the device will send the INIDENT signal as the OUTIDENT from this device. The next device in the priority chain will now receive this signal as its INIDENT. This daisy chaining will continue until the device that gave the interrupt recognizes the INIDENT and finds that the code for the interrupt level ADDRESS BITS 0-5 corresponds to the level for the specific device. This device will not transmit an OUTIDENT signal. The device will instead return a CONNECT and INPUT signal to the CPU.

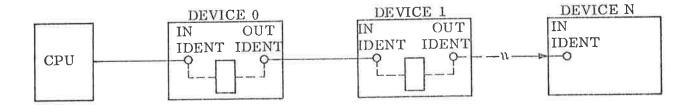

Figure 5 illustrates the daisy chaining mechanism of the INIDENT/ OUTIDENT signals.

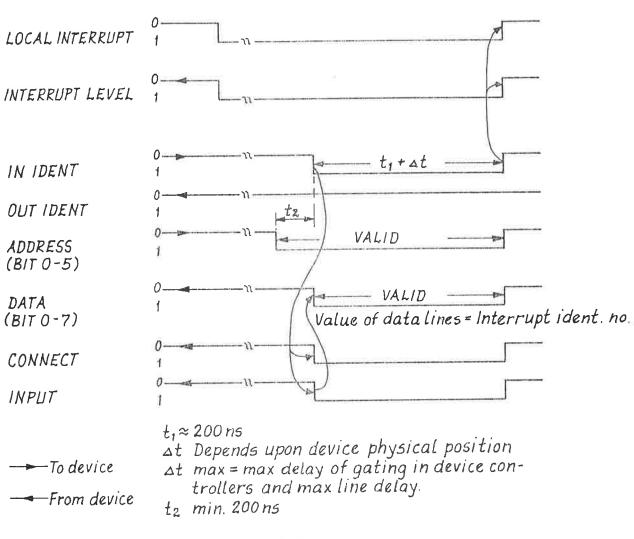

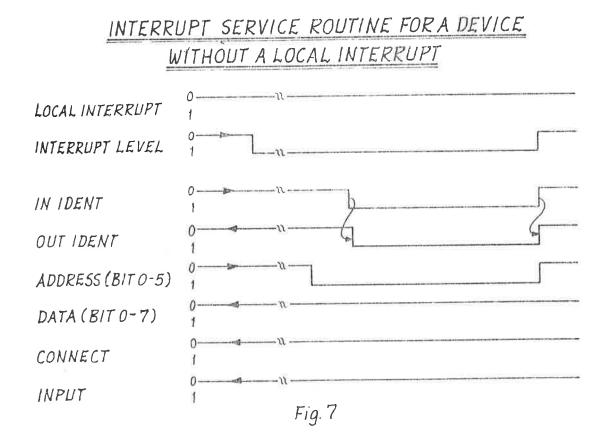

The timing diagram for the interrupt sequence of an interrupting device, is shown in figure 6. Likewise a timing diagram for a non-interrupting device is shown in figure 7. GENERATING LOCAL INTERRUPT

Fig. 6

#### 8-1

#### 8 DMA INPUT/OUTPUT

8.1 Bus Signals

The following signals on the I/O Bus are relevant for DMA input/output:

DATA

ADDRESS

INGRANT

OUTGRANT

DMA REQUEST

CONNECT

DMA DATA READY

MPX ADDRESS

INPUT

MASTER CLEAR

16 DATA Source: Device or memory 16 lines carrying the data information from the memory or from the device. Direction depends upon the control signal INPUT.

18 ADDRESS Source: Device These lines have different meaning depending on the control signal MPX ADDRESS.

MPX ADDRESS: true.

Bit 11-14: Gives the address of the specific core address register within the Multiplexer. I.e., if a DMA device uses core address register 15, the address bits 11-14 should all be true (1111)=15 when DMA REQUEST is sent to the memory.

MPX ADDRESS: false.

Bit 0-15: Gives the memory address for the DMA transfer within one 64K memory block.

Bit 16-17: Gives the memory block address, i.e., if more than 64K memory is used only one out of four memory blocks of 64K can be specified from a device within a complete data transfer. Thus ADDRESS bit 16-17 will remain static during the complete transfer while ADDRESS bit 0-15 will be counting per word. 1 INPUTA control signal indicating whether the requestSource:is for input or for output.Device

1 CONNECTA signal confirming receipt of INGRANT, and thatSource:address and data are enabled onto the bus.Deviceaddress and data are enabled onto the bus.

1 INGRANTThis signal is generated at the MPX as a responseSource:to a DMA REQUEST and indicates that the deviceMPX and devicereceiving this signal is granted the I/O Bus.

1 OUTGRANTA signal transmitted to the next device's INGRANTSource:pin if the transmitting device did not generate aDeviceREQUEST.

1 DMA REQUESTA request for receiving the I/O Bus for a DMASource:transfer.Device

1 DMA DATAA control signal from the memory. This signalREADYindicates that the DATA lines may be strobed inSource:case of OUTPUT. (The ADDRESS to the memoryMemory bufferbuffer may also be changed after receiving thissignal.)

1 MPX ADDRESSA control signal indicating whether the device isSource:using a MPX core address register.Deviceusing a MPX core address register.

1 MASTER CLEAR Used to clear the logic in the device controllers. Source: CPU

#### 8.2 Data Transfer

A DMA data transfer on the I/O Bus is initiated as follows:

A device indicates that a DMA transfer is wanted by generating the DMA REQUEST signal. The MPX will then return an INGRANT signal to the device as soon as the I/O Bus is free. The first device to receive the INGRANT signal is the first device in the DMA priority chain. If this device did not generate the DMA REQUEST, it will transmit the INGRANT signal as the OUTGRANT signal from this device. The daisy chaining mechanism for the INGRANT/OUTGRANT signal is identical to the one for INIDENT/OUTIDENT as described in the section Interrupt Sequence.

#### 8.2.1 DMA Output

After a DMA REQUEST has been placed on the bus the device is waiting for an INGRANT signal. As soon as this is received (the delay depends upon where the device is positioned in the priority chain) it is used as an enabling signal for the ADDRESS, MPX ADDRESS and CONNECT.

#### ND-06.004.01

A device with a REQUEST to be processed, will inhibit the sending of the OUTGRANT signal.

If the device is using one of the MPX core address registers, the ADDRESS bits 11-14 have to be enabled, giving the address of this register.

If the device is using its own core address register, the ADDRESS bits 0-17 gives the memory address from where the data word is fetched.

The device will then receive a DMA DATA READY signal from the Memory Buffer indicating that the DATA bits 0-15 are valid and may be strobed.

The leading edge of the DMA DATA READY signal should be used for clocking of the local data buffer register.

Once the DMA DATA READY has been received the memory address need not be valid any more, thus the MPX may use this signal as an increment pulse for the core address register of the device. (The trailing edge of CONNECT may also be used.)

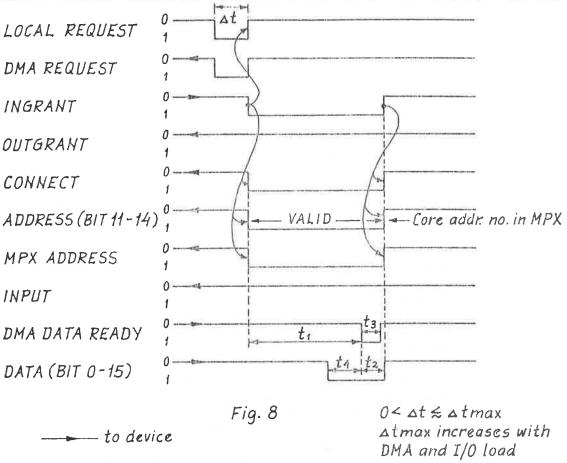

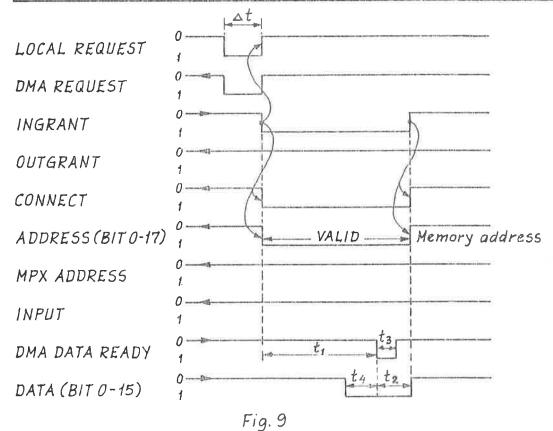

The timing sequence for DMA output is shown in figure 8 and figure 9.

DMA OUTPUT TO DEVICE USING MPX CORE ADDRESS REGISTER

$\times -4$

---- from device

DMA and I/O load  $t_{access} \neq 200 \text{ ns} < t_1 \lesssim t_{cycle}$   $20 \text{ ns} < t_2 \lesssim 100 \text{ ns}$   $t_3 \approx 100 \text{ ns}$  $25 \text{ ns} < t_4 \lesssim 200 \text{ ns}$

DMA OUTPUT TO DEVICE USING LOCAL CORE ADDRESS REGISTER

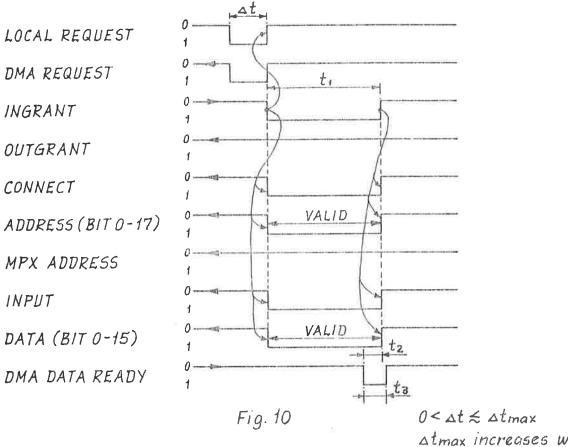

#### 8.2.2 DMA Input

8.3

The device having placed a DMA REQUEST on the line will wait for the INGRANT signal. This is used as an enable signal for the MPX ADDRESS, ADDRESS, DATA, INPUT and CONNECT signals.

If the device is using one of the MPX core address registers, ADDRESS bits 11-14 have to be enabled giving the address of this register.

If the device is using its own core address register, the ADDRESS bits 0-17 give the Memory Address to where the data word is transferred.

When the INGRANT signal is turned off, address and data have been strobed into the Memory Buffer, and should be disabled.

The timing sequence for a DMA output is shown in figure 10.

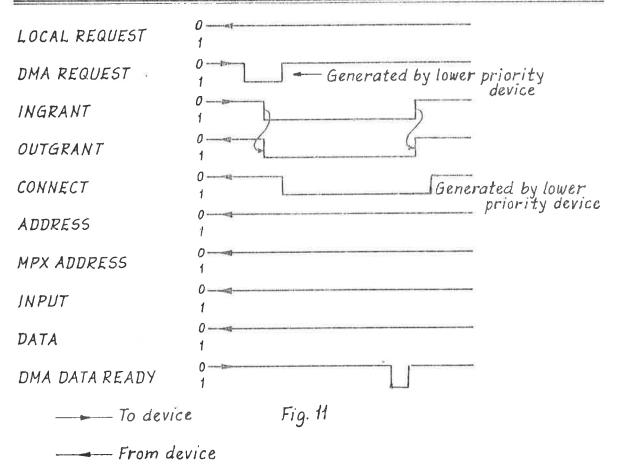

DMA Sequence for a Device that has not generated a Request

If a device of lower priority has generated a DMA REQUEST, the higher priority devices have to be active during the DMA sequence. The higher priority devices have to transmit the INGRANT signal to the OUTGRANT signal so that the device requesting a DMA sequence will receive an INGRANT signal. This daisy chaining mechanism is the same as shown for interrupt in figure 5.

The timing sequence for the DMA daisy chaining is shown in figure 11.

8-6

DMA INPUT FROM DEVICE USING LOCAL CORE ADDRESS REGISTER

$\triangle t_{max}$  increases with DMA and I/O load 300 ns <  $t_1 \lesssim t_{cycle} + 200 ns$ 20 ns <  $t_2 \lesssim 100 ns$ ,  $t_3 \approx 100 nc$

DMA SERVICE ROUTINE FOR A DEVICE NOT GIVING LOCAL REQUEST

#### 9 TECHNICAL SPECIFICATIONS

#### 9.1 Cables

Three cables are used for I/O connections outside the CPU-cabinet, one each for data, address and control. Each cable has 20 twisted pairs, with 120n impedance.

#### 9.2 Signal Levels

Internal I/O Bus signals are TRI-STATE TTL for all signals except interrupt lines and DMA request line, which are open collector TTL.

Logical "1" signal:  $0 < S \le 0, 4V$

Logical "0" signal:  $2, 4 \le S \le 5V$

The drive (sink) capability of each driver should be 30 mA.

The load on each input terminal should not be more than 0,1 mA in high state and 1,6 mA in low state. External I/O Bus signals supplied on cables are twisted pair differential line drivers/receivers using the DM 8820/8831 or equivalent.

9.3 Card Module Specifications

#### 9.3.1 General Description

The modules are a 100-terminal edge connector with contact fingers on 0.1" grid.

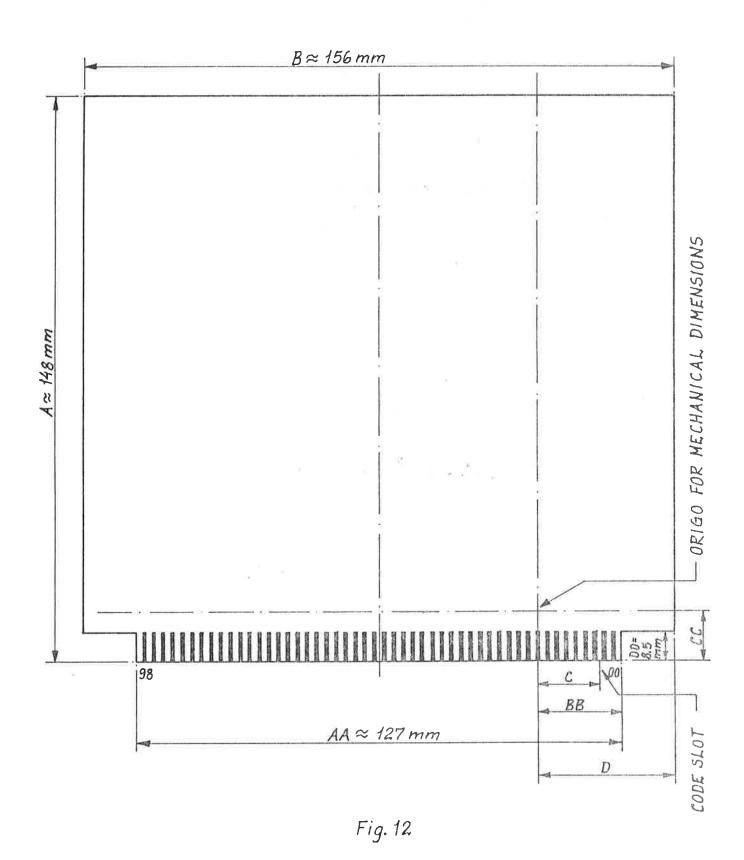

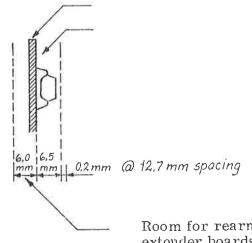

The module board dimensions relevant to its mounting in card-frame are given in figure 12 page 9-2.

The contact area of the module is specific, based on use with a 50 + 50 terminal connector with 0.1" spacing, symmetrically located relative to the board centerline.

There are a number of 100-pin connectors available, differing only slightly in mechanical dimensions. Only the corner cut-outs of the board need special adaption to the connector selected. As a secondary standardization a BURNDY connector has been shoosen, and the specific board dimension are given in the tables.

ND-06.004.01

A =

$148.2 \pm 0.3 \text{mm}$

B =

$156.2 \pm 0.2 \text{mm}$

C =

$16.51 \pm 0.1 \text{mm}$  (to centerline of code slot)

D =

$36.19 \pm 0.1 \text{mm}$

Contact finger width:

$50 \text{ mil} (1.27 \pm 0.1 \text{mm})$

Distance between fingers:

$50 \text{ mil} (1.27 \pm 0.1 \text{mm})$

Board thickness: nom. 1.6mm, 1.5 - 1.8mm incl. finishes to 3mm from edge.

9.3.2 Connector Standards

Specific to modules for use with connector: BURNDY PCBD 50 M10 GE00.

| AA =             | $127.32 \pm 0.15$ mm |                         |

|------------------|----------------------|-------------------------|

| BB =             | 21.76 <u>+</u> 0.1mm | , ×                     |

| CC =             | 13.6 <u>+</u> 0.2mm  |                         |

| DD =             | 8.5 <u>+</u> 0.2mm   |                         |

| Code slot depth: |                      | 8.5 <u>+</u> 0.5mm      |

| Code slot width: |                      | $1.0 \pm 0.1 \text{mm}$ |

#### 9.3.3 Mounting Standards

Heigths of finished mounted modules is given in figure 13.

#### ND-06.004.01

Room for rearmounted contacts, bus-bars, extender boards, etc.

Modules with larger components will require two slots in the  $\rm I/O$  rack.

|                    |       | Terminal no. |

|--------------------|-------|--------------|

| ADDRESS BIT        | 15    | 52           |

|                    | 16    | 53           |

|                    | 17    | 54           |

| OUTIDENT           |       | 6            |

| INIDENT            |       | 7            |

| OUTGRANT           |       | 8            |

| INGRANT            |       | 9            |

| IOXE               |       | 11           |

| INPUT              |       | 15           |

| MPX ADDRESS        |       | 19           |

| CONNECT            |       | 23           |

| INTERRUPT LEVEL 10 |       | 27           |

| INTERRUPT LEVEL 11 |       | 31           |

| INTERRUPT LEVEL 12 |       | 35           |

| INTERRUPT LEVEL 13 |       | 39           |

| INTERRUPT LEVEL 15 |       | 43           |

| DMA REQUEST        |       | 47           |

| DMA DATA READY     |       | 51           |

| MASTER CLEAR       |       | 55           |

| DEVICE CONNEC      | TIONS | 56 - 95      |

| +5V                |       | 0, 1, 98, 99 |

| GROUND             |       | 2, 3, 96, 97 |

| BFQ1 19,2 kh       | Z     | 4            |

| BFQ2 307,2 kh      | Z     | 5            |

590

124

10-1

### SIGNAL DISTRIBUTION WITHIN ONE CARD RACK

Terminal no.

| DA' | TA BIT  | 0   |   |   |    | 10 |

|-----|---------|-----|---|---|----|----|

| 11  | 11      | 1   |   |   |    | 12 |

| 11  | * *     | 2   |   |   |    | 13 |

| 11  | 11      | 3   |   |   |    | 14 |

| 11  | 11      | 4   |   |   |    | 16 |

| TŤ  | 11      | 5   |   |   |    | 17 |

| 11  | 11      | 6   |   |   |    | 18 |

| 11  | 11      | 7   |   |   |    | 20 |

| 11  | 11      | 8   |   |   |    | 21 |

| Ħ   | 7.8     | 9   |   |   |    | 22 |

| 11  | 11      | 10  |   |   |    | 24 |

| н   | 11      | 11  |   |   |    | 25 |

| 11  | 11      | 12  |   | 2 |    | 26 |

| 11  | 11      | 13  |   |   |    | 28 |

| TT. | **      | 14  |   |   | 30 | 29 |

| 11  | 11      | 15  |   |   |    | 30 |

|     |         |     |   |   |    |    |

| AD  | DRESS I | BIT | 0 |   |    | 32 |

|     |         |     | 1 |   |    | 33 |

|     |         |     |   |   |    |    |

$\mathbf{2}$

4

ND-06.004.01

11 - 1

0

9

10

11

#### FORMAT OF STATUS AND CONTROLWORD

The format of status and controlword may be assigned by the designer of each device controller. The following standard is used by ND for its own device control cards (when applicable) and is recommended for customer use.

11.1

Status Word

BIT

Ready for transfer, interrupt enabled

1 Error interrupt enabled

2 Device active

3 Device ready for transfer

- 4 Inclusive OR of errors

- 5 Error indicator

- 6 <sup>14</sup> <sup>1†</sup>

- 7 11 11

- 8 11 11

Selected unit

11 11

11 Operational mode of device

| 12 | н  | н 🖂 | 11 | 11 |

|----|----|-----|----|----|

| 13 | 11 | 11  | 11 | 11 |

| 14 | 11 | 11  | ** | 11 |

| 15 | 11 | 11  | 11 | 11 |

ND-06.004.01

#### 11.2 Control Word

BIT

- Enable interrupt on device ready for 0 transfer

- Enable interrupt on errors 1

- 2 Activate device

- 3 Test mode

- Device clear 4

- Address bit 16 5

- Address bit 17 6

- 7 Not assigned

- п п 8

- 9 Unit select

- 11 11 10

Device operation 11

| 12 | 11 | 11  |  |

|----|----|-----|--|

| 13 | 11 | 11  |  |

| 14 | 11 | * * |  |

| 15 | 11 | 11  |  |

15

NORSK DATA A.S. Lørenvn 57 - Postboks 163, Økern OSLO 1

## COMMENT AND EVALUATION SHEET

NORD-10 Input/Output System

ND-06,004.01

In order for this manual to develop to the point where it best suits your needs, we must have your comments, corrections, suggestions for additions, etc. Please write down your comments on this preaddressed form and post it. Please be specific wherever possible.

**FROM**:

# - we want bits of the future

A/S NORSK DATA-ELEKTRONIKK LØRENVEIEN 57 OSLO 5 NORWAY PHONE: 217371 TELEX: 18284