HARDWARE MANUAL

VOLUME II

FLOW DIAGRAMS

HARDWARE MANUAL

VOLUME II

FLOW DIAGRAMS

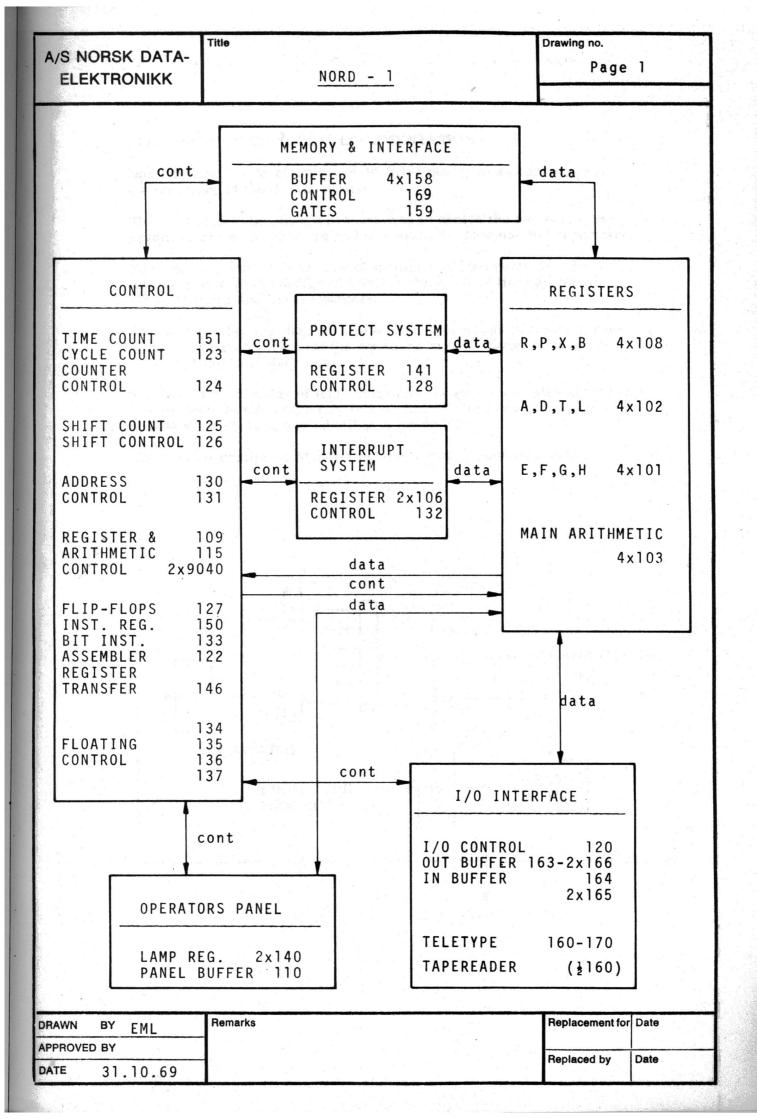

## NORD-1 COMPUTER SYSTEMS

TABLE OF CONTENTS

v. T + X T X

1=1 1:0

# Hardware Manual Volume II Flow Diagrams

A/S NORSK DATA-ELEKTRONIKK

Wid Harris (pate)

E MARY A ENTERFEE

PURTER EXTENSION 169 GATCS 169

## TABLE OF CONTENTS

PROTECT SYSLEM

1 Introduction

2 Flow Diagrams

3 Signal Definitions

### INTRODUCTION TO NORD-1 DOCUMENTATION

Summarizing the development of NORD-1 may give a coarse idea of the structure of the documentation.

The first step in the design process was to decide the number of programmer oriented registers and the instruction format and repertoire.

The next step was to draw flow diagrams of all instructions. Part of this work is also the design of CPU-arithmetic and timing control (Time Counter and Cycle Counter).

To translate the flow diagrams into logical equations is a straight forward mechanical work, and the equations may be regarded as a rewriting of the flow diagrams.

The last step, drawing of logic diagrams, is even more straight forward. The problem at this stage consists of distributing circuits on circuit boards and definition and labelling of subsignals.

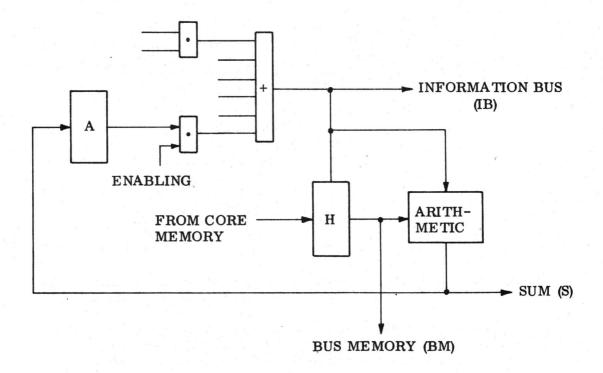

The basic operation of NORD-1 is illustrated in the figure below.

One register is enabled at a time and presented at the IB terminals, and as input to the arithmetic. Data from memory goes via the H-register and the BM input to the arithmetic. For inter-register operations one of the operands (source) is first transferred to the H-register before IB is switched to the other operand. The output of the arithmetic is then routed back to all registers where it may be strobed into register flip-flops.

The purpose of the control logic therefore is to generate the appropriate sequence of register enabling signals and register strobe pulses and to control the arithmetic to give the desired function, all as a result of the instruction decoded.

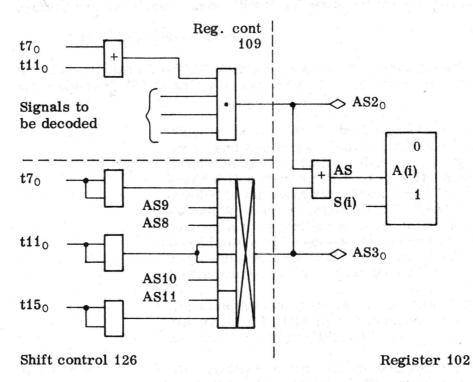

The operation of the logic is synchronous, i.e. controlled by a common timing source (Time Counter and Cycle Counter). To avoid timing hazards the timing signals, after being decoded from the time counter flip-flops, always passes three stages of logic circuits before reaching the register flip-flops.

Example: Generation of A-register set pulse.

The timing synchronization of all registers in CPU is similar to the example shown for the A-register.

As further introduction to the NORD-1 documentation three instructions will be taken as examples and all important active signals connected to each block in the flow diagrams will be described in detail.

1. add 120

- 2. skp dx gre zro

- 3. shad rot 5

The reader is advised to find the mentioned signals in the logic diagrams, to familiarize himself with the documentation.

### add 120

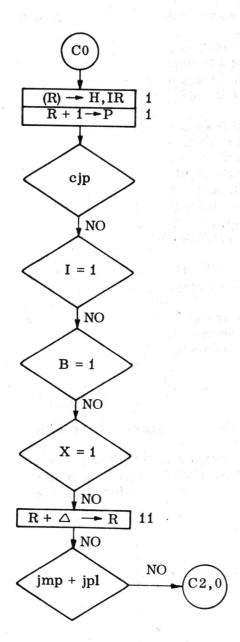

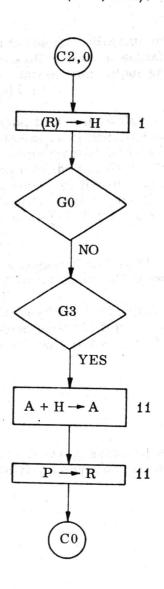

Relevant flow diagrams: Pages 1 and 12

The instruction add is a two-memory cycle instruction requiring two 16 bit words to be read from core memory, first the instruction itself (C0) and then the data word (C2).

The Time Counter control signals BACK and NEXT are both 0 in both cycles, and the Time Counter therefore produces the short sequence

to lasts until DATA READY is received from the memory control and is approximately 800 ns with a 1.5  $\mu s$  memory. All other time intervals are 100 ns.

$(R) \rightarrow H, IR$

When entering to in Co the R-register contains the actual address and a Memory Request signal is generated by CPU (RQ1). (Note: Last instruction ended with a transfer of P to R). The address is enabled to the memory address input MR (158), and a Read/Restore is intiated (INIT, RRA 169). The content of the specified memory location is transferred to the MB-register (Memory Control Module) and a Data Ready signal is returned to CPU (RY1). RY1 restarts the Time Counter and t1 is entered.

The memory communication bus MJ is now equal to MB (enabled by CPUE) and is strobed into IR (IS1) and the H-register (HS1, ME1).

$R + 1 \rightarrow P$

This addition is done via the address arithmetic. First P is set to all ones (PS3) and then the appropriate zeroes are transferred to P via the flip-flop clear terminal (PS4). RE1 enables the R-register as input to the arithmetic and CY2 generates the 1 to be added as a carry input to the least significant stage of the adder.

$R + 120 \rightarrow R$

Address arithmetic addition (RE1, HE2, SX1, RS1).

R is equal to the address of current instruction. 120 is the displacement of the instruction with sign extension, i.e. bits 8 through 15 equal to bit 7. 120 is transferred via the H-register and SX1 controls the sign extension mechanism.

The flip-flop D-input is used since the input to R is a function of R itself.

(R) - H

Similar to (R) - H, IR

$A + H \rightarrow A$

Input to the arithmetic is enabled by HE1 and AE1, which makes BM=H and IB=A.

The output of the arithmetic is the sum of RM and IR

The output of the arithmetic is the sum of BM and IB if no other control signal is active. (PLUS= $XR_0ID_0BD_0$ ). The sum is strobed into A at t11 by AS2.

$P \rightarrow R$

Transfer via address arithmetic (PE1, RS1).

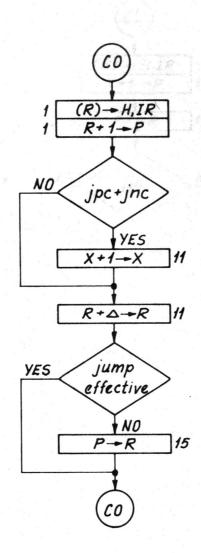

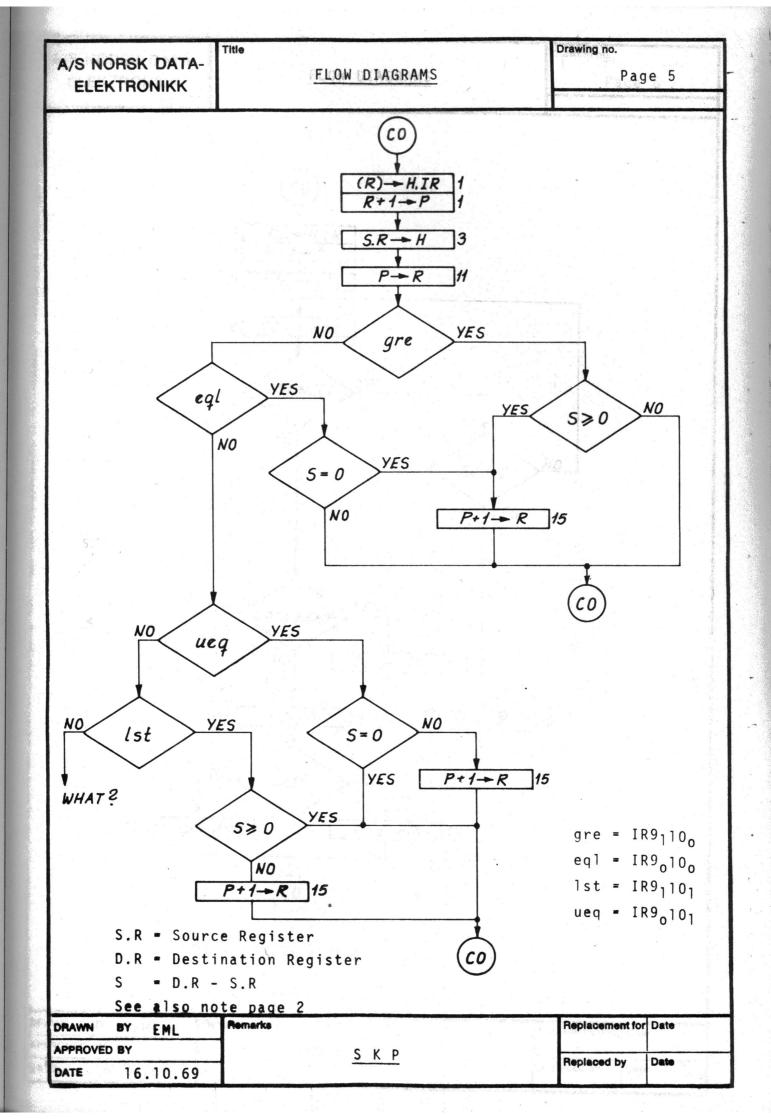

### skp dx gre zro

Relevant flow diagram: Page 5

This instruction is a one cycle instruction (C0). The Time Counter control signal NEXT depends upon resulting skip condition and selects one of the following two time pulse sequences.

skip not effective:

t0-1-2-3-8-9-10-11-0

skip effective:

t0-1-2-3-8-9-10-11-12-13-14-15-0

(R) → H, IR

same as example 1

$R + 1 \rightarrow P$

same as example 1

S.R. - H

In the instruction above the source register code is 0, which means that no register is enabled and therefore IB=0. This zero is transferred to the H-register (IE1, HS1).

$P \rightarrow R$

same as example 1

The branching conditions in the flow diagram depends upon the sum output. The active control signals engaged in producing the correct sum output are XE3, HE1, BC0, BC8 and CY1.

We want the sum to be equal to X-H, which with two's complement representation of negative numbers means that H should be complemented bit by bit (BC0, BC8) and a one added to the result (CY1). If the resulting sum is positive, i.e. S15=0, the next instruction should be skipped. This means that the content of R should be replaced by P+1, and operation requiring additional time.

The Time Counter control signal NEXT (NX1) adds time pulses t12-13-14-15 to the "normal" sequence.

$P + 1 \rightarrow R$

Address arithmetic addition (PE1, CY2, RS1). RS1 is unconditionally dependent upon t15 for C0:skp since t15 in this case exists only if P + 1 -> R is wanted.

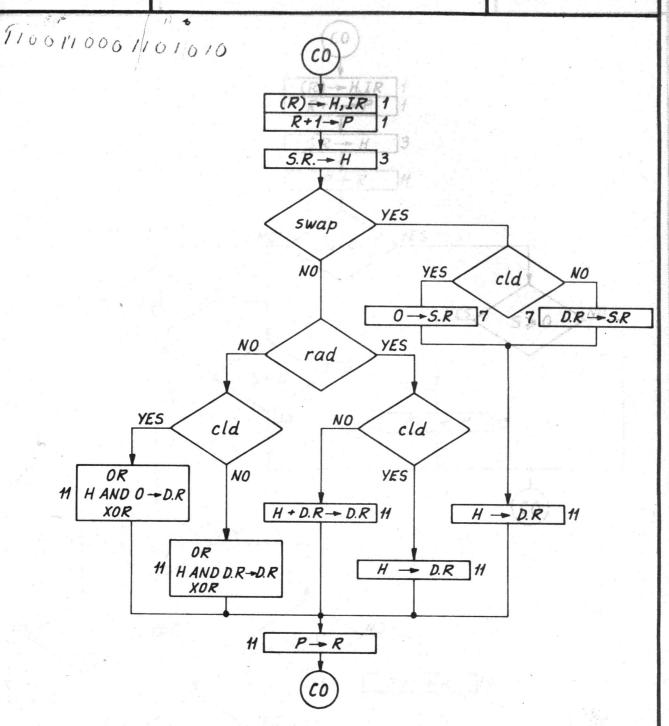

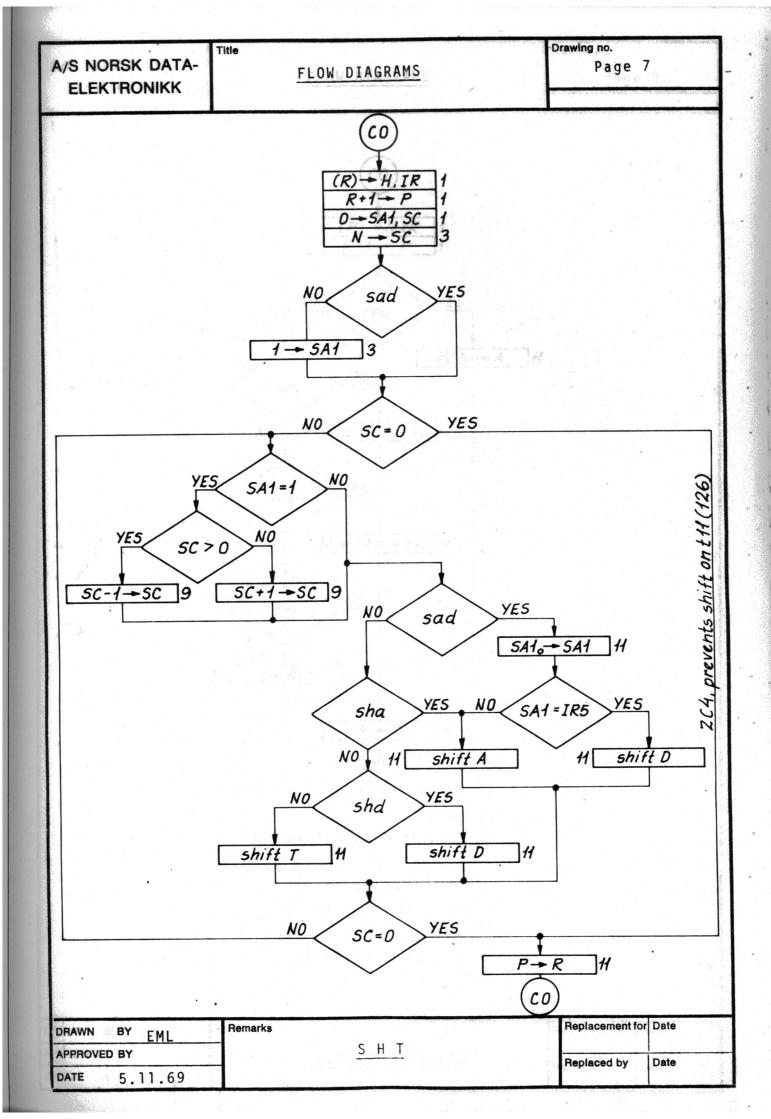

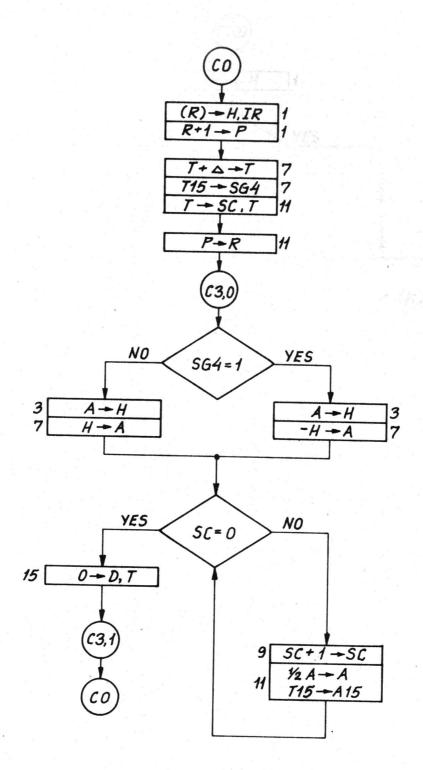

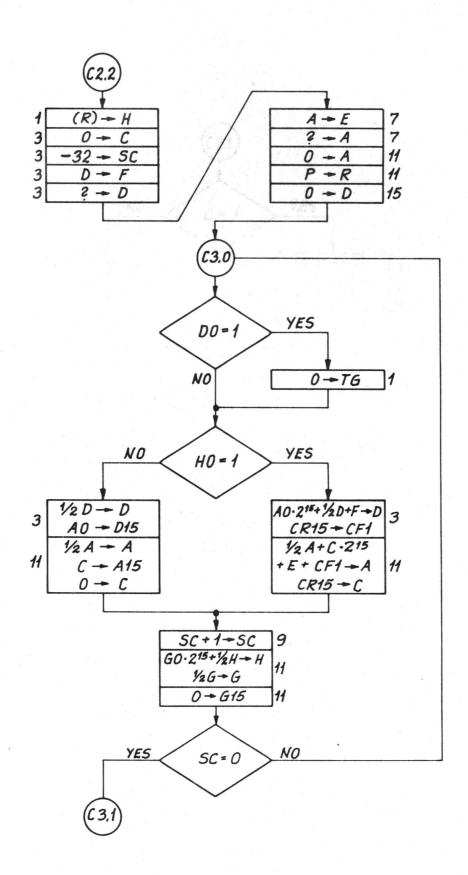

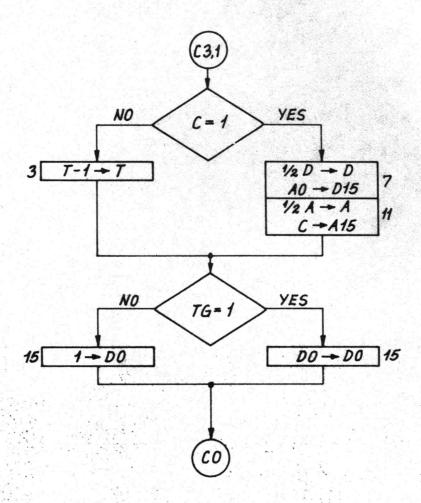

### shad rot 5

Relevant flow diagram: Page 7

Double shifts (AD connected, 32 bits) are done in two phases, 16 bits shifted at a time. SA1 is a phase control flip-flop being complemented at each shift pulse.

SA1 = 0: shift the D-register SA1 = 1: shift the A-register

No shift direction specified means left shift.

$(R) \rightarrow H, IR$

Same as example 1

$R + 1 \rightarrow P$

same as example 1

$0 \rightarrow SA1$ , SC

Reset Shift Counter (SC) and the phase control flip-flop

(SA1).

ining writte

5 - SC

5, the number of places to be shifted, is transferred from the H-register to the shift counter via the main arithmetic (required by floating point instructions). (HE1, BD, SS8).

$SC - 1 \rightarrow SC$

If SA1 = 1 the shift counter is decremented.

$SA_0 \rightarrow SA$

Complement the phase control flip-flop.

shift D

If SA1 = 0 shift the D-register one place to the left. (DE1, IL, ID, DS2, DX1).

IL enables left shift of IB. ID makes the output of the arithmetic equal to the IB-input and DX1 selects A15 as input to D0. The discarded bit (D15) is transferred to the link flip-flop M.

shift A

If SA1 = 1 shift A-register one place to the left (AE1, IL, ID, AS3, DX1). In this case DX1 selects M as input to A0, and the discarded bit (A15), which has already been transferred to D0, replaces the previous content of M.

If the content of the shift counter is not zero go back to  $SC - 1 \rightarrow SC$ . This is controlled by the Time Counter control signal BACK (BK1), which repeats pulses t8-9-10-11 the required number of times, ten in our case, five for each phase.

$P \rightarrow R$

same as example 1

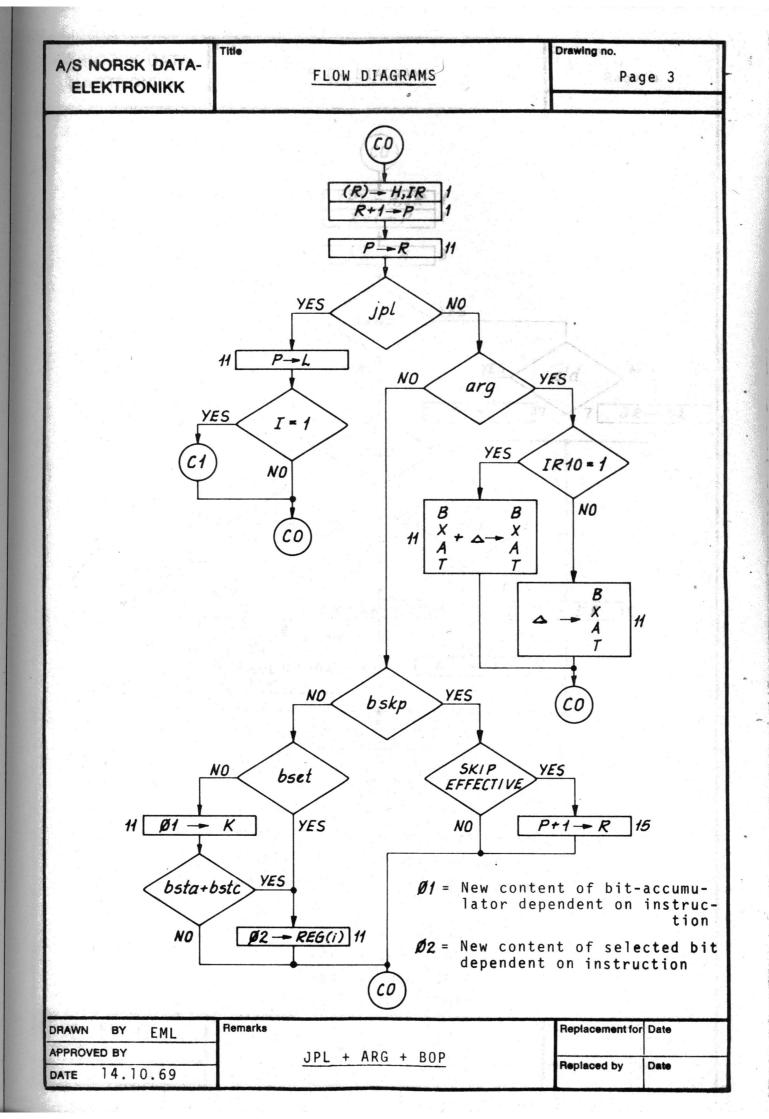

### 2 FLOW DIAGRAMS

Below follows a list of symbols and abbreviations used in the FLOW DIAGRAMS together with a short explanation.

| AW                                         | Anything written                                                                           |

|--------------------------------------------|--------------------------------------------------------------------------------------------|

| DP                                         | Deposit                                                                                    |

| SA                                         | Set Address Flip-flops on the                                                              |

| SI                                         | Single Instruction Assembler 122                                                           |

| ST                                         | Stop                                                                                       |

| TR                                         | Tape-Reader                                                                                |

| SR                                         | Source-Register                                                                            |

| DR                                         | Destination-Register                                                                       |

| S                                          | DR - SR (Sum output)                                                                       |

| (R)                                        | The contents of the cell which address is contained in the R-register                      |

| REG (i)                                    | Bit in the register                                                                        |

| Δ                                          | Displacement of the instruction (lower half of H with sign extension)                      |

| A ← G                                      | The A- and the G-register is exchanged                                                     |

| T14 <sub>0</sub> - T14                     | Bit 14 in the T-register is complemented                                                   |

| 2X - X                                     | Left shift of the X-register                                                               |

| 1/2X→X                                     | Right shift of the X-register                                                              |

| T15 ⊕ H15 → SG1                            | Exclusive or of bit 15 of the T- and the H-register. If T15 is the oposite of H15, $1-SG1$ |

| T15 ⊕ H15 <sub>0</sub> → SG1               | If T15 is equal to H15, 0 - SG1                                                            |

| $A0 \cdot 2^{15} + 1/2D \longrightarrow D$ | Right shift of the D-register with A-register bit 0 shifted into D-register bit 15         |

|                                            |                                                                                            |

Drawing no. Title A/S NORSK DATA-Page 1 FLOW DIAGRAMS ELEKTRONIKK R plker i memory  $(R) \rightarrow H, IR$ R+1 - P YES See page 2 NO cjp NO YE5 I = 1YES NO YES B=1 B = 1  $B+\Delta \rightarrow R$ NO NO X=1 $R+\triangle \rightarrow R$ YE5 R+A-R  $HX+\Delta\rightarrow R$ (R)-H YES X = 1YE5 X = 1B+X+A-R H NO  $H + X \rightarrow R$ NO B + △ → R 11  $H \rightarrow R$ 11 YES. jmp+jpl △ = Lower half of H with sign extension. Replacement for Date

APPROVED BY

DATE 14.10.69

Remarks

ADDRESSING SEQUENCE GO - 5

Replaced by Date

Title

FLOW DIAGRAMS

Drawing no.

Page 2

NOTE: t12 - 15 is "inserted" only if jump not effective and does not exist with jump effective. Controlled by signal <u>NEXT</u> to time counter.

| DRAWN BY EML  | Remarks      | Replacement for Date |

|---------------|--------------|----------------------|

| APPROVED BY   | <u>C J P</u> | Replaced by Date     |

| DATE 14.10.69 |              | heplaced by          |

Title

FLOW DIAGRAMS

Drawing no.

Page 4

If D.R.=P P→R is replaced by S→R.

If IR7=1 H is replaced by one's complement of H in the diagram above.

swap =  $IR10_09_08_0$ cld = 100 (IR6) rad = 2000 (IR10)

cm1 = 200 (IR7)

| Remarks | Replacement for    | Date           |

|---------|--------------------|----------------|

| R O P   | The spirit America | and the second |

|         | Replaced by        | Date           |

|         | Remarks R O P      | R O P          |

Title

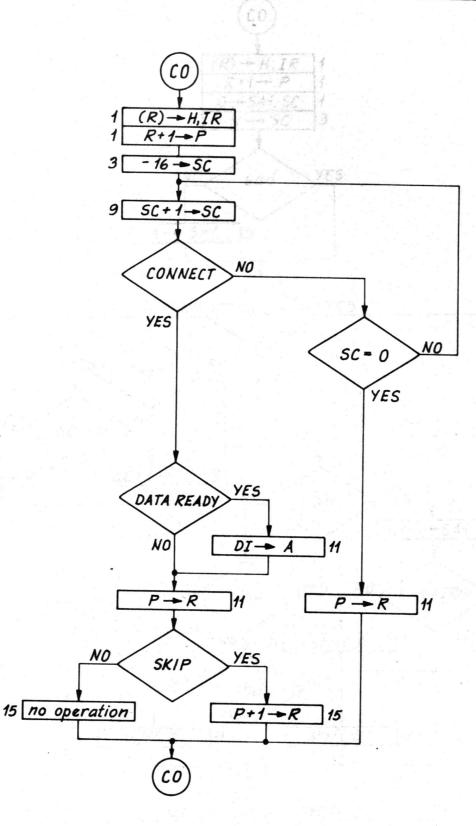

DI = I/O Data in bus bits O - 15.

| DRAWN BY EML  | Remarks | Replacement for Date |

|---------------|---------|----------------------|

| APPROVED BY   | T 0 T   |                      |

| DATE 15.10.69 | 101     | Replaced by Date     |

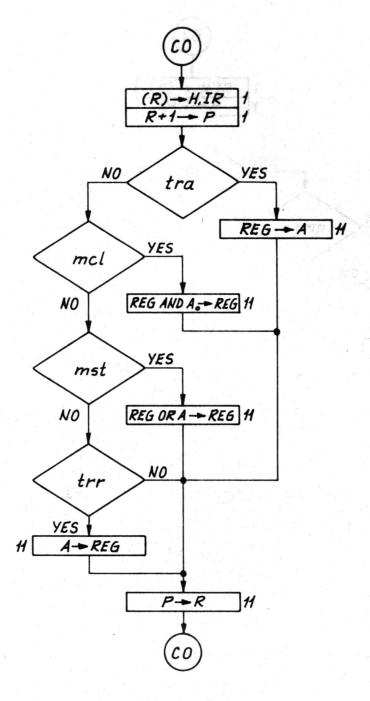

Title

FLOW DIAGRAMS

Drawing no.

Page 8

### 0 ≤ REGISTER ADDRESS ≤ 63

tra - 150.000

trr = 150.100

mc1 - 150.200

mst = 150.300

| DRAWN BY EML  | Remarks           | Replacement for | Date |

|---------------|-------------------|-----------------|------|

| APPROVED BY   | REGISTER TRANSFER |                 |      |

| DATE 15.10.69 |                   | Replaced by     | Date |

Title Drawing no. A/S NORSK DATA-FLOW DIAGRAMS Page 9 **ELEKTRONIKK** CO  $(R) \rightarrow H,IR$ R+1-P NO YE5 IN-1 NO NO YES jmp jmp YES NO wait RJ = 1see page 1 see YE5 YES YES page 1 11 1-ST 20+PL-- R 11 P-- R NO RJ = 1C1,0 C8.0 YES. 11  $0 \rightarrow PD(i)$  $P \rightarrow R$ (R)→H 11 ANY INTERRUPT H-R NO 11 YES. 9 PK-PL 20 + PL--R (R)-H

△ = displacement

C2.0

$(R) \rightarrow H$

$H \rightarrow X$   $P \rightarrow R$

60

0 - RJ

$H \rightarrow R$

CO

| DRAWN BY EML  | Remarks         | Replacement for | Date |

|---------------|-----------------|-----------------|------|

| APPROVED BY   | WAIT + JMP • IN |                 |      |

| DATE 15.10.69 |                 | Replaced by     | Date |

Title Drawing no. A/S NORSK DATA-FLOW DIAGRAMS Page 10 **ELEKTRONIKK**  $(R) \rightarrow H, IR$ R+1-P 11 T140-T14 P-R A15 -564 A -- H NO YES A = 03[ 1 -TG 0 - TGNO YES. H15=1 $H \rightarrow A$ -H - A 0-T15 1 -T15 0 - Do 15 NO YES TG=1 T-1-T ]3 0-T FL4 (Repeat cycle) co YES NO A15=1 2A-A H

| DRAWN BY EML  | Remarks | Replacement for | Date |

|---------------|---------|-----------------|------|

| APPROVED BY   | N L Z   |                 |      |

| DATE 15.10.69 |         | Replaced by     | Date |

Title

FLOW DIAGRAMS

Drawing no.

| DRAWN BY EML Rema | rks   | Replacement for | Date |

|-------------------|-------|-----------------|------|

| APPROVED BY       | D N 7 |                 |      |

| DATE 15.10.69     | D N Z | Replaced by     | Date |

Title

FLOW DIAGRAMS

Drawing no.

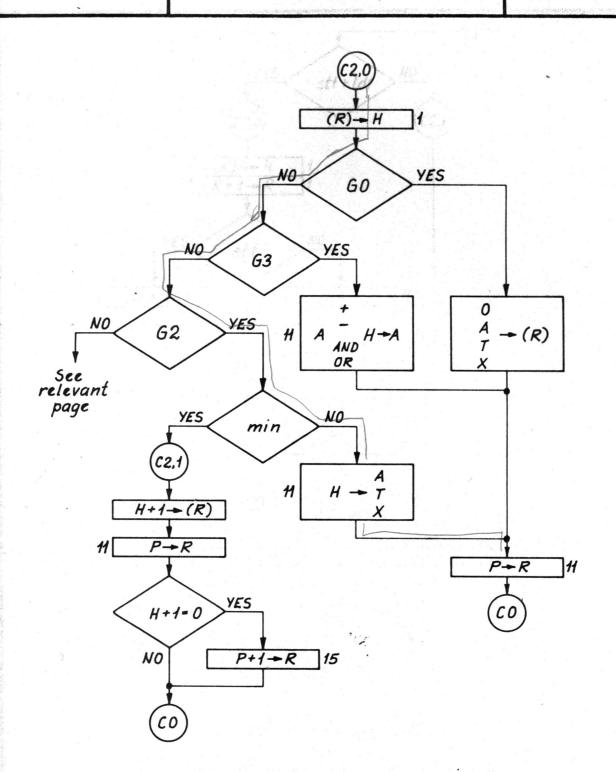

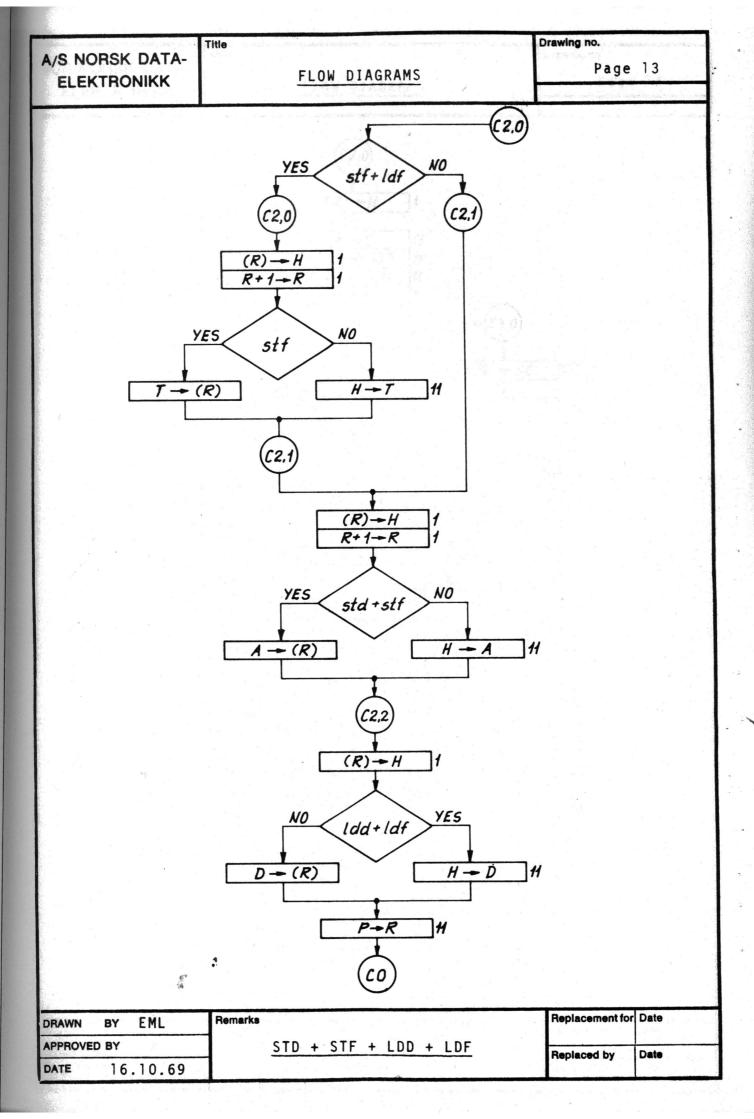

$$G0 = stz + sta + stt + stx$$

$G2 = min + 1da + 1dt + 1dx$

$$G3 = add + sub + and + ora$$

| DRAWN BY EML  | Remarks    | Replacement for | Date |

|---------------|------------|-----------------|------|

| APPROVED BY   | GO + 2 + 3 |                 |      |

| DATE 16.10.69 |            | Replaced by     | Date |

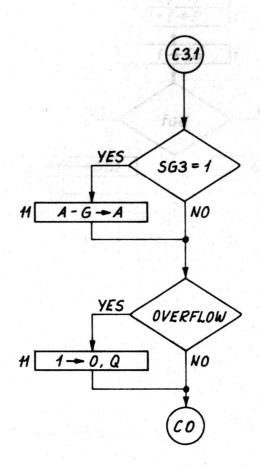

Title Drawing no. A/S NORSK DATA-Page 14 FLOW DIAGRAMS **ELEKTRONIKK** 7450 (R)-H A-G H15 → 5G3 11  $0 \rightarrow A, Q$ 11 P-R 11 C3,0 -16 - SC YE5 5G3=1 NO IC1, BK1 gives signal BACK to TIME COUNTER NO NO H15 = 1 H15 = 011 YES 2A + AYES 2A+G-A 11 2A-G+A YES. OVERFLOW A15 (t8-4) repeated H 1-0, Q NO 2H -- H 11 SC+1 -SC NO

| DRAWN   | BY   | EML   | Remarks | 8     | Replacement for | Date |

|---------|------|-------|---------|-------|-----------------|------|

| APPROVE | D BY |       |         | M P Y |                 |      |

| DATE    | 16.  | 10.69 |         |       | Replaced by     | Date |

SC = 0

YES

Title

FLOW DIAGRAMS

Drawing no.

| DRAWN    | BY   | EML  | Remarks | Replacement for | Date       |

|----------|------|------|---------|-----------------|------------|

| APPROVED | BY   |      | мрү     | Designed by     | <br>  D-4- |

| DATE     | 16.1 | 0.69 |         | Replaced by     | Date       |

Title

FLOW DIAGRAMS

Drawing no.

Page 16

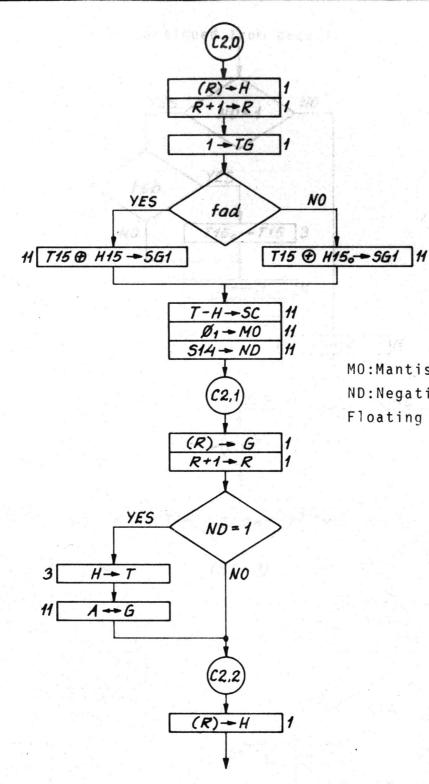

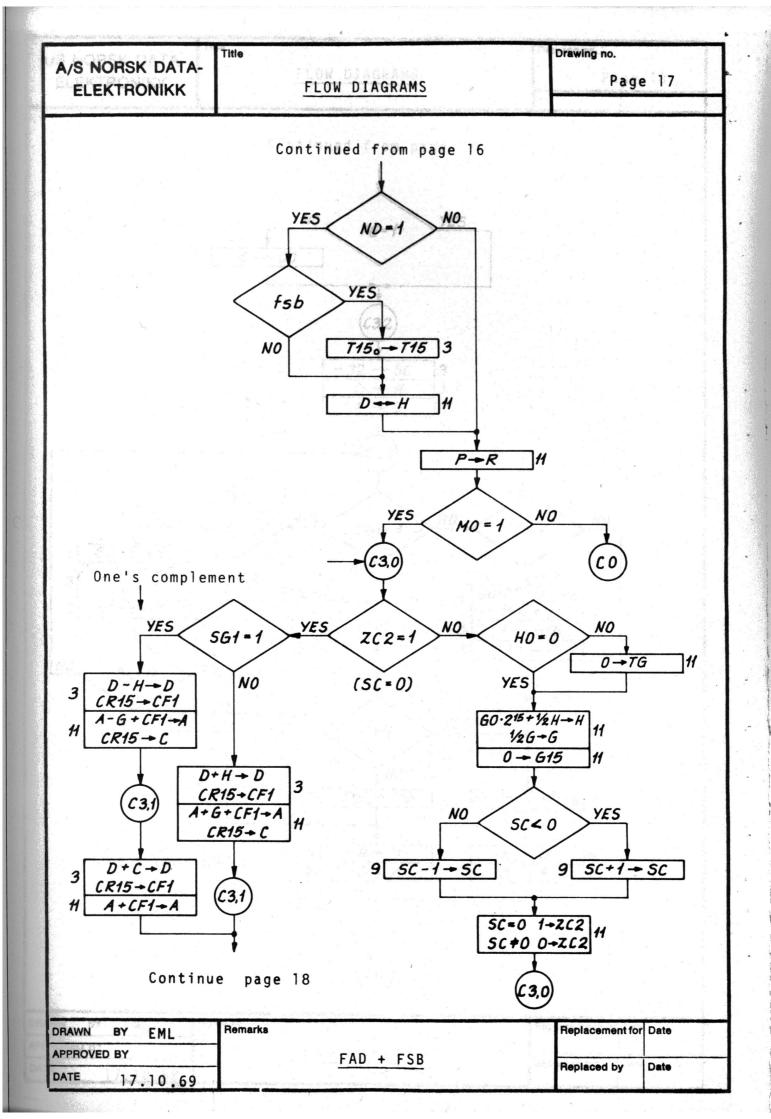

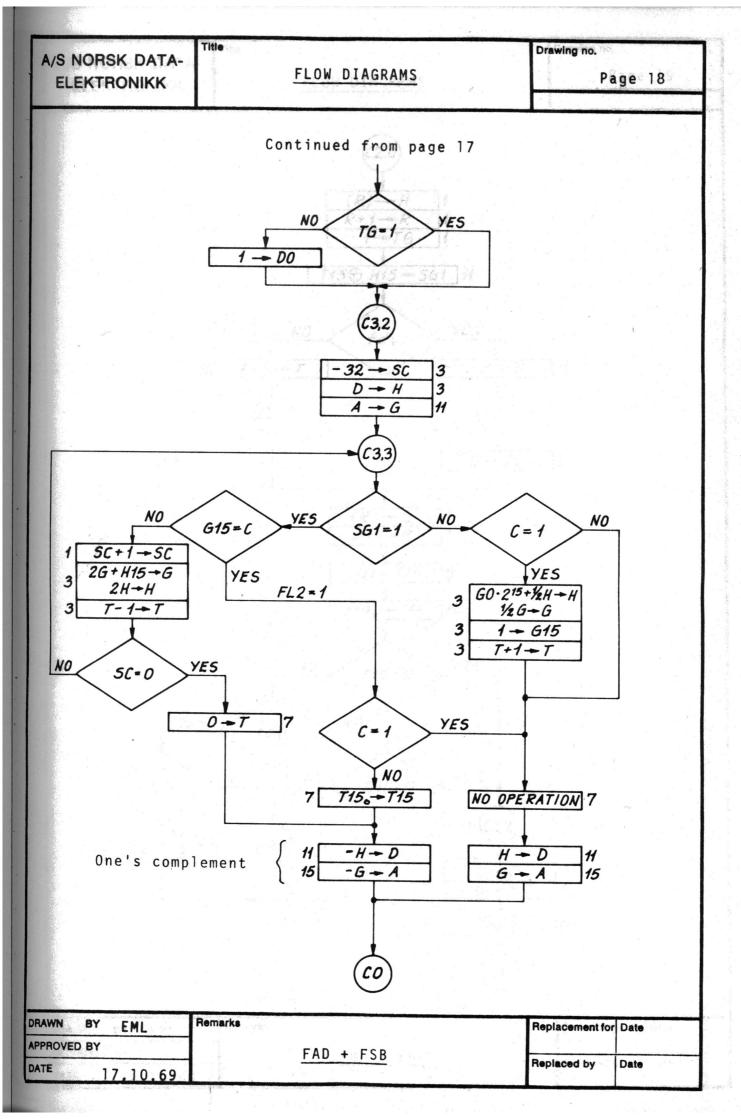

MO:Mantissa overlap ND:Negative differance Floating control 134

Continue page 17

$\emptyset_1 = S14_113_112_111_110_19_18_17_16_15_1 + S14_013_012_011_010_09_08_07_06_05_0$ ): (T - H) < 32

| DRAWN BY EML   | Remarks   | Replacement for | Date |

|----------------|-----------|-----------------|------|

| APPROVED BY    | FAD + FSB |                 |      |

| DATE: 17.10.69 |           | Replaced by     | Date |

FLOW DIAGRAMS

Drawing no.

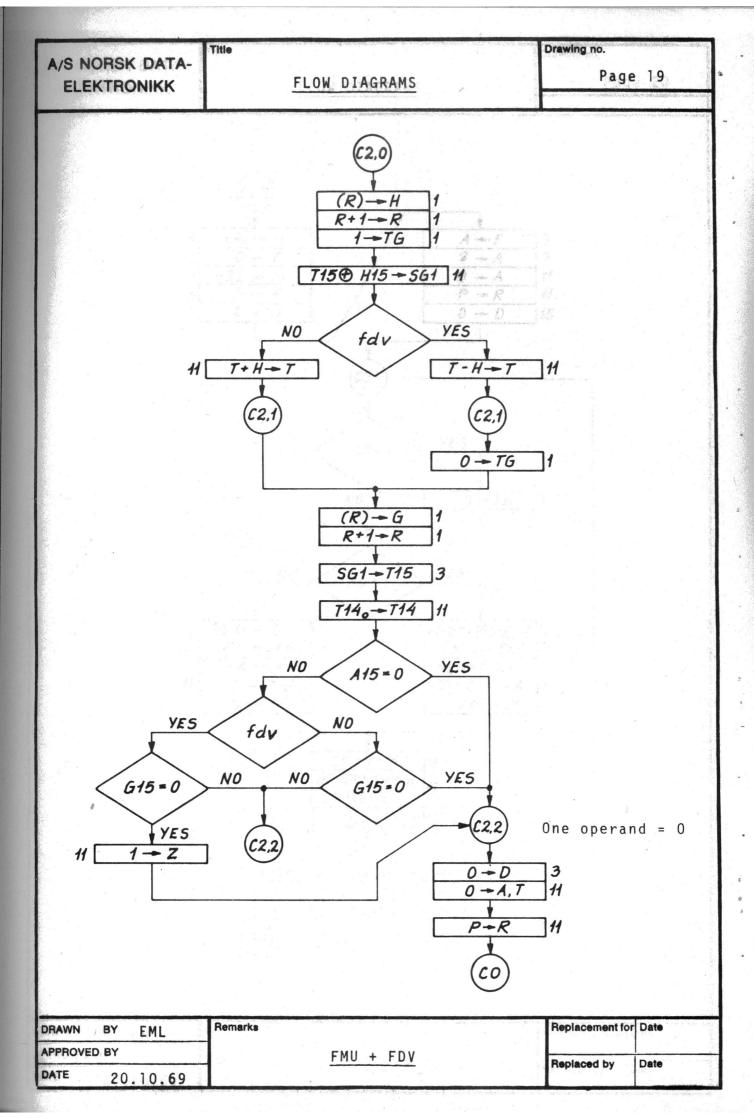

| DRAWN BY EML  | Remarks | Replacement for | Date |

|---------------|---------|-----------------|------|

| APPROVED BY   | F M U   |                 |      |

| DATE 20.10.69 |         | Replaced by     | Date |

Title

FLOW DIAGRAMS

Drawing no.

| DRAWN   | BY   | EML     | Remarks      | Replacement for | Date     |

|---------|------|---------|--------------|-----------------|----------|

| APPROVE | D BY |         | <u>F M U</u> |                 | <b>-</b> |

| DATE    | 2    | 1.10.69 |              | Replaced by     | Date     |